Тема 4. Организация памяти эвм

Лекция 11. Организация памяти

1. Сегментированная модель памяти.

2. Формирование физического адреса в реальном режиме.

3. Формирование физического адреса в защищенном режиме.

4. Пространство физической памяти

1. Сегментированная модель памяти

Физическая память, к которой процессор имеет доступ по шине адреса, называется оперативной памятью (или оперативным запоминающим устройством – ОЗУ). На самом нижнем уровне память компьютера можно рассматривать как массив битов. Один бит может хранить значение 0 или 1. Для физической реализации битов и работы с ними идеально подходят логические схемы. Но процессору неудобно работать с памятью на уровне битов, поэтому реально ОЗУ организовано как последовательность ячеек – байтов. Каждому байту соответствует свой уникальный адрес (его номер), называемый физическим. Диапазон значений физических адресов зависит от разрядности шины адреса процессора. Для i486 и Pentium он находится в пределах от 0 до 232- 1 (4 Гбайт). Для процессоров Pentium Pro/II/III/IV этот диапазон шире - от 0 до 236 - 1 (64 Гбайт).

Механизм управления памятью полностью аппаратный. Это означает, что программа не может сама сформировать физический адрес памяти на адресной шине. Этот механизм позволяет обеспечить:

компактность хранения адреса в машинной команде;

гибкость механизма адресации;

защиту адресных пространств задач в многозадачной системе;

поддержку виртуальной памяти.

Процессор аппаратно поддерживает две модели использования оперативной памяти.

В сегментированной модели программе выделяются непрерывные области памяти (сегменты), а сама программа может обращаться только к данным, которые находятся в этих сегментах.

Страничную модель можно рассматривать как надстройку над сегментированной моделью. В случае использования этой модели оперативная память рассматривается как совокупность блоков фиксированного размера (4 Кбайт и более). Основное применение этой модели связано с организацией виртуальной памяти, что позволяет операционной системе использовать для работы программ пространство памяти большее, чем объем физической памяти. Для процессоров i486 и Pentium размер возможной виртуальной памяти может достигать 4 Тбайт.

Сегментация – механизм адресации, обеспечивающий существование нескольких независимых адресных пространств как в пределах одной задачи, так и в системе в целом для защиты задач от взаимного влияния. В основе механизма сегментации лежит понятие сегмента, который представляет собой независимый поддерживаемый на аппаратном уровне блок памяти.

Когда мы рассматривали сегментные регистры, то отмечали, что для процессоров Intel, начиная с i8086, принят особый подход к управлению памятью. Каждая программа в общем случае может состоять из любого количества сегментов, но непосредственный доступ она имеет только к трем основным сегментам (кода, данных и стека), а также к дополнительным сегментам данных числом от одного до трех. Программа никогда не знает, по каким физическим адресам будут размещены ее сегменты. Этим занимается операционная система. Операционная система размещает сегменты программы в оперативной памяти по определенным физическим адресам, после чего помещает значения этих адресов в определенные места. Куда именно, зависит от режима работы процессора. Так, в реальном режиме эти адреса помещаются непосредственно в соответствующие сегментные регистры, а в защищенном режиме они размещаются в элементы специальной системной дескрипторной таблицы. Внутри сегмента программа обращается к адресам относительно начала сегмента линейно, то есть начиная с 0 и заканчивая адресом, равным размеру сегмента. Этот относительный адрес, или смещение, который процессор использует для доступа к данным внутри сегмента, называется эффективным.

Отличия моделей сегментированной организации памяти в различных режимах хорошо видны на схеме (рис. 1). Различают три основных модели сегментированной организации памяти:

сегментированная модель памяти реального режима;

сегментированная модель памяти защищенного режима;

сплошная модель памяти защищенного режима.

2. Формирование физического адреса в реальном режиме

Формирование физического адреса в реальном режиме происходит следующим образом. Под физическим адресом понимается адрес памяти, выдаваемый на шину адреса процессора. Другое название этого адреса - линейный адрес. Подобная двойственность в названии обусловлена наличием страничной модели организации оперативной памяти. Эти названия являются синонимами только при отключении страничного преобразования адреса (в реальном режиме страничная адресация всегда отключена). Страничная модель, является надстройкой над сегментированной моделью. В страничной модели линейный и физический адреса имеют разные значения.

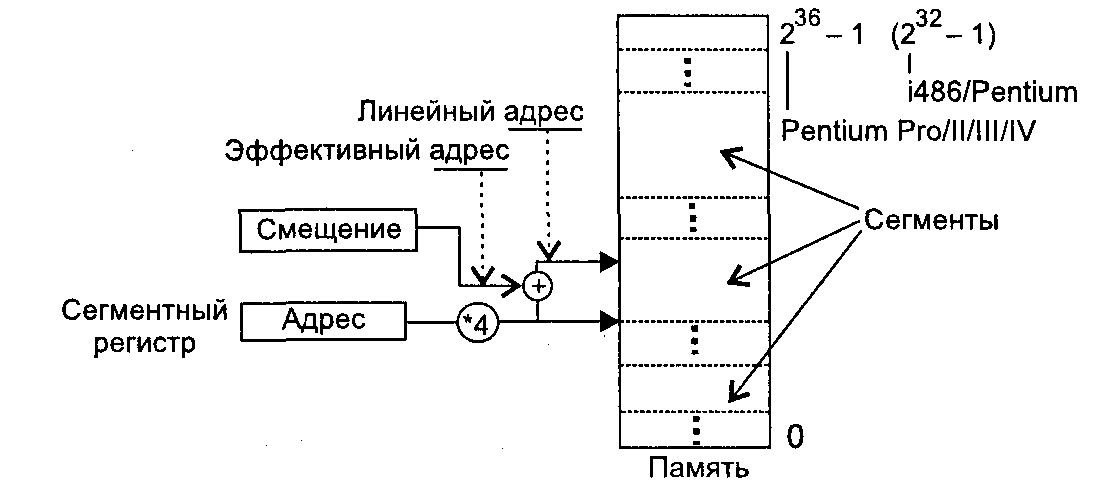

Характеристики механизма адресации физической памяти в реальном режиме (рис. 1):

диапазон изменения физического адреса – от 0 до 1 Мбайт. Эта величина определяется тем, что шина адреса i8086 имела 20 линий.

максимальный размер сегмента— 64 Кбайт. Это объясняется 16-разрядной архитектурой i8086. Нетрудно подсчитать, что максимальное значение, которое могут содержать 16-разрядные регистры, составляет 216 - 1, что применительно к памяти и определяет величину 64 Кбайт.

для обращения к конкретному физическому адресу оперативной памяти необходимо определить адрес начала сегмента (сегментную составляющую) и смещение внутри сегмента.

Рис. 1. Сегментированная модель памяти реального режима

Понятие адреса начала сегмента ввиду принципиальной важности требует дополнительного пояснения. Исходя из разрядности сегментных регистров, можно утверждать, что сегментная составляющая адреса (или база сегмента) представляет собой всего лишь 16-разрядное значение, помещенное в один из сегментных регистров. Максимальное значение, которое при этом получается, соответствует 216 - 1. Если так рассуждать, то получается, что адрес начала сегмента может быть только в диапазоне 0-64 Кбайт от начала оперативной памяти. Возникает вопрос, как адресовать остальную часть оперативной памяти вплоть до 1 Мбайт с учетом того, что размер самого сегмента не превышает 64 Кбайт. Дело в том, что в сегментном регистре содержатся только старшие 16 битов физического адреса начала сегмента. Недостающие младшие четыре бита 20-разрядного адреса получаются сдвигом значения в сегментном регистре влево на 4 разряда. Эта операция сдвига выполняется аппаратно и для программного обеспечения абсолютно прозрачна. Получившееся 20-разрядное значение и является настоящим физическим адресом, соответствующим началу сегмента. Что касается второго компонента (смещения), участвующего в образовании физического адреса некоторого объекта в памяти, то он представляет собой 16-разрядное значение. Это значение может содержаться явно в команде либо косвенно в одном из регистров общего назначения. В процессоре эти две составляющие складываются на аппаратном уровне, в результате получается физический адрес памяти размерностью 20 битов. Данный механизм образования физического адреса позволяет сделать программное обеспечение перемещаемым, то есть не зависящим от конкретных адресов загрузки его в оперативной памяти (рис. 2).

Рис. 2. Формирование физического адреса при обращении в памяти

На рисунке видно, как формируется некоторый целевой физический адрес: сегментная часть извлекается из одного из сегментных регистров, сдвигается на четыре разряда влево и суммируется со смещением. В свою очередь, видно, что значение смещения можно получить минимум из одного и максимум из трех источников: из значения смещения в самой машинной команде и/или из содержимого одного базового и/или одного индексного регистра. Количество источников, участвующих в формировании смещения, определяется кодированием конкретной машинной команды, и если таких источников несколько, то значения в них складываются. В заключение заметим, что не стоит волноваться из-за несоответствия размеров шины адреса процессора i486 или Pentium (32 бита) и 20-разрядного значения физического адреса реального режима. Пока процессор находится в реальном режиме, старшие 12 линий шины адреса попросту недоступны, хотя при определенных условиях и существует возможность работы с первыми 64 Кбайт оперативной памяти, лежащими сразу после первого мегабайта.

Недостатки такой организации памяти:

сегменты бесконтрольно размещаются в ОП с любого адреса, кратного 16 (так как содержимое сегментного регистра аппаратно смещается на 4 разряда), и, как следствие, программа может обращаться по любым адресам, в том числе и реально не существующим;

сегменты имеют максимальный размер 64 Кбайт;

сегменты могут перекрываться другими сегментами.

Желанием ввести в архитектуру средства, позволяющие избавиться от указанных недостатков, и обусловлено, в частности, появление защищенного режима, в котором работают все современные операционные системы, в том числе Windows и Linux.