Масленников Основы шемотехники електронных цепей

.pdf

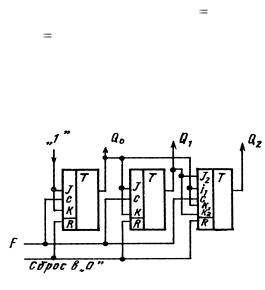

От этого недостатка свободны параллельные счетчики, иногда их называют синхронными. В синхронных счетчиках импульсы счета подаются одновременно на входы С всех разрядов. Управление переключением триггеров осуществляется по логическим J и К входам (рис. 6.15).

Для того, чтобы убедиться в более высоком быстродействии синхронного счетчика, рассмотрим процесс перехода синхронного и асинхронного счетчиков (см. рис. 6.14 и 6.15) из состояния «111» в состояние «000» при поступлении очередного счетного импульса по входу F. Переключение последнего триггера асинхронного счетчика произойдет через tз.общ 3tз.тр . Для синхронного счетчика

tз.общ tз.тр , так как во всех разрядах на входах J и К уже были выставлены «1» (код на выходе до прихода импульса был «111») и переключаются три триггера одновременно. Как видим, выигрыш в быстродействии составит для трехразрядного счетчика – 3. В общем случае – N, N – количество разрядов.

Рис. 6.15. Трехразрядный синхронный счетчик

Однако благодаря своей простоте асинхронные (последовательные) счетчики нашли широкое применение при построении цифровой аппаратуры.

Для создания многоразрядных счетчиков часто используется па- раллельно-последовательное построение, которое осуществляется путем последовательного соединение трехили четырехразрядных счетчиков. Такие счетчики имеют более высокое быстродействие, чем последовательные и требуют меньше аппаратурных затрат, чем параллельные счетчики.

111

Для получения модулей счета M 2m используются счетчики с

модулем счета M 2m путем исключения избыточных устойчивых состояний. Исключение этих состояний осуществляется введением обратных связей, а также путем включения дополнительных логических элементов. Например, десятичный счетчик (М = 10) можно получить из последовательного (асинхронного) четырехразрядного счетчика с М = 16, если при поступлении 10-го импульса, когда установится состояние выходов Q3Q2Q1Q0 1010, подать на общий

вход сброса сигнал R = 1. Этот сигнал можно получить, используя управляющую комбинационную схему, на выходе которой образуется «1» только в том случае, если на входе сигнал 1010. Аналогично можно построить и счетчики с другим модулем счета.

Как видно из табл. 6.1, с помощью трехразрядного двоичного счетчика можно сосчитать до 7, с помощью четырехразрядного – до 15. Следовательно, для счета натуральных десятичных чисел в двоичном коде для каждого десятичного разряда необходим четырехразрядный двоичный счетчик, вырабатывающий двоичный эквивалент счетной декады. Эта счетная декада отличается от обычного четырехразрядного двоичного счетчика тем, что на каждый 10-й (а не 16-й) импульс счета она сбрасывается в нуль и появляется сигнал переноса для запуска счетной декады следующего, более старшего десятичного разряда.

Такие счетчики носят название двоично-десятичных. Они значительно проще чисто двоичных в тех случаях, когда результат счета необходимо представить в десятичной форме, потому что каждую цифру удобно дешифрировать в цифру десятичного разряда. В данной работе будем исследовать именно такой счетчик.

Промышленностью выпускается большая номенклатура счетчи-

ков. Это 155ИЕ1, ИЕ6, ИЕ7, ИЕ16; 176ИЕ1, ИЕ2, ИЕ3, ИЕ4, ИЕ5,

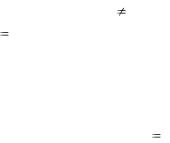

ИЕ8, ИЕ9 и т.д. Схема двоично-десятичного счетчика 155ИЕ2 представлена на рис. 6.16.

Дешифраторы являются представителями комбинационных схем и широко используются для преобразования одной формы представления цифровой информации в другую. Условное изображение дешифратора представлено на рис. 6.17. Он имеет m входов и n выходов и выполняет следующую функцию: каждому слову (m – разрядному коду), т.е. комбинации единиц и нулей на входах,

112

соответствует сигнал «0» или «1» на одном или нескольких определенных выходах. Для дешифратора

число выходов n 2m. При n 2m дешифратор называется полным,

при n 2m – неполным. В составе современных серий микросхем выпускается, например, неполный дешифратор «из 4 в 10», который используется в устройствах вывода информации, чтобы обеспечить десятичную индикацию или печать десятичных чисел. В дешифраторе используются выходные элементы ТТЛ с открытым коллектором (см. рис.6.12, а), которые при логическом «0» на соответствующем выходе замыкают электрическую цепь, в которую включены индикаторные лампы или обмотки реле цифропечатающего устройства. Таким образом, дешифратор функционирует в соответствии с табл.6.2, где X1 , X 2 , X 3 , X 4 служат входными переменными.

Рис. 6.16. Условное обозначение микросхемы

155ИЕ2

Рис. 6.17. Условное изображение дешифратора

Таблица 6.2

Х1 |

Х2 |

Х3 |

Х4 |

Y0 |

Y1 |

Y2 |

Y3 |

Y4 |

Y5 |

Y6 |

Y7 |

Y8 |

Y9 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

0 |

113

Широкое распространение получили дешифраторы двоичнодесятичных кодов в семисегментный код, которые также выпускаются отечественной промышленностью в виде интегральных схем. Такие дешифраторы применяются в устройствах визуальной индикации десятичных цифр на световых табло (рис.6.18), использую-

щих светодиоды, индикаторы на жидких кристаллах, электролюминесцентные или электровакуумные приборы. Логическое функционирование такого дешифратора определяется табл.6.3, где обозначения выходных функций соответствуют семи сегментам А, В, С, D, Е, F, G. Так как на выходе дешифратора включаются элементы с открытым коллектором (см. рис. 6.12, а), то сегмент будет светиться при низком потенциале («0») на соответствующем выходе.

Таблица 6.3

Х1 |

Х2 |

Х3 |

Х4 |

А |

В |

С |

D |

Е |

F |

G |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

Помимо устройств вывода информации дешифраторы широко используются в устройствах управления, где они в соответствии с поступающим кодом образуют на выходах комбинацию управляющих сигналов для других блоков системы.

Дешифраторы строятся обычно на основе логических микросхем, выполняющих функции «И», «ИЛИ», «НЕ» и их комбинаций.

Дешифраторы выпускаются в виде интегральных микросхем с широкой номенклатурой. К ним относятся К155ИД1, 134ИД6,

К155ИД10, 514ИД2; К176ИД2, К176ИД3, К176ИЕ8 и др. Причем в

114

микросхеме К176ИЕ8 совмещены функции счетчика и дешифратора.

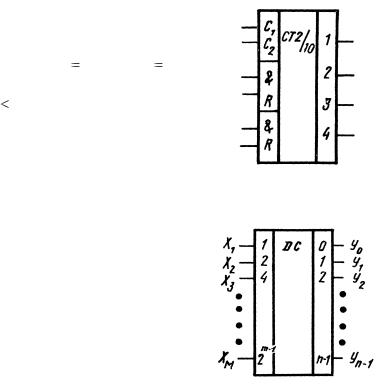

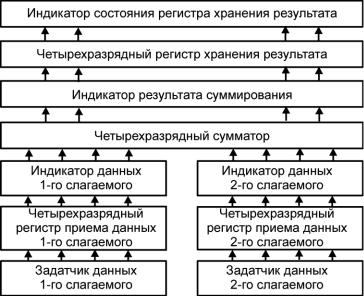

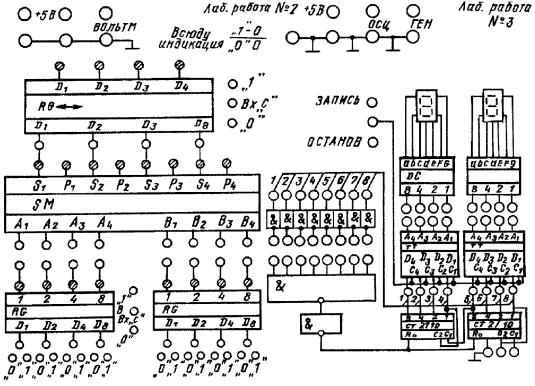

ОПИСАНИЕ ЛАБОРАТОРНОГО МАКЕТА

Структурная схема лабораторного макета представлена на рис.6.19 и 6.20, а вид лицевой панели на рис.6.21. Макет лабораторной работы состоит из трех четырехразрядных регистров К155ИР1, два из которых используются для приема данных 1-го и 2-го слагаемых, а третий – для хранения результатов суммирования; а также из четырехразрядного сумматора, который осуществляет непосредственное суммирование.

Рис. 6.19. Структурная схема лабораторного макета (левая часть рис.6.21)

На входы регистров слагаемых подаются произвольные четырехразрядные числа. Для этого с помощью перемычек клеммы «0» или «1», расположенные в нижней части макета, соединяются со входами регистров. Прием информации регистрами происходит только в том случае, когда на вход С подается высокий уровень потенциала (тумблеры Вх. «С» в верхнем положении). Заполненные регистрами

115

четырехразрядные числа с помощью перемычек подаются на вход четырехразрядного сумматора. Для того, чтобы была возможность визуальной регистрации значений переноса, сумматор построен на основе четырех микросхем К155ИМ1, т.е. на основе одноразрядных сумматоров. К выходу сумматора подсоединен четырехразрядный регистр, выполняющий функцию хранения результатов суммирования, которые фиксируются с помощью светодиодов.

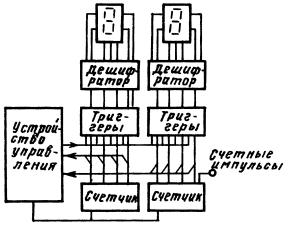

Структурная схема лабораторного макета, представляющая собой цифро-отображающее устройство, состоящее из двух десятичных разрядов, показана на рис. 6.20. Оно состоит из двух четырехразрядных двоичных счетчиков, двух счетверенных триггеров, двух дешифраторов и двух семисегментных индикаторов. В макет входит также устройство управления, позволяющее путем коммуникации устанавливать пределы счета. Это устройство включает в себя 8 двухвходовых элементов, выполняющих операцию «2И-НЕ» и один восьмивходовой элемент «8И-НЕ», а также схему задержки импульсов, которая позволяет согласовывать по времени подачу на входы счетчика и триггеров сигналов сброса и установки.

Рис. 6.20. Структурная схема лабораторного макета (правая часть рис. 6.21)

Работа макета осуществляется следующим образом. На вход двоично-десятичного четырехразрядного счетчика, принадлежащего к младшему десятичному разряду, подаются счетные импульсы.

116

117

Рис. 6.21. Вид лицевой панели лабораторного макета

После поступления 9-го счетного импульса на выходе счетчика формируется импульс, который, в свою очередь, является счетным для такого же счетчика, расположенного в старшем десятичном разряде. После заполнения обоих счетчиков до установленного заранее с помощью схемы коммутации предела показания счетчика переписываются (запоминаются) триггерами. Значение числа, которое запомнили триггеры, подается на входы дешифраторов, преобразующих входной четырехразрядный код в семисегментный. Выходы дешифраторов непосредственно связаны с семисегментными индикаторами. Таким образом, на индикаторах высвечивается число импульсов, поступивших на вход счетчика.

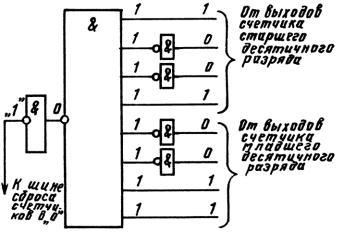

Рис. 6.22. Схема управления

При достижении показаний счетчика установленного предела в устройстве управления формируется импульс сброса, который подается на счетчик и устанавливает значение всех его разрядов в «нуль». Затем процесс повторяется.

Процесс установки любого заданного заранее предела счета удобно проследить на конкретном примере. Пусть необходимое предельное число сосчитанных импульсов составляет 93. Это значит, что счетчики должны быть сброшены в «нуль», когда показания счетчика младшего десятичного разряда станет равным –3, а

118

счетчик старшего десятичного разряда –9. Число 3 в двоичном коде представляется в виде –0011, число 9 –1001.

Согласно логике работы логического элемента «8И-НЕ» нулевое состояние на его выходе может быть только в том случае, когда на всех его 8 входах будет присутствовать логическая единица. Таким образом, задача состоит в том, чтобы с помощью логических элементов «И-НЕ» преобразовать выбранное число, представленное в двоичном коде, в восемь единиц. Эту операцию можно осуществить с помощью четырех элементов «И-НЕ», как представлено на рис.6.22. Аналогичным образом можно поступить для кодирования предела счета, выраженного любым двузначным числом.

В макете предусмотрена возможность соединения выходов счетчика непосредственно со входами дешифраторов, минуя триггеры.

ПОДГОТОВКА К РАБОТЕ

1.Внимательно ознакомиться с описанием лабораторной работы

иответить на все контрольные вопросы.

2.Произвести сложение двух пар произвольно выбранных четырехразрядных двоичных чисел. Получить значение суммы и переносов.

3.Выбрав два произвольных восьмиразрядных числа, произвести сдвиг вправо на 3 разряда и влево на 2 разряда.

4.Выбрать два произвольных двузначных числа и представить их в двоично-десятичной форме.

5.Составить схему кодирования сброса, аналогичную представленной на рис.6.22, но для выбранных чисел.

РАБОЧЕЕ ЗАДАНИЕ

1.Записать произвольную информацию в регистр приема данных 1-го слагаемого. Тоже самое – в регистр приема 2-го слагаемого.

2.Произвести сдвиг информации в регистрах на 1, 2, 3 и 4 разряда. Объяснить полученный результат.

3.Записать во входные регистры выбранные при подготовке к работе два четырехразрядных числа и подать их на сумматор. Запи-

119

сать значение суммы и переносов. Сравнить полученный результат с результатом, полученным при подготовке к работе. Записать полученную сумму в регистр хранения результата.

4.Произвести сложение двух четырехразрядных чисел без использования регистра. Сравнить с п.3. Объяснить полученный результат.

5.Произвести обнуление всех регистров.

6.Соединить в «кольцо» два четырехразрядных регистра, записать любой код, подать с внешнего генератора синхронизирующие импульсы. Наблюдать с помощью осциллографа процесс хранения записанного слова.

7.Собрать схему цифроотображающего устройства, не включая триггеры памяти.

8.Испытать собранную схему при подаче на вход счетчика счетных импульсов в однократном режиме.

9.Повторить п.8, но генератор счетных импульсов переключить

вавтоколебательный режим. Изменяя частоту поступления импульсов, определить при какой частоте еще имеется возможность наблюдать результат счета на светодиодных индикаторах.

10.Включить в собранную схему триггеры памяти. Подать на вход импульсы с частотой 5÷10 кГц. С помощью тумблера «Запись» запомнить число, которое в этот момент присутствует на выходах счетчика. Объяснить необходимость включения триггера памяти в цифроотображающее устройство.

11.Установить предел счета импульсов, равным одному из двух чисел, выбранных при подготовке к работе. Убедиться в правильности работы собранной схемы. То же самое проделать для второго числа.

12.Используя счетчик в качестве генератора случайных чисел, получить пять случайных чисел при установке предела счета, равным 36.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1.Что такое сумматор?

2.В чем отличие сумматора от полусумматора?

3.Что такое «перенос»? Приведите пример.

120