Н.А. Резниченко Исследование усилителей постоянного тока

.pdfМинистерство образования Российской Федерации Государственное учреждение

Кузбасский государственный технический университет Кафедра общей электротехники

ИССЛЕДОВАНИЕ УСИЛИТЕЛЕЙ ПОСТОЯННОГО ТОКА

Методические указания к лабораторной работе по дисциплине "Электротехника и электроника"

для студентов специальности 170100 "Горные машины и оборудование"

Составитель Н.А. Резниченко

Утверждены на заседании кафедры Протокол № 6 от 23.02.01

Рекомендованы к печати учебно-методической комиссией cпециальности 170100 Протокол № 5 от 2.04.01

Электронная копия находится в библиотеке главного корпуса ГУ КузГТУ

Кемерово 2001

ЦЕЛЬ РАБОТЫ

Изучение принципа работы, снятие и анализ характеристик и приобретение навыков балансировки дифференциального усилителя как основного усилителя в современных электронных устройствах.

КРАТКИЕ ТЕОРЕТИЧЕСКИЕ СВЕДЕНИЯ

При усилении сигналов очень низких частот (порядка долей герц) требуются усилители, имеющие равномерную амплитудно-частотную характеристику до самых низких частот. Такие усилители называют усилителями постоянного тока (УПТ). В многокаскадных УПТ для связи между каскадами не могут быть использованы реактивные элементы связи (конденсаторы, трансформаторы), поэтому для этой цели, как правило, служат резисторы. В области низких и средних частот ампли- тудно-частотная характеристика УПТ равномерна, в области высоких частот в УПТ начинают сказываться паразитные емкости усилительных каскадов, в результате чего появляются фазовые сдвиги и частотные искажения.

В УПТ возникают специфические трудности, связанные с отделением полезного сигнала от постоянных составляющих напряжения и тока, необходимых для работы транзисторов, используемых в усилителях.

Характеристики УПТ должны отвечать ряду требований:

если нет входного сигнала, не должно быть и выходного сигнала; при изменении знака входного сигнала должен изменять знак и

выходной сигнал; напряжение на нагрузочном устройстве должно быть пропорцио-

нально входному напряжению.

Для выполнения первого условия необходимо отделить полезный выходной сигнал от постоянных составляющих тока и напряжения транзистора, которое, как правило, производится компенсационным методом. Такие усилители подразделяются на усилители с одним и с двумя источниками питания, обладающие рядом недостатков.

Второе и третье требования в УПТ выполняются при работе усилителя класса А.

УПТ имеют специфический недостаток, затрудняющий усиление малых постоянных напряжений и токов, называемый дрейфом нуля.

2

Дрейф нуля заключается в том, что с течением времени могут изменяться токи транзисторов и напряжения на их электродах из-за нестабильности источников питания, “старения” транзисторов, изменения температуры окружающей среды. Эти изменения принципиально не отличаются от полезного сигнала. Выходное напряжение при дрейфе нуля состоит из двух составляющих: медленно изменяющегося напряжения, называемого медленным дрейфом и обусловленное в основном изменением характеристик транзисторов в течение длительного времени; быстрого дрейфа, определяемого колебаниями напряжения источника питания, температуры окружающей среды и другими внешними дестабилизирующими факторами.

Для борьбы с дрейфом нуля принимают целый ряд мер:

1)стабилизацию напряжения источников питания;

2)стабилизацию температурного режима;

3)тренировку транзисторов (искусственное старение);

4)использование дифференциальных (балансных) схем УПТ;

5)преобразование усиливаемого напряжения.

Балансные УПТ (рис.1) построены по принципу четырехплечего моста,

VT1 |

|

VT2 |

3

двумя плечами которого являются внутренние сопротивления транзисторов VT1 и VT2, а двумя другими - резисторы Rк1 и Rк2. К одной диа-

гонали моста подключено напряжение источника питания Eк, а к другой – внешняя нагрузка Rн. Входной сигнал постоянного или медленно изменяющегося тока прикладывается к базам обоих транзисторов (симметричный вход). Если плечи моста симметричны (транзисторы

идентичны, а Rк1 = Rк2) и Uвх = 0, то начальные токи покоя транзисто-

ров одинаковы. При этом напряжения на коллекторах Uк1 и Uк2 относительно заземленной точки схемы также равны, поэтому разность по-

тенциалов между коллекторами (на нагрузке Rн) равна нулю. Изменение напряжения питания, температуры или воздействие какого–либо другого дестабилизирующего фактора вызывает равные приращения начальных токов транзисторов, что обусловливает равные приращения

напряжений на коллекторах ∆Uк1=∆Uк2. Однако баланс моста при этом сохраняется и напряжение на нагрузке (напряжение дрейфа) равно нулю.

При наличии входного сигнала (Uвх > 0) приращения коллекторных токов, а следовательно, и напряжений на коллекторах будут равны, но противоположны по знаку, что приводит к разбалансу моста и

появлению на нагрузке разности потенциалов (Uвых ≠ 0), за счет кото-

рой в резисторе Rн проходит ток усиленного сигнала.

Полной симметрии плеч в реальной схеме достичь невозможно, что обусловливает наличие небольшого напряжения дрейфа. Для по-

вышения стабильности балансного УПТ вводят сопротивление Rо, с помощью которого поддерживается большее постоянство потенциалов эмиттеров при изменении токов транзисторов. Сопротивление этого резистора определяется соотношением

Rо = ÄU бmax ,

Iоэ

где ∆U бmax − максимальное изменение потенциала базы, обусловленное дрейфом или входным сигналом усилителя; Iоэ − ток покоя тран-

зистора.

Вместо отдельных резисторов в цепях эмиттеров транзисторов на

практике применяют один общий резистор Rэ. Он обусловливает отрицательную обратную связь лишь по токам покоя обоих транзисторов,

4

что выгодно с точки зрения стабилизации параметров УПТ и снижения дрейфа нуля. Так как при воздействии входного сигнала приращения

эмиттерных токов, проходящих через резистор Rэ, равны, но противоположны по направлению, т.е.

ÄIЭ1 = −ÄIЭ2 ,

то отрицательная обратная связь по току полезного сигнала поддерживается лишь небольшим сопротивлением связи

Rо = (0,01 − 0,05) Rэ.

Коэффициент усиления балансного УПТ равен коэффициенту усиления однокаскадного усилителя с ОЭ (одного плеча УПТ):

Kv =h21ЭRкн/Rвх,

|

|

|

R |

R |

|

|

|

R |

|

|

где |

R |

= |

к |

н |

/ R |

+ |

н |

|

; |

|

|

|

|

||||||||

|

кн |

2 |

|

к |

|

2 |

|

|

||

|

|

|

|

|

|

|

||||

RК1=RК2 =RК .

Дифференциальный усилитель представляет собой балансный УПТ с источником стабильного тока в цепи эмиттера, значение которого определяется дополнительным источником питания и резистором в эмиттерной цепи (рис.2). В частном случае напряжение входного сигнала может быть подано лишь на один вход ( EВХ1 =0 или

5

EВХ2 =0 ). Напряжение выходного сигнала снимается либо между кол-

лекторами транзисторов (симметричный выход), либо с коллектора одного из транзисторов относительно общего провода (несимметричный выход).

Сопротивление резистора Rэ должно значительно превышать внутреннее сопротивление усилителя со стороны его входа с тем, чтобы стабильный ток

Iо=(E−UбЭ) / Rэ

не зависел от напряжения на входе дифференциального усилителя и сохранял постоянное значение даже при наличии короткого замыкания в цепи нагрузки источника тока. Параметры дифференциального усилителя существенно зависят от тока Iо.

Важнейшая особенность дифференциального усилителя − способность высокого усиления разностного сигнала Eвх1 −Eвх2 (когда

входные сигналы переменного тока противофазны или разнополярны в случае сигналов постоянного тока) и значительного ослабления суммарного входного сигнала Eвх1 +Eвх2 (дрейфа нуля УПТ).

При симметричных плечах схемы и отсутствии входных сигналов дифференциальный усилитель сбалансирован и напряжение между

коллекторами (на выходе) равно нулю. Поскольку ток Iо делится пополам между плечами, потенциалы коллекторов обоих транзисторов одинаковы (рис.3):

Uко = Uвых1 = Uвых2 = Eк − Iо Rк/2.

Если в момент времени t1 на вход транзистора VT1 поступил по-

ложительный сигнал при Eвх2 = 0, то на выходе левого плеча схемы (см. рис.2), представляющего собой усилительный каскад с ОЭ, поя-

вится усиленный сигнал Uвых1 противоположной полярности (инвертированный сигнал, как в схеме с ОЭ). Одновременно на эмиттерном резисторе

Rэ′ = Rэ Rвх об / (Rэ + Rвх об)

появится положительный импульс Uэ, равный по амплитуде входному импульсу Eвх1 > 0. В приведенной формуле Rвх об является входным

сопротивлением транзистора VT2 по эмиттерному входу. Импульс Uэ поступает на эмиттер транзистора VT2, вызывая появление на коллекторе усиленного импульса также положительной полярности (сдвиг по

6

фазе отсутствует, как в схеме с ОБ) с амплитудой Uвых2 ≈ Uвых1. Следовательно, выходной сигнал с напряжением Uвых2 не инвертирован по отношению к входному сигналу.

При увеличении амплитуды входного сигнала Eвх1 ток транзисто-

ра VT1 увеличивается, а напряжение на его коллекторе Uвых1 снижается, и, наоборот, ток транзистора VT2 уменьшается, что сопровождается

ростом напряжения Uвых2 (участок t1 − t2 на потенциальной диаграмме сигналов рис.3). В момент времени t2 ток транзистора VT1 достигает максимально возможного значения Iо, а ток транзистора VT2 равен ну-

лю. При этом разность выходных сигналов Uвых2−Uвых1=IоRк. Описанный процесс справедлив, если между входами прикладывается диффе-

ренциальный сигнал (разностный или разнополярный). При наличии синфазного входного сигнала

Eсф = Eвх1 + Eвх2

(оба входа дифференциального усилителя соединены) и в случае иде-

ального источника тока (Rэ → ∞) реакция усилителя на выходе отсутствует. Поскольку в реальном дифференциальном усилителе резистор

Rэ имеет конечное значение сопротивления, при воздействии синфаз-

7

ного сигнала на выходе усилителя появится небольшое напряжение

разбаланса ∆Eсф, которое складывается с полезным сигналом, обусловливая сигнал ошибки. Поэтому дифференциальный усилитель будет тем качественней, чем меньший разностный входной сигнал может быть им различим на фоне большого синфазного сигнала, обычно вызванного влиянием дестабилизирующих факторов.

Если на вход дифференциального усилителя поступает разност-

ный сигнал Eвх1 = − Eвх2 = Eвх, то дифференциальный коэффициент усиления

Kд = (Uвых2 − Uвых1)/Eвх.

При синфазном входном сигнале Eвх1 = Eвх2 = Eсф коэффициент передачи синфазного напряжения, характеризующий степень ослабления синфазного сигнала:

Kсф = ∆Uвых.сф/Eсф,

где ∆Uвых.сф − приращение выходного синфазного напряжения на любом выходе схемы.

С учетом идентичности параметров транзистора

Kос.сф = Kд/Kсф = (Rвх.оэ + 2h21э Rэ)/Rвх.оэ,

где Rвх.оэ составляет примерно половину сопротивления схемы с ОЭ, определяемого по формуле

Rвх = rб + (rэ +Rэ)(1 + h21э),

и характеризует способность дифференциального усилителя выделять полезный сигнал на фоне помехи. В пределе Kос.сф может достигать значения 2h21э Rэ/Rвх.оэ, что подчеркивает важность выбора больших номиналов Rэ для подавления синфазного тока.

ОПИСАНИЕ ЛАБОРАТОРНОГО СТЕНДА

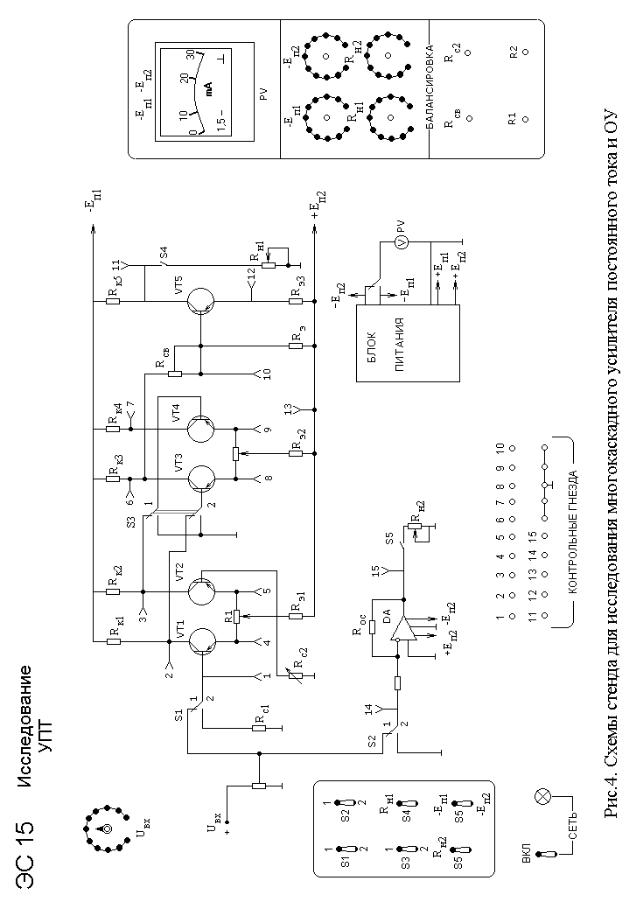

Для выполнения лабораторной работы служит переносной стенд (рис.4), на панели которого показаны схемы многокаскадного усилителя постоянного тока (УПТ) на транзисторах и на основе микросхемы, вольтметр для регистрации показаний напряжения источников питания, переключатели для коммутации соответствующих

8

9

режимов работы УПТ, сборки различных схем, регулировочные резисторы для балансировки, контрольные гнезда для подключения приборов и осциллографа с целью визуального наблюдения за характером изменения сигналов.

Первый каскад на транзисторах VT1 и VT2 является симметричным параллельно − балансным УПТ, второй (на транзисторах VT3, VT4) − несимметричным. Третий каскад выполнен на транзисторе VT5.

Одной из важных характеристик дифференциального усилителя является амплитудная характеристика, представляющая зависимость

Uвых = f(Uвх) (рис.5). Для первого каскада УПТ (см. рис.4) при подключении к точке 1 положительного полюса источника входного сигнала, а

к базе VT2 − отрицательного, ток будет проходить по цепи: точка 1, база − эмиттер VT1, R1, эмиттер − база VT2. Этим током транзистор VT1 будет закрываться и отрицательное напряжение на его коллекторе начнет расти, а транзистор VT2 будет открываться и отрицательное напряжение на его коллекторе будет уменьшаться. Следовательно, вольтметр для измерения выходного напряжения при данной полярности входного напряжения следует подключить плюсом к точке 3, а минусом − к

точке 2.

При некотором входном сигнале транзистор VT1 начнет закрываться, а транзистор VT2 окажется в режиме насыщения, т.е. прекратится воздействие входного сигнала на каскад УПТ. Этому состоянию каскада соответствуют

напряжения +Uвых.max и

−Uвых.max (см. рис.5),

ограничивающие линейный участок амплитудной характеристики, в

пределах которого коэффициент усиления напряжения постоянен, т.е.