KT-p22

.pdfАртура Рока основали фирму Intel (название образовано от Integral Electronic). Первой продукцией фирмы были микросхемы оперативной памяти. При выполнении заказа японской фирмы Busicom у сотрудника Теда Хоффа возникла идея создания универсальной интегральной микросхемы, успешную разработку которой возглавил Федерико Феджин. Результатом стало появление первого микропроцессора: Intel 4004.

AMD

Ещё в мае 1969 года бывший директор отдела маркетинга Fairchild Semiconductor Джерри Сандерс и несколько единомышленников основали фирму Advanced Micro Devices (AMD), которая специализировалась на производстве микроэлектронных устройств. Компания добилась успеха и уже через пять лет обладала внушительным производством. Позже,в 1982 году на основе лицензионного соглашения с фирмой Intel, AMD начинает производство клонов процессоров x86. Но компания не ограничилась простым клонированием и в 1991 году создала свой вариант Intel 386™. С тех пор AMD становится самым известным конкурентом Intel в производстве процессоров x86...

Cyrix

В 1988 году Джерри Роджерс (Jerry Rogers), один из самых перспективных инженеров США и ещё несколько бывших сотрудников Texas Instruments (Том Брайтман) организовали фирму Cyrix, которая начала свою деятельность с производства высокопроизводительных математических сопроцессоров для 286 и 386 систем. Отличительной чертой Cyrix было то,что фирма всегда была производителем,не имеющим своих собственных заводов по производству процессоров: вся продукция производилась по контрактам на заводах Texas Instruments, SGS Thompson и позднее IBM Microelectronics. Кроме того,Cyrix в производстве своих процессоров использовал только свои собственные разработки и никогда не пользовался лицензионными соглашениями с Intel. Тем не менее,со стороны Intel постоянно выдвигались обвинения о нарушении патентов в процессорах Cx486. Небольшая команда разработчиков Cyrix (до 30 человек) смогла составить реальную и успешную конкуренцию Intel и AMD, и даже обвинила Intel в незаконном использовании технологий переименования регистров

и энергосбережения,впервые реализованных в проекте M1,которые были применены в процессорах Intel Pentium Pro. Результатом долгих судебных разбирательств стало кросс-лицензионное соглашение между Intel и Cyrix, которое открывало совместный доступ к патентам друг друга.

VIA

41

Transmeta

NexGen Microsystems

Основанная в 1984 году в Милпитасе (Калифорния), фирма NexGen Microsystems была мало кому известна,даже специалистам. Несмотря на то, что у фирмы имели собственные разработки процессоров класса 386 и 486, шансов на успех у неё не было,так как они появились слишком поздно,да и рынок был давно поделен. Поэтому основные усилия были сосредоточены на разработке процессора следующего поколения. В 1994 году на CeBIT’94 был представлен процессор собственной разработки,над которым NexGen работала почти пять лет. В 1994 году NexGen Microsystems, не имеющая собственной производственной базы,и IBM Microelectronics, заключили соглашение,по которому процессоры Nx586 и производились на заводах IBM. В то время,когда фирма AMD запаздывала с разработкой собственного процессора пятого поколения а у NexGen был готовый продукт,но не было завода,произошло слияние AMD и NexGen, что имело огромное значение на дальнейшее развитие рынков процессоров.

Centaur Technology

Centaur Technology была основана в 1995 и являлась подразделением компании Integrated Device Technology (IDT)с небольшой командой инженеров,которые могли спроектировать микропроцессор x86 для компьютеров начального уровня. Через шесть лет,Centaur Technology преуспел,разрабатывая самые маленькие в мире,недорогие и конкурентоспособные x86 процессоры,посредством гибкой политики при разработке и производстве процессоров.

Rise Technology

Rise Technology — молодая американская компания,созданная специально для разработки х8б-совместимых процессоров для настольных компьютеров и ноутбуков. На сегодняшний день эта компания производит достаточно слабые процессоры,составляющие конкуренцию лишь поздним версиям Pentium ММХ,но обладаюточень низкой ценой,малым энергопотреблением и сочетают и себе ряд перспективных технологических решений.

1.2.4. Поколения процессоров

Первые микропроцессоры

Intel 4004. Объявлен: 15 ноября 1971 г. Тактовая частота: 108 килогерц,0,06 млн операций в секунду. Количество транзисторов: 2300 (10

мкм). Ширина полосы пропускания шины: 4 бит. Адресуемая память: 640

42

байт. Применение: калькуляторы Busicom, первая компьютерная микросхема, арифметические вычисления.

Intel 8008. Объявлен: апрель 1972 (разрабатывался одновременно с процессором 4004). Тактовая частота: 200 килогерц,0,06 млн операций в секунду. Количество транзисторов: 3500 (10 мкм). Ширина полосы пропускания шины: 8 бит. Адресуемая память: 16 Kбайт. Применение: терминалы ввода/вывода, калькуляторы общего назначения, автоматы бутылочного разлива,обработка данных и текста.

Intel 8080. Объявлен: апрель 1974 г. Тактовая частота: 2 МГц,0,64 млн операций в секунду. Количество транзисторов: 6000 (6 мкм). Ширина полосы пропускания шины: 8 бит. Адресуемая память: 64 Kбайт. Применение: устройства управления уличным освещением,компьютеры Altair (первые ПК). По сравнению с процессором 8008, производительность возросла в десять раз,а количество микросхем поддержки уменьшилось с 20-ти до шести.

Intel 8085. Объявлен: март 1976 г. Тактовая частота: 5 МГц,0,37 млн операций в секунду. Количество транзисторов: 6500 (3 мкм). Ширина полосы пропускания шины: 8 бит. Применение: весы Toledo, электронное взвешивание и вычисление цены товара,высокий уровень интеграции,впервые применен единый 5-вольтовый источник питания (ранее - 12 вольт).

Первое поколение

Общая характеристика. Первое поколение задали архитектурную основу — набор неравноправных 16-разрядных регистров, сегментную систему адресации памяти в пределах 1 Мбайт с большим разнообразием режимов,систему команд,систему прерываний и некоторые другие черты.

В процессорах применялась “малая” конвейеризация: пока одни узлы выполняли текущую инструкцию,блок предварительной выборки выбирал из памяти следующую. На выполнение каждой инструкции уходило в среднем по 12 тактов процессорного ядра.

Процессоры Intel Процессоры AMD

Второе поколение

Общая характеристика. Второе поколение привнесло в семейство защищенный режим. Производительность повысилась не только за счет роста тактовой частоты,но и за счет значительного усовершенствования

конвейера. Здесь на выполнении инструкции уходило в среднем по 4,5 такта. Во втором поколении появились новые инструкции: системные (для обслуживания механизмов защищенного режима) и несколько прикладных (в том числе блочный ввод-вывод — основа для программного обмена с портами PIO).

Процессоры Intel Процессоры AMD

43

Третье поколение

Общая характеристика. Третье поколение ознаменовалось переходом к 32-разрядной архитектуре. Кроме расширения диапазона непосредственно представляемых величин (16 бит отображают целые числа в диапазоне 0–65535 или –3276...+32767, 32 бита — более чем 4 млрд), увеличился и объем адресуемой памяти: до 4 Гбайт реальной, 64 Тбайт виртуальной). Для этого почти все программно-доступные регистры были расширены и получили в названии приставку “E” (EAX, EBX...). В систему команд ввели возможность переключения разрядности адресации и данных. Защищенный режим был несколько усовершенствован,но оставлена и обратная совместимость с 286. На таком процессоре стала “расцветать” система MS Windows — сначала оболочка,а потом и операционная система. В плане организации исполнения инструкций существенных изменений, повлекших за собой сокращение числа тактов на инструкцию,не произошло

— те же средние 4,5 такта,но частота уже достигла 40 МГц.

Процессоры Intel

Четвертое поколение

Общая характеристика. Четвертое поколение в видимую архитектурную модель больших изменений не внесло,но зато принят ряд мер для повышения производительности. В этих процессорах значительно усложнен исполнительный конвейер — основные операции выполняет RISC-ядро, “задания” для которого готовят из входных CISC-инструкций x86. Этот конвейер стал способным выдавать очередные инструкции в среднем за каждые два такта. Конечно,каждая инструкция проходит черезвесь конвейер

процессора за гораздо большее количество тактов,но темп выполнения в потоке именно таков. Производительность конвейера процессора оторвалась от возможностей доставки инструкций и данных из оперативной памяти,и прямо в процессор ввели быстродействующий первичный кэш объемом 8-16 Кбайт. В этом же поколении отказались от внешнего сопроцессора: теперь он либо на одном кристалле с центральным (называется FPU), либо его нет вообще. По сравнению с предыдущим поколением и сопроцессор стал работать значительно эффективнее. А тактовая частота в этом поколении достигла 133 МГц.

Процессоры Intel Процессоры AMD Процессоры IBM Процессоры Cyrix

Пятое поколене

Общая характеристика. Пятое поколение привнесли суперскалярную архитектуру. Суперскалярность означает наличие более, чем одного

44

конвейера. У процессоров пятого поколения после блоков предварительной выборки и первой стадии декодирования инструкций имеется два конвейе- ра,U-конвейер и V-конвейер. Каждый из этих конвейеров имеет ступени окончательного декодирования, исполнения инструкций и буфер записи результатов. U-конвейер “умеет” все,у V-конвейера возможности немного скромнее. Конвейеризирован и блок FPU. Процессор с такой архитектурой может одновременно “выпускать” до двух выполненных инструкций, но в среднем получается 1 такт на инструкцию. Не все инструкции могут выполняться парно,эффективность использования конвейеров (коэффициент их загрузки или простоя) зависит от программного кода — есть широкие возможности оптимизации. В процессорах применяется блок предсказания ветвлений.

Для быстрого снабжения конвейеров инструкциями и данными из памяти шина данных процессоров имеет разрядность 64 бит, из-за чего поначалу их даже ошибочно называли 64-разрядными процессорами. На закате этого поколения появилось расширение MMX, новизна которого заключается в принципе SIMD: одна инструкция выполняет действия сразу над несколькими (2,4 или 8) комплектами операндов. В MMX появился и новый тип арифметики — с насыщением (saturated): если результат операции не умещается в разрядной сетке,то вместо переполнения (антипереполнения) устанавливается максимально (минимально) возможное значение числа.

Процессоры Intel Процессоры AMD Процессоры IBM Процессоры Cyrix

Шестое поколение

Общая характеристика. Наличие двойной независимой шины у Intel является одним из свойств шестого поколения. Системная шина при этом имеет протокол, принципиально отличающийся от протокола шины процессоров Pentium.

Pentium Pro имеет два конвейера по 12 ступеней каждый. Исполнительная часть процессора состоит из четырех основных блоков: выборки и декодирования,выполнения,завершения и накопителя (буфера для инструкций). Все инструкции в накопителе имеют определенный статус: «может быть выполнена», «ожидает данные», «выполнена» и т. д. Первый блок содержит три декодера,которые переводят обычные х86 инструкции в более простой микрокод. Каждая инструкция микрокода получает свой статус и отправляется в накопитель. Блок выполнения считывает микрокод из накопителя, ориентируясь по статусу,и выполняет его. Выполнение может происходить и не в порядке очередности,при этом выполненные инструкции снова попадают

в накопитель,но уже со статусом «выполнена». Процессор одновременно может оперировать максимум с пятью инструкциями,но обычно этот пока-

45

затель равен трем. Блок завершения выбирает выполненные инструкции и удаляет их из накопителя уже в порядке очередности. Процессор имеет встроенный блок предсказания переходов с возможностью предварительного исполнения. Кэш-память разделена на память данных (8 Кбайт) и память инструкций (8 Кбайт). Кроме всего этого,процессор имеет еще одно нововведение,которым не может похвастать больше никто: встроенная кэшпамять второго уровня размером 256 или 512 Кбайт. Данная кэш-память работает на частоте процессора,что приводит к значительному повышению быстродействия. Это позволяет создавать и многопроцессорные системы. Именно на использование в многопроцессорных серверных системах и был рассчитан Pentium Pro, последняя модификация которого имеет кэш-память второго уровня 1 Мбайт.

Pentium III, Celeron и Xeon. Его лейтмотивом является динамическое исполнение,под которым понимается исполнение инструкций не в том порядке (out of order), как это предполагается программным кодом,а в том,как “удобно” процессору. Инструкции,поступающие на конвейер,разбиваются на простейшие микрооперации µ-ops, которые далее выполняются суперскалярным процессорным ядром в порядке,удобном процессору. Ядро процессора содержит несколько конвейеров,к которым подключаются исполнительные устройства целочисленных вычислений,обращений к памяти,предсказания переходов и вычислений с плавающей точкой. Несколько различных исполнительных устройств могут объединяться на одном конвейере. Результаты “беспорядочно” выполненных микроопераций собираются в реупорядочивающем буфере и в корректном порядке записываются в память (и порты ввода-вывода). Для того,чтобы можно было одновременно выполнять разные инструкции с одними и теми же программно-адресуемыми регистрами, внутри процессора выполняется аппаратное переименование регистров (их у процессора больше,чем доступных по программной модели). Конечно,при этом учитывается и связь по данным,которая сковывает “беспорядочные” параллельные исполнения,даже пользуясь дополнительными регистрами. В процессорах 6-го поколения используется исполнение по предположению, называемое также спекулятивным (speculative execution): процессор пытается исполнить инструкцию,последующую (по его мнению) за переходом еще до самого перехода. Если его предсказание сбывается,то труд был ненапрасным,если не сбывается — конвейер окажется недогруженным. В

итоге всех этих ухищрений среднее число тактов на инструкцию у Pentium Pro сократилось до 0,5 такта. В систему команд были введены новые инструкции, позволяющие писать более эффективные коды (с точки зрения минимизации ветвлений).

Фирма AMD в своих процессорах шестого поколения (K6) реализовала “беспорядочное исполнение”, но двойную независимую шину применять не стала. Вместо этого была увеличена тактовая частота шины Pentium,

46

весьма эффективной в однопроцессорных конфигурациях. Двойная шина (но без торжественного объявления) появилась лишь в процессорах K6-III. Благодаря такому решению сокет-7 (Super7) пережил целых два поколения процессоров. По микроархитектуре (способу реализации “беспорядочного исполнения”) процессоры K6 заметно отличаются от своих интеловских собратьев.

Пдобно пятому поколению, которое по ходу развития получило расширением MMX, так шестое поколение получило расширение 3DNow! (AMD) и SSE (Intel). Однако в отличие от единого MMX, эти два расширения не эквивалентны. У них общая “потоковая” направленность и реализация SIMD для чисел с плавающей точкой. Кроме того,данные,уже прошедшие обработку,в дальнейшем этим вычислительным процессом использоваться не будут и ими не следует засорять кэш. Теперь появились инструкции загрузки данных в кэш,а также записи в память минуя кэш. Прежде такого явного управления кэшированием не было.

47

Седьмое поколение

Общая характеристика¦

-асимметричное ядро с блоками, работающими на различных скоростях;

-значительно улучшенная версия суперскалярного механизма исполнения инструкций;

-новый кэш второго уровня,отслеживающий порядок выполнения инструкций;

-переработанные блоки операций с мультимедийными данными и числами с плавающей запятой;

-огромный набор новых инструкций;

-новая системная шина,работающая на высоких скоростях

-конвейер выполнения инструкций с большим числомстадий.

-абсолютно разные процессоры двух конкурирующих производителей

- Intel (Pentium 4) и AMD (Athlon).

Особенности процессоров Intel

Основные черты процессоров Intel определяют технологии NetBurst и Hyper-Threading, а так же некоторые особенности реализации кэш-памяти.

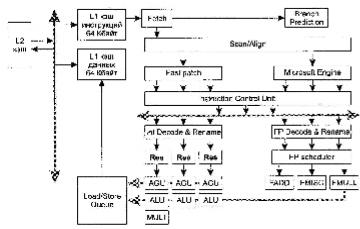

Исполнительный участок {Back End) содержит исполнительные устройства и обслуживающими их элементами.

Подготовительный участок {Front End) с устройствами,отвечающими за декодирование инструкций и своевременную их подачу на исполнительный участок. Сюда же входит группа устройств,обеспечивающих некоторые специфические возможности: блок предварительной выборки {Prefetch),

блок предсказания переходов {Branch Prediction Unit).

Подсистема памяти {Memory Subsystem), управляющая загрузкой и подачей данных на участки

Алгоритм работы процессора в грубом приближении выглядит так: подсистема памяти снабжает ядро данными из оперативной памяти,подготовительный участок приводит их к удобоваримому виду и передает на исполнительный участок для обработки. Участок Back End ведает непосредственной обработкой этого материала. Специальная группа устройств отвечает за своевременную подачу данных и предсказание следующих переходов, то есть создает комфортные условия для функционирования остальных компонентов ядра. На участке Back End имеется пять функциональных исполнительных устройств, каждое из которых выполняет свой перечень операций. Три устройства (два «быстрых» и одно «нормальное» АЛУ) занимаются операциями с целыми числами, два — операциями с действительными числами.

Раскладка операций на составляющие позволяет упростить каждую

стадию конвейера, уменьшить число логических элементов и тем самым повысить рабочую частоту ядра. Упрощением и выравниваем инструкций

48

занимается декодер, преобразующий инструкции CISC в микрооперации

RISC.

Если команду х86 нельзя представить в виде одной простой инструкции,декодер создает некую последовательность простых инструкций (микроопераций) RISC. В процессоре Pentium 4 вместо традиционного кэша команд,в котором хранится код х86, имеется кэш трассировки (Trace Cache). Он расположен после декодера,но перед остальными блоками процессора. В нем хранятся не инструкции CISC, а результаты их декодирования

— микроопераци. При такой архитектуре декодер работает независимо от остальных блоков,наполняя Trace Cache микрооперациями. Если в Trace Cache нетинструкций затребованного процессором участка кода,они сравнительно медленно загружаются из кэша L2,декодиру-ясь на лету. Естественно,что декодирование и выборка данных на этом участке происходят в очередности,определяемой исполняемой программой. Микрооперации «снимаются» прямо с декодера,по мере их готовности,и результирующая скорость будет не более одной инструкции за такт. При повторном обращении к тому же участку кода процессор избавляется от необходимости производить декодирование еще раз.

Если в программе есть условные переходы (то есть такие,которые зависят от результата выполнения какой-либо операции), надо постараться «угадать», произойдетэтотпереход,или нет. Блок предсказаний хранитспециальную таблицу истории переходов (Branch History Table), в которой записана результативность предыдущих примерно 4000 предсказаний. Кроме того, отслеживается точность последнего предсказания,чтобы при необходимости откорректировать алгоритм работы. Благодаря этому декодер выполняет по подсказке блока предсказания условный переход,а затем блок предсказаний проверяет,правильно ли было предсказано это условие. Микроархитектура Prefetch (предзагрузки или предвыборки) позволяет заранее знать,какие данные понадобятся процессору в будущем. Специальные механизмы анализируют последовательности адресов,по которым происходила загрузка данных,и пытаются предугадать следующий адрес.

Задача подсистемы памяти сравнительно проста: как,можно быстрее доставить затребованные данные и как можно быстрее снять полученный результат. Для этого активно используется кэширование данных в высокоскоростной памяти сравнительно небольшого объема. Процессор Pentium

4 имеет два,а модификация Extreme Edition даже три уровня кэш-памяти. Основная роль в ускорении работы отведена кэшу второго уровня. Фактически,именно кэш второго уровня становится основным хранилищем данных

вмикроархитектуре Pentium 4.

Вмодификации Pentium 4 на ядре Nortwood впервые реализована технология виртуальной двухпроцессорности Hyper-Threading. Немалая часть ресурсов ядра простаивает во время работы других элементов, а

49

технология Hyper-Threading позволяет загрузить временно простаивающие блоки другими задачами. Эффективность блоков Hyper-Threading при выполнении конкретных приложений сильно зависит от степени оптимизации кода программы. Чем лучше оптимизирован код для архитектуры Pentium 4, тем меньше будет выигрыш от применения Hyper-Threading, поскольку «правильный» код нагружает элементы процессора по максимуму. Если же оптимизация кода далека отидеала,происходятпромахи размещения данных в кэш-памяти, ошибки предсказания ветвлений, нарушение параллелизма выполнения инструкций. В результате часть аппаратных блоков ядра простаивает,ожидая результатов критичных операций. В этот момент свободные блоки могутбыть представлены операционной системе как элементы второго, логического процессора и получить собственные задачи,выполнение которых будет происходить независимо от работы других элементов.

Особенности процессоров AMD

Создание в 1999 г. процессорного ядра К7 седьмого поколения стало значительным достижением компании AMD. Здесь были реализованы выдающиеся технические решения: три параллельных исполнительных конвейера,системная шина с удвоенной частотой за счет передачи данных по фронту и спаду сигнала,асинхронная шина памяти,блоки декодера и предварительной выборки данных высокой интеллектуальности. Кэш-память первого уровня включает двухканальные частично-ассоциативные (наборноассоциативные) кэш команд и кэш данных емкостью по 64 Кбайт каждый. Кэш данных К7 обеспечивает одновременный доступ к двум 64-разрядным величинам при выполнении команд загрузки регистров и записи в память. Другой важной особенностью К7 является наличие в блоке кэша команд

специальной кэш-памяти предварительного декодирования,которая используется декодерами команд.

Кроме того,кэш команд первого уровня содержитдвухуровневый блок

50