Embedded system engineering magazine 2005.09

.pdf

<ESS 2005 Preview>

ESE Magazine September 05

30

System Design & Modelling

Wednesday 19th October

9.00

9.15

9.30

On-Target Rapid Prototyping

Mohamed Anas, The Mathworks

9.45

10.00Does UML Improve Software Quality? A Real-World Case Study

10.15 |

|

Niall Cooling, Feabhas |

|

|

|

10.30 |

|

Refreshments |

|

|

|

10.45 |

|

|

|

|

|

|

|

|

11.00 |

|

Migrating Structured Methods |

|

|

Legacy to a Modern MDA |

|

|

Environment – Allan Kennedy, |

11.15 |

|

|

|

Kennedy Carter |

|

|

|

|

11.30 |

|

Graphical System Design |

|

|

Ian Bell, National Instruments |

11.45 |

|

|

|

|

|

12.00 |

|

Making UML Work |

|

|

Niall Cooling, Feabhas |

12.15 |

|

|

|

|

|

12.30 |

|

|

|

|

|

12.45

Lunch

13.00

13.15

13.30Building an Entire Embedded System in UML

13.45 Colin Walls, Mentor Graphics

14.00

14.15

14.30

14.45 |

Design Patterns for High Availability |

|

Systems |

15.00 |

David Kalinsky, ENEA Embedded |

Technologies |

15.15

15.30

15.45

16.00

16.15

16.30

16.45

17.00

17.15

17.30

rics. QA C++ new features include Type Alias |

integrity analysis on behalf of PICMG. |

>>

Register now at www.embedded.co.uk

Perfect Combination…

Standard Platform and to Individual Customer’s Specification

Broadest Range of AdvancedTCA Packaging ProductsGlobal Availability and Project Support

Unique Internet Platform with downloadable Manuals: www.a-tca.com

Complete packaging solutions from the experts

and have now transformed the demands of the standard into technically high-grade products.

Schroff >> Stand 913

SDC SYSTEMS will be demonstrating a range of their lines including MQX Embedded's RTOS and MetaWare tools, General Software's EBIOS2000, FSM Labs' RTLinuxPro and iSYSTEM's ic3000 hardware debuggers.

Their range of products apply to the embedded design cycle from concept to implementation; including a x86 BIOS, Embedded Linux, Real-Time Operating Systems, Reference Design Hardware, Embedded Software, Debuggers and Emulators and Database/Data Management for embedded applications. In addition to their broad range of embedded technologies, SDC Systems have considerable engineering skills and offer system integration and on-site assistance and training to their customers.

SDC Systems >> Stand 707

STRETCH will be exhibiting MPEG4/H.264 and WiMax products with their entirely new generation of processors, the first to embed programmable logic within the processor core for compute intensive applications, on the Broadband Technology stand.

Stretch >> Stand 411

SYNPLICITY will showcase its new, patented graph-based physical synthesis technology and its DSP Synthesis software. Graph-based physical synthesis provides a single-pass physical synthesis flow for 90nm FPGAs, merging optimization, placement, and routing to ensure available, fast routes along critical paths. The Synplify DSP product offers designers the most efficient way to get DSP algorithms into hardware such as an FPGA, for DSP designs that are faster, lower cost, more flexible, and reach the market faster.

Synplicity >> Stand 500

TOSHIBA wants to discuss its latest range of Microcontroller, Microprocessor and Peripheral products in conjunction with its UK distributor Abacus Polar and its development systems partner AND Technology Research. Toshiba currently offer a growing range of flash 8-32bit CISC Microcontrollers with extensive peripheral options, also 32-64 bit RISC Microprocessors.

Automotive.

Toshiba has a number of interesting technologies including LCD drive, motor control, MPEG-4, low cost flash memory with security features and many more.

Toshiba >> Stand 530

WIND RIVER visitors will see demonstrations of three Workbench products, Wind River Workbench, Desktop Edition – an integrated development environment with a project system, build system, editor, and source code analysis capabilities; Wind River Workbench, Linux Edition – the industry’s first and only Eclipse-based open device software development suite; and Wind River Workbench, OnChip Debugging Edition – for developers engaged early in the device software development cycle

They can also learn about the recent release of specialised platforms for consumer and automotive devices, VxWorks 6.1 and a Linux edition of its platform for network equipment, and meet technical experts, who will be on hand to answer individual queries.

Wind River >> Stand 420

THE XILINIX embedded processing solutions include a wide variety of critical elements and are based on Platform FPGA devices like the Virtex-4, Virtex-II Pro and Spartan-3 families. These programmable system devices offer designers both hard PowerPC processor and soft MicroBlaze processor core options to allow an optimal balance of features, price and performance. Solutions also include the EDK product bundle, the Platform Studio Tool Suite, processor software libraries and IP, evaluation boards, reference designs, support, documentation, and debug capabilities.

Xilinix >> Stand 508

Conference fee

One day rate.............£190.00 + 17.5 % VAT Two day rate.............£345.00 + 17.5 % VAT

Discounts for early booking, IEE members and university groups

Exhibition tickets.................................... |

Free |

Register at www.embedded.co.uk |

|

Workshops each........ |

£95.00 + 17.5 % VAT |

Register now at www.embedded.co.uk

DIL/NetPC Family

|

E |

W |

|

|

||||

|

N |

DNP/9200 |

|

|||||

DIL/NetPC |

|

|||||||

(Host/Device) |

|

|||||||

> 2x |

USB |

|

||||||

|

|

|

Port |

|

Visit us at: |

|||

|

|

|

|

|

||||

> 2xSerial |

Ethernet |

|||||||

|

|

|||||||

> 10/100 |

Mbps |

|

|

|||||

|

|

|

|

Stand 412 |

||||

|

|

|

|

|

|

|

||

|

|

|

|

|

Heisterbergallee 72 > 30453 Hanover > Germany |

|||

|

|

|

|

|

Phn: +49-(0)511-40000-0 |

> Fax: +49-(0)511-40000-40 |

||

|

|

|

|

|

||||

E m b e d d e d S y s t e m s |

|

Email: sales@ist1.de |

> http://www.dilnetpc.com |

|||||

W W W . D I L N E T P C . C O M

Embedded PCs |

|

Packaged PCs |

|

LCD Displays |

|

|

|

|

|

Fieldbus |

|

Flash Storage |

|

Touchscreens |

|

|

|

|

|

Fanless Pentium M PC Systems

Microspace PC range

Pentium M and Celeron M Processor 1.4G/600MHz

Passive cooling no fan Aluminium case IP50 -40 to 70 deg C Low power consumption 8 to 30V DC

Vehicle approved CE and E1

100/10 Base-T LAN, miniPCI WLAN, Digital I/O 6 USB 2.0, Audio

3 parallel displays Fieldbus option BT878 Framegrabber DVD-R/CD-RW option CF & preheat HDD GPS and GSM option GSM Sleep/Wake

4 COM option PC/104 expansion PC/104+ expansion

from £770 net 600MHz 256RAM 40GB HDD

Miles Industrial Electronics Ltd

Phone: +44 (0)1604 771122

Buy Online

www.milesie.co.uk

catalyst.logic.nl

BUS and Protocol analyzer / Exerciser

PCI Express

USB & USB OTG

SAS / Serial ATA

Wireless USB Coming soon

Visit us at ESS, Birmingham, oct 19-20, booth # 207

For |

Linux, |

|

|

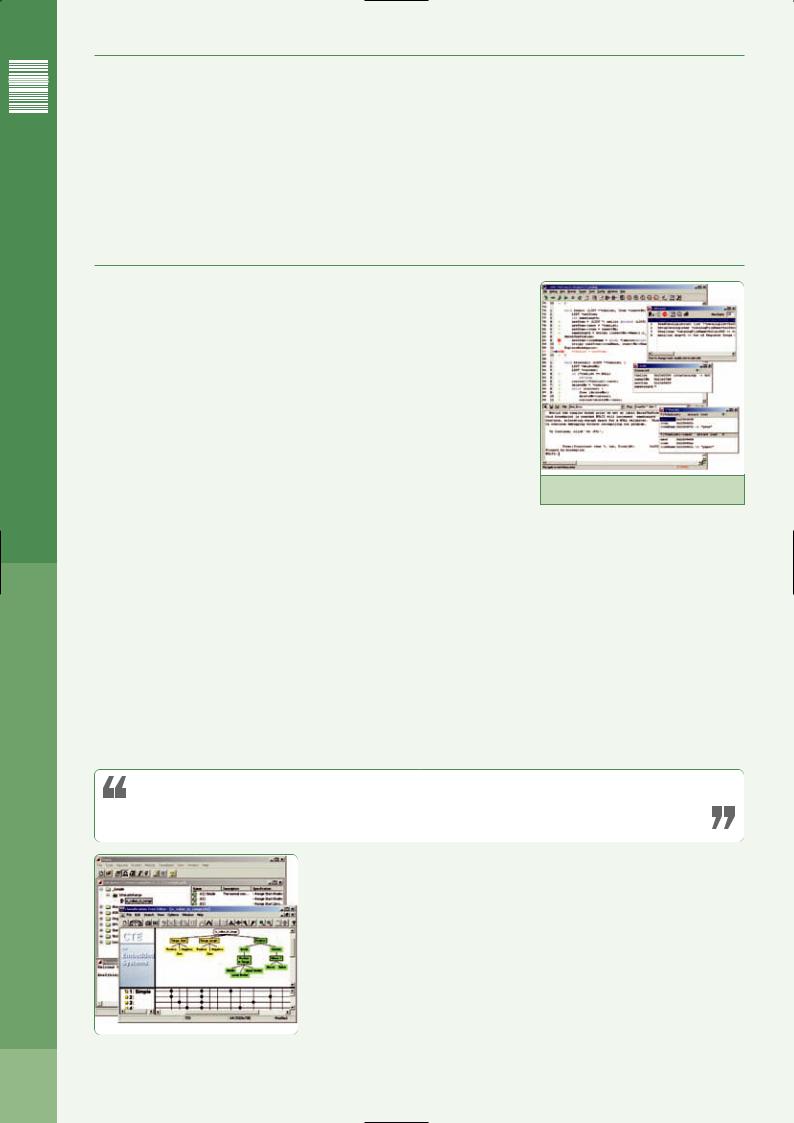

The New Journey Beyond...

ARK Series for Worry-Free Adventure

Robust, Reliable and Optimized Integration Intel® Pentium® M Embedded Box Computers

Advantech ARK-3380 Series of Embedded Box Computers are designed for space critical applications and can be operated as standalone or integrated systems. Targeting video, automation and network control, this type of plug-and-forget, maintenance free, ubiquitous device brings new momentum to embedded computing.

Compact & Robust |

Fanless Operation |

|

||||

Long Life Cycle Support |

Flexible I/O Configuration |

|||||

ARK-3380 |

ARK-3382 |

|

|

|

||

Video Intensive |

Network Intensive |

|

|

|

||

|

|

|

|

|

Advantech (UK) Ltd |

|

|

|

|

|

|

Tel: +44 (0)1908 304 800 |

|

|

|

|

|

|

Fax: +44 (0)1908 304 820 |

|

© 2005 Advantech Co., Ltd. www.advantech.com |

||||||

Email: embedded@advantech-uk.com |

||||||

<In-Depth>

In-Depth: Software testing –

New challenges for future systems

<Written by> Martin Whitbread </W>

As software gains in importance for embedded devices, so tools are needed to manage the complexity of testing.

AS THE SOFTWARE content increases year on year, the

of software specification, implementation and test

Figure 2: The MULTI user screens

ESE Magazine September 05

The history of large IT projects is not one of which any industry can be proud, and yet embedded systems are racing ahead in complexity

|

part of the debugger so that they become inde- |

|

|

|

pendent windows on the workstation. This pro- |

|

|

|

vides increased visibility and control over the dis- |

|

|

|

play of information in the debugger. Windows that |

|

|

|

have been separated from the debugger can also |

|

|

|

be "docked" to rejoin the main debugger work- |

|

|

|

space controls. The CodeWarrior Debugger's work- |

|

|

|

space allows users to focus on complex debugging |

|

|

|

tasks. Each workspace contains just the set of |

|

|

|

views needed for the task at hand. The application |

|

|

|

workspace provides a high-level view of the target |

|

|

Figure 1: Code Analysis with Tessy |

software, while the hardware workspace provides |

|

|

a low-level view of the target hardware. |

using JTAG-based run control. |

||

|

34

<<

Figure 2: The MULTI user screens

UML is well supported with tools – these are migrating towards the Eclipse IDE. Amongst the tool providers are Aonix, Artisan, Gentleware, IBM, I-Logix and Rhapsody

UML is well supported with tools – these are migrating towards the Eclipse IDE. Amongst the tool providers are Aonix, Artisan, Gentleware, IBM, I-Logix and Rhapsody

code for the ARM7, ARM9, ARM9E, ARM10 and Intel XScale families. The C-SPY debugger supports the ARM Multi-ICE JTAG interface and other RDI-based JTAG interfaces, the EPI Jeeni JTAG interface, Macraigor’s mpDemon Raven and Wiggler JTAG interfaces as well as ARM Angel. It also includes plug-in modules for CMXRTX RTOS and ThreadX RTOS.

Simulink

Many modern systems are reaching a complexity that is beyond normal debugging tools and code generation technologies have to be considered in order to create the product on time and on cost. Two options for this spring to mind, Simulink and UML. The former is supported by Reactive Systems’ Reactis tool suite. Reactis is an embedded software design automation tool suite currently consisting of three components:

the replay of tests generated by Reactis Tester, the graphical display of different coverage metrics, and the capability to fine-tune Tester-generated test suites.

●Reactis Validator automatically searches models for violations of user-specified requirements.

UML

UML is well supported with tools, and again these are migrating towards the Eclipse IDE. Amongst the tool providers are Aonix, Artisan, Gentleware, IBM, I-Logix and Rhapsody. (If you go to http://www.objectsbydesign.com/tools/uml tools_byCompany – you will see a larger number of mainly Java based UML tools).

Aonix Ameos

Ameos combines UML 2.0 Profile support, MDA based Model Transformation and the usage of colour in a unique fashion. This ensures a higher level of abstraction in the models and targetindependent modeling. By implementing the current UML standard Ameos can be used to describe business processes, to design architectures for SW systems and to model dynamic aspects in State Machines with hard timing constraints. The Model management of the UML is an integrated part of Ameos and allows distributed working, private workspaces and the configuration of new versions. The Ameos MultiUser Repository ensures an appropriate scaling even in large projects.

Artisan’s Real-time Modeler

This tool includes UML modelling plus real-time extensions, supporting the industry-standard Unified Modelling Language (UML) notations,

eling with other facets of the lifecycle. Requirements stored and managed in Rational RequisitePro can be accessed, associated to corresponding modelling elements, and synchronized with user-selectable rules. They can generate reports highlighting traceability from requirements to design. Modell¬ing files can be managed by Rational ClearCase LT. As an alternative, the product integrates with Concurrent Versions System (CVS) for customers already committed to that tool. Rational Software Modeler integrates with the IBM Rational Team Unifying Platform, provid¬ing requirements management, trace¬ability, model version control, and other team management functions throughout the lifecycle. IBMs absorption of the Rational tools means that the Eclipse IDE is a favoured environment. <Ends>

References:

Tessy – www.hitex.co.uk

Freescale’s MetroWerks CodeWarrior – www.codewarrior.com

WindRiverWorkbench–www.windriver.com IAR Embedded WorkBench – www.iar.com

Reactive-Systems’ Reactis – www.reactive-systems.com

Greenhills’ MULTI – www.ghs.com

Aonix Ameos – www.aonix.com

Artisan’ Real Time Modeler – www.artisansw.com

Gentleware’s Poseidon – www.gentleware.com

IBM Rational’s Software Modeler – www-306.ibm.com/software/rational/

</In-Depth>

ESE Magazine September 05

35

</Feature>

ESE Magazine September 05

Trouble shooting unknown boards

<Written by> Andy Bonner, Cupio Ltd </W>

Trouble shooting a poorly documented single board computer requires a new breed of ATE.

MBEDDED SYSTEMS often con- |

be checked, and power chips identified and |

off the shelf single board computers |

replaced. |

manufactured in the Far East. Their popu- |

Beyond this, effective troubleshooting |

larity is due to their low cost and ease |

becomes more difficult. Even if detailed docu- |

E |

mentation is available, test probes, digital |

|

scopes and simulators or function generators |

|

and logic analyzers become necessary, together |

|

with increasing demands on experience and |

|

skill levels. BGA and PQFP packages cannot be |

|

accessed with conventional test clips. |

|

ATE for unknown boards |

|

However a different approach using benchtop |

|

ATE equipment is now available. Its functional- |

|

ity eliminates the need for other instruments |

|

and its setup capability reduces the skill levels |

|

needed to successfully troubleshoot. Its learn- |

|

ing mode can eliminate the need for documen- |

|

tation. |

|

The strategy here comprises two compo- |

|

nents. If the board has been roughly handled or |

a VHDL simulation of the component which more completely represents the component under all conditions. This simulation can be drawn from the ATE library or responses learned by the ATE from a known good board. The Learn mode is important because it allows test sequences for boards with no documentation to be developed.

Boards with a bus based architecture also benefit from Digital Guarding, which eliminates bus contention. Bus connected chips apart from the one under test are forced into tristate disconnect to avoid unwanted loading on the bus.

ATE can test analogue and mixed signal as well as digital components, as well as mixed logic devices.

Inaccessible pins

Increasingly, boards include BGA or PQFP devices with pins inaccessible to test clips. Such boards provide a 5 way JTAG connector allow-

The functionality of benchtop ATE equipment eliminates the need for other instruments and its setup capability reduces the skill levels needed to successfully troubleshoot.

The functionality of benchtop ATE equipment eliminates the need for other instruments and its setup capability reduces the skill levels needed to successfully troubleshoot.

www.cupio.co.uk

response to a truth table prediction, or, better,

36

Standard for efficient test automation

<Written by> Ren Drescher,

Testing Technologies IST GmbH </W>

The European Telecommunications Standards Institute (ETSI) are promoting a family of standards and tools for telecoms applications.

IN SYSTEM ENGINEERING, testing is a generally accepted approach to validate systems and system components.

Assured quality of system and system components is particularly important, as the time- to-market become even shorter. A systematic approach to testing distributed systems is essential, so that the requirements of the market can be fulfilled. In the past, a methodology and framework for testing distributed systems, known as conformance testing methodology and framework (CTMF), have been developed and internationally standardized. CTMF covers all aspects of testing distributed systems such as test suite specification, test notation (TTCN - Tree and Tabular Combined Notation), test implementation and test execution. CTMF has been successfully

regression, system and integration testing. TTCN-3 is on syntactical (and methodologi-

cal) level a drastic change compared to previous TTCN versions. However, the main concepts of TTCN have been retained and improved and new concepts have been included, so that TTCN-3 will be applicable for a broader class of systems. New concepts are, e.g. a test execution control program to describe relations between test cases such as sequences, repetitions and dependencies on test outcomes, dynamic concurrent test configurations, and test behavior in asynchronous and synchronous communication environments. Further improved concepts are, e.g. the integration of ASN.1, the module and grouping concepts to improve the test suite structure, and the test component concepts to

A text-based language for specifying tests for reactive systems

testing including interoperability, robustness,

|

|

C3 |

|

l- |

|

ne |

|

|

ePa |

|

|

ePanel-C3

Full featured SBC for mobile applications

Low profile - mounts behind LCD

Supports digital and LVDS displays

Low power x86 compatible CPU

300 MHz to 1 GHz versions

MPEG2 hardware decoder

Smart battery charger

H a l l 7 B o o t h 3 0 6

Our info hotline:

+ 44 1243 523 500

www.kontron-emea.com/flatpanel s a l e s - g r a p h i c @ k o n t r o n . c o m

... We Drive Your Display !

</Feature>

ESE Magazine September 05

Tackling tough problems

<Written by> By Reg Waller, ASSET InterTech </W>

Boundary scan (JTAG) can provide testing throughout the product life cycle, even in hard to reach places.

FAULTS AND FAILURES in embedsystems are quite different from in other types of electronic systems.

embedded systems are in hard-to-

Local embedded system test/configuration

Server

Internet

Local ScanWorks laptop

Remote embedded system test/configuration

Remote ScanWorks station

Figure 1: Embedded Boundary Scan

during assembly and manufacturing, and even later after the system has been installed. As a result, higher quality systems are shipped to the field and, when troubleshooting is needed, the cause of a structural failure is identified faster, returning the system to service in short order.

Another important use of boundary scan is in-system programming. The four-wire JTAG infrastructure on a circuit board is available to reconfigure programmable logic devices (PLDs) or load data into memory. System-level JTAG techniques can enable remote access via the Internet, for example, to PLDs or memories. For embedded systems in far-away or hard-to-reach places, downloading firmware upgrades remotely without dispatching a technician can reduce costs tremendously. (Figure 1)

What is boundary scan?

Boundary scan is designed into chips, circuit boards and systems. Boundary scan chips have a multi-purpose memory element called a bound- ary-scan cell. A circuit board’s collection of boundary-scan cells is configured into a parallelin, parallel-out shift register by way of the fourwire JTAG interface. Data can be shifted into and out of the scan chain that connects the boundary scan cells on multiple devices on one or more circuit boards or assemblies in the system. This device-level access can also be used to load data into PLDs or memories.

Devices that do not have embedded bound- ary-scan cells can still be tested by boundary scan. A boundary-scan device directly connected to a non-boundary-scan device can drive signals onto the non-boundary-scan device and test its interconnects in this way.

How is boundary scan used?

Boundary scan can be used to test the interconnection between a chip and a circuit board as well as the structural integrity of assembled circuit boards. And if the board-level boundary-scan facilities are connected and a system-level JTAG architecture established, then system-level boundary-scan operations can also be conducted.

For embedded systems, many of which are subjected to harsh environmental conditions, system-level JTAG operations can be very beneficial. For example, many companies use techniques such as HALT (Highly Accelerated Life Testing) or other environmental tests as part of

the design validation process. If a manufacturing fault is detected, system-level JTAG diagnostics can identify netor pin-level faults and eliminate the time the test group might spend trying to find a design fault. System-level boundary scan is available in the environmental test chamber at whatever temperature or at whatever level of stress the system is subjected to.

Fast ROI

Boundary scan’s return-on-investment (ROI) is very fast since it can reduce costs during every phase of an embedded system’s life. Beginning with the design phase, boundary scan can help developers quickly validate a design or debug a problematic prototype circuit board.

As part of the assembly and manufacturing process, the increased test coverage made possible by the embedded JTAG infrastructure will yield higher quality systems, which leads to increased reliability and durability. In addition, problems on any failed circuit boards or assemblies can be rapidly diagnosed down to the level of a particular pin on a device. With this kind of information, repair operations are much more effective and the firm’s investment in assembled but failed circuit boards can be recouped.

Lastly, after embedded systems are installed, boundary scan can reduce support costs significantly. For example, many providers of embedded systems must contend with the “no fault found” (NFF) condition. To return a high-availabil- ity system to service quickly, technicians routinely remove and replace one or more circuit boards that might be the cause the problem. Subsequently, the questionable boards are tested and a high percentage of them are often classified as “no-fault-found.” NFF boards are sometimes returned to service where the costly cycle of failure, troubleshooting and testing begins again. The precise diagnostic capabilities of sys- tem-level JTAG can eliminate the guesswork and drastically reduce the NFF costs.

Ultimately, developers of embedded systems are finding that designing boundary scan into their applications has a big pay off in terms of reducing the cost of test and support, improving the quality and reliability of their products, and simplifying the way software updates are loaded into systems in the field. <Ends>

www.asset-intertech.com/

38