Konspekt_lektsy_MPT

.pdf

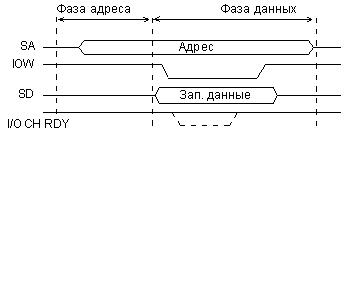

Адрес остается на шине SA до конца цикла. Фаза адреса, одинаковая для обоих циклов, заканчивается с началом строба обмена данными - IOR или -IOW. В течение фазы адреса устройство-исполнитель должно принять код адреса и распознать или не распознать его. Если адрес распознан, исполнитель готовится к обмену.

В фазе данных цикла чтения (рис. 7.6) процессор выставляет отрицательный сигнал чтения данных из устройства ввода/вывода - IOR. В ответ на него устройство-исполнитель должно выдать на шину данных SD свой код данных (читаемые данные). Логика на шине данных положительная. Через установленное время строб обмена - IOR снимается процессором, после чего снимается также и код адреса с шины SA. Цикл заканчивается без учета быстродействия исполнителя.

Рис. 7.6. Цикл чтения из УВВ на магистрали ISA.

Рис. 7.7. Цикл записи в УВВ на магистрали ISA.

Но так происходит только в случае основного, синхронного обмена. Кроме него на магистрали ISA также предусмотрена возможность асинхронного обмена. Для этого применяется сигнал готовности канала (магистрали) I/O CH RDY. Тип выходного каскада для данного сигнала — ОК, для предотвращения конфликтов между устройствами-исполнителями. При синхронном обмене сигнал I/O CH RDY всегда положительный. Но медленное устройство-исполнитель,

91

не успевающее работать в темпе процессора, может этот сигнал снять, то есть сделать нулевым сразу после начала строба обмена. Тогда процессор до того момента, пока сигнал I/O CH RDY не станет снова положительным, приостанавливает завершение цикла, продлевает строб обмена. Конечно, слишком большая длительность этого сигнала рассматривается как аварийная ситуация. Для простоты понимания можно считать, что устройство-исполнитель формирует в данном случае отрицательный сигнал неготовности завершить обмен. На время этого сигнала обмен на магистрали приостанавливается.

Принципиальное отличие асинхронного обмена по магистрали ISA от асинхронного обмена по магистрали Q-bus состоит в следующем. Если в случае Q-bus сигнал подтверждения обязателен, и его должен формировать каждый исполнитель, то в случае ISA сигнал о неготовности исполнитель может не формировать, если он успевает работать в темпе процессора. Зато в случае Q-bus к концу цикла обмена процессор всегда уверен, что устройство-исполнитель выполнило требуемую операцию, а в случае ISA такой уверенности нет.

В фазе данных цикла записи по магистрали ISA (рис. 7.7) процессор выставляет на шину данных SD код записываемых данных и сопровождает их стробом записи данных в устройство ввода/вывода -IOW. Получив этот сигнал, устройство-исполнитель должно принять с шины SD код записываемых данных. Если оно не успевает сделать это в темпе процессора, то оно может снять на нужное время сигнал I/O CH RDY после получения переднего фронта сигнала -IOW. Тогда процессор приостановит окончание цикла записи.

Рассмотренные примеры, конечно, не раскрывают всех тонкостей обмена по упомянутым магистралям. Они всего лишь иллюстрируют главные принципы обмена по ним.

92

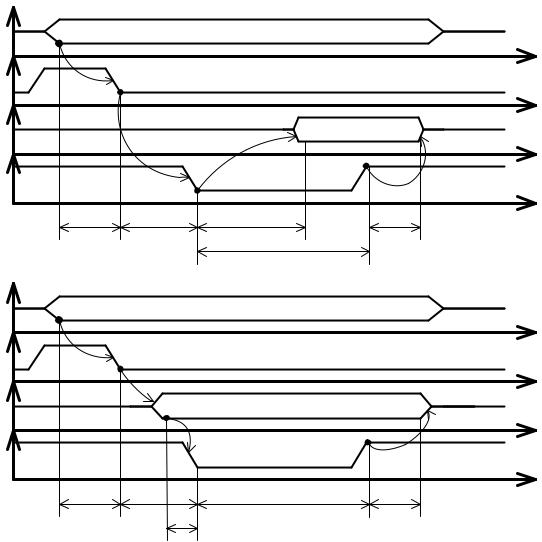

Циклы обмена для использующихся в лабораторной базе данного курса макетах показаны на рисунках 7.8 и 7.9.

ША

СА В

ШД

ЧТ ПД Н

ta |

tcч |

tчд |

tуд |

|

|

tчт |

|

|

|

Цикл чтения |

|

ША

СА В

ШД

ЗАП ПД Н

ta |

tcч |

tзап |

tуд |

|

|

tпр |

|

Цикл записи

Рис. 7.8. Временные диаграммы чтения и записи для синхронной демультиплексированной шины.

93

Рис. 7.9. Временные диаграммы чтения и записи для синхронной мультиплексированной шины

94

Раздел 8. Системы отладки МПУ

По сравнению с традиционной радиоэлектронной аппаратурой, микропроцессорная техника имеет ряд специфических особенностей:

-высокую сложность и трудоемкость разработки и отладки аппаратных и, в особенности, программных компонент микропроцессорного устройства;

-основные ресурсы микропроцессора и однокристальной ЭВМ сосредоточены внутри микросхемы и, как правило, не имеют самостоятельных выводов. Это существенно затрудняет доступ к внутренним ресурсам, и, как следствие, поиск и анализ неисправностей и сбоев в работе микропроцессорного устройства;

-необходимость одновременного контроля за состоянием множества быстропротекающих процессов на внутренних шинах и интерфейсных магистралях, что также сильно затрудняет поиск неисправностей.

8.1. Основные понятия и термины

Отладка МПУ – процесс обнаружения ошибок в АС и ПС, их исправление и обеспечение полной работоспособности МПУ. Устройство считается отлаженным, когда оно полностью функционирует на реальной аппаратуре в реальных условиях.

Для разработки, производства и эксплуатации микропроцессорной техники необходимы специальные инструментальные средства, позволяющие автоматизировать наиболее трудоемкие этапы проектирования. Такие средства называются отладочными средствами.

Хотя не все МПУ выполнены на базе микропроцессора или ОЭВМ имеющего гарвардскую архитектуру, все равно различие между

памятью программ и памятью данных в МПУ проявляется

95

достаточно заметно. Эта особенность МПУ объясняется тем, что штатная программа МПУ хранится в микросхеме ПЗУ, а данные – в микросхеме ОЗУ, что, с точки зрения структурной схемы является существенно различными узлами МПУ.

В дальнейшем термины ПЗУ и ОЗУ будут использоваться как для обозначения узлов структурной схемы, так и для обозначения памяти программ и памяти данных соответственно – вне зависимости от архитектуры МПУ. Конкретный смысл, скрывающийся за данными терминами, будет ясен из контекста.

управления объекту К

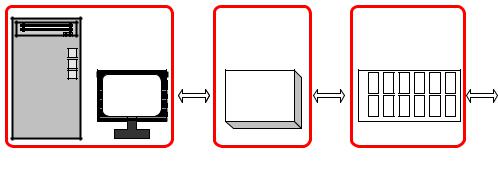

Рис 8.1. Система отладки МПУ (общий случай)

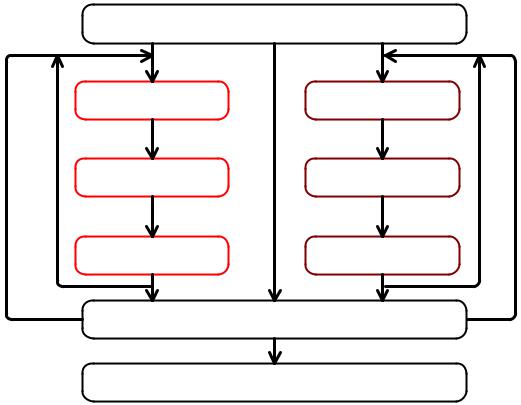

На рисунке 8.1 показана наиболее часто встречающаяся структура системы отладки. В эту систему входят:

-инструментальная ЭВМ (ИЭВМ). Чаще всего в этой роли выступает персональный компьютер IBM PC. Назначение ИЭВМ – подготовка, трансляция и построение отлаживаемой программы, управление процессом отладки и роль интерфейса отладочного устройства;

-отладочное устройство. Как правило, в роли отладочного устройства выступает эмулятор того или иного типа. В некоторых случаях отладочное устройство выполнено в виде одной платы и входит в состав ИЭВМ. Такое отладочное устройство обычно называется внутренним или встраиваемым. В этом случае

существенно снижается цена отладочного устройства, так как

96

отпадает необходимость в корпусе и блоке питания. Однако, из-за дефицита места на плате стандартного размера, у таких устройств обычно отсутствует гальваническая развязка между ИЭВМ и объектом отладки. Из-за этого не исключается возможность попадания высокого напряжения из объекта отладки внутрь ИЭВМ. Подобное может произойти как следствие неадекватных действий отлаживаемых ПС или из-за сбоев отлаживаемых АС.

-Объект отладки. Им, как правило, является отлаживаемое МПУ. На завершающих этапах отладки к МПУ подключается объект управления – то самое оборудование, для которого и разрабатывается МПУ.

Вряде случаев использование реального объекта управления при отладке не возможно. Такая ситуация может возникнуть из-за:

-больших размеров (например – разрабатывается модуль управления подъемным краном);

-возможности разрушения оборудования при неизбежных в процессе отладки сбоях АС и ПС;

-из-за крайней опасности для объекта управления тех режимов работы МПУ, которые и подлежат отладке.

Например, для адекватной проверки работы системы управления при аварии необходимо эту аварию реально вызвать. В противном случае останется вероятность, что в случае реальной аварии реальные датчики и исполнительные устройства будут действовать не так, как заложено в ПС.

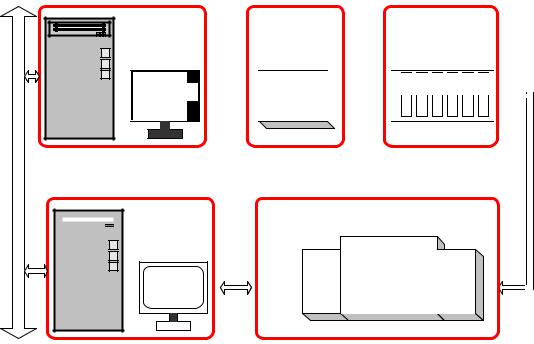

В таких случаях приходится применять более сложный отладочный комплекс, показанный на рисунке 8.2.

97

ЛВС

ВСЭ

ВСЭ

Инструментальная ЭВМ |

Отладочное |

Объект отладки |

|||||

устройство |

|||||||

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

И |

Технологическое |

И |

Ч |

оборудование |

Ч |

1 |

|

2 |

|

|

|

Технологическое оборудование - |

|

Технологическая ЭВМ |

||||

иммитатор |

||||

|

|

|

||

Рис 8.2. Система отладки МПУ (расширенный случай)

Вэтом случае к оборудованию добавляются:

-Технологическая ЭВМ (одна или несколько), объединенные между собой локальной вычислительной сетью (ЛВС). Задача этих ТЭВМ – с помощью технологического оборудования имитировать поведение объекта управления на время отладки.

-Технологическое оборудование. Предназначается для создания максимально правдоподобной копии объекта управления. Как правило, в нем стараются использовать датчики и исполнительные механизмы, аналогичные тем, которые используются

вреальном объекте управления. Взаимодействие между ними осуществляется под управлением ПС ТЭВМ. Как правило, технологическое оборудование стараются создать таким образом, чтобы оно не столько имитировало сигналы датчиков (в этом случае существует риск неадекватной имитации), а воздействовало своими исполнительными устройствами на реальные датчики, идентичные

тем, которые будут штатно поставлять информацию МПУ.

98

В некоторых литературных источниках ИЭВМ и все ТЭВМ объединяют в одно целое – в базовый вычислительный комплекс

(БВК).

8.2. Процесс отладки МПУ

Отладка МПУ — это процесс обнаружения ошибок, их исправления и обеспечения полной работоспособности МПУ. Микропроцессорное устройство считается отлаженным, когда оно полностью функционирует на реальной аппаратуре в реальных условиях.

Комплексные технические требования к МПУ

ПС отладки комплексной процессе в Корректировка |

ПС отладки автономной процессе в Корректировка |

Исходный текст ПС

Загрузочный модуль

Отладка ПС на модели

Схемы АС

Прототип АС

Отладка прототипа АС

в Корректировка |

Корректировка |

АС отладки автономной процессе |

АС отладки комплексной процессе в |

Комплексная отладка МПУ в реальных условиях

Продолжение проектирование МПУ

Рис 8.3. Этапы процесса отладки

Процесс отладки является важнейшим этапом проектирования и создания МПУ и ему придается большое значение потому, что это первый этап проверки и отработки принятых решений в реальных условиях функционирования. Если все предварительные этапы проектирования МПУ можно считать абстрактным проектированием

99

МПУ, при котором АС и ПС представляются в виде схем и текстов программ, то этап отладки следует назвать функциональным проектированием в реальных условиях. Цель этого этапа — обеспечение выполнения всех функций МПУ полностью от начала до конца (рисунок 8.3). В результате выполнения каждой из параллельных ветвей автономного проектирования АС и ПС реализуется лишь часть каждой отдельной функции МПУ, так как согласно сущности МПУ полностью каждая функция может быть выполнена только при комплексном объединении АС и ПС в МПУ.

Процесс отладки МПУ носит циклический характер и придает такой же характер всему процессу проектирования МПУ. На рисунке 3 показано, что обнаруженные при отладке несоответствия исходным техническим требованиям, некорректное выполнение функций, ошибки и неточности в АС или ПС требуют проведения соответствующих корректировок и по крайней мере частичного повторения всех этапов проектирования. После выполнения корректировок снова необходима отладка, т. е. процесс повторяется. После прохождения каждого цикла отладки МПУ все более удовлетворяет заданным техническим характеристикам.

Цикл отладки включает следующие виды работ:

1)организация взаимодействия АС и ПС в реальных условиях функционирования МПУ;

2)обнаружение несоответствий исходным требованиям, некорректно выполняемых функций, ошибок и неточностей в АС и ПС МПУ и анализ причин и источников их появления;

3)корректировку или доработку прототипа АС и ПС МПУ путем частичного повторения предшествующих этапов проектирования;

4)тестирование МПУ в комплексе АС и ПС;

5)запись отлаженных ПС на носитель в ППЗУ и повторное тестирование МПУ.

100