мпсу / Лекции pdf / Лекции модуль 1 МПСУ

.pdf

Запрет по х2 |

|

y = x1 |

|

2 |

|

0 |

0 |

1 |

0 |

|

x |

||||||||||

|

|

|

|

|

|

|

|

|

||

Импликатор от |

|

y = x1 |

|

2 |

1 |

0 |

1 |

1 |

||

|

x |

|||||||||

х2 в х1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Микросхема К155ЛА3 (рис. 1, в) содержит четыре логических элемента 2И- НЕ (цифра "2" показывает число входов у одного элемента). Микросхемы KI55JIA6 (рис.1, б), содержащая два элемента 4И-НЕ имеет повышенную нагрузочную способность, что обозначается треугольником на поле условного изображения. Микросхема К155ЛР1 (рис.1, в) содержит два элемента 2И-2ИЛИ-НЕ. В одной из частей этой микросхемы может быть увеличено на единицу число логических элементов типа И, подключаемых к элементу ИЛИ. Для этого необходимо использовать так называемый расширитель по ИЛИ, который подключают к специальным выводам Э (эмиттера) и К (коллектора). К этим выводам параллельно можно подсоединять несколько расширителей, например два четырехвходовых, входящих в состав микросхемы К155ЛД1 (рис.1, г).

а |

б |

в |

г |

Рис. 1. Условные обозначения логических элементов: |

|

||

а - 4×2И-НЕ; б - 2×4И-НЕ; в - 2×2И-2ИЛИ-НЕ; г - расширитель;

Некоторые микросхемы имеют выход с открытым коллектором. Для нормальной работы таких микросхем требуется подключение выхода к источнику питания через внешнюю нагрузку. Внешней нагрузкой могут быть резисторы, реле и другие элементы. Удобство таких микросхем состоит в том, что нагрузка может быть подключена к независимому источнику питания с повышенным напряжением (до 30 В).

Триггеры. Схемы с логическими элементами, между которыми включены обратные связи, могут запоминать информацию. Такие схемы называют триггерами. Триггер имеет два устойчивых состояния, которые определяются значением выходного сигнала Q. При Q = 1 триггер находится в единичном состоянии; при Q = 0 - в нулевом. Обычно триггер имеет и инверсный выход Q. Под воздействием входных сигналов триггер скачкообразно переходит из одного состояния в другое.

19

По способу организации логических связей триггеры подразделяют на четыре основных типа:

1.RS - с установочными входами;

2.Т- счетные;

3.D- задержки;

4.JK- универсальные.

Каждый символ в обозначении триггера соответствует наличию аналогичного информационного входа.

В логических устройствах широко используют синхронные триггеры, имеющие дополнительный вход управления С, называемый тактовым. Сигнал на тактовом входе определяет интервалы времени, в течение которых состояние триггера приходит в соответствие со значениями сигналов на информационных входах.

Триггеры типа RS и D могут иметь статический тактовый вход. В этом случае триггер реагирует на сигналы, действующие на информационных входах только при наличии единичного (при прямом управлении) или нулевого (при инверсном управлении) сигнала С на тактовом входе.

Триггеры RS и Т выпускают также в асинхронном варианте, т.е. без тактового входа С. Работа асинхронного RS-триггера эквивалента работе синхронного триггера, у которого на статическом тактовом входе есть сигнал, допускающий его переключение. Особенность асинхронного Т-триггера состоит в том, что он имеет динамический вход, при котором состояние изменяется на противоположное при формировании фронта (прямой вход) или среза (инверсный вход) входного сигнала.

Ниже для синхронных триггеров представлены значения выходного сигнала Q в зависимости от информационных и входных сигналов до срабатывания триггеров (срабатывание происходит после появления сигнала на тактовом входе):

Сигналы на информационных входах: |

|

|

|

|

|

|

R, K |

0 |

0 |

1 |

1 |

||

S, J, Т, D |

0 |

1 |

0 |

1 |

||

Сигнал на выходе триггера типа: |

|

|

|

|

|

|

RS |

Q |

1 |

0 |

- |

||

|

|

|

|

|

|

|

JK |

Q |

1 |

0 |

Q |

||

D |

Q |

1 |

0 |

1 |

||

|

|

|

|

|

|

|

Т |

Q |

Q |

Q |

Q |

||

Для RS-триггера сочетание сигналов R = 0, S = 0 переводит его в режим хранения информации, при котором на выходе триггера сохраняется состояние, существовавшее ранее. Комбинацию сигналов R = 1, S = 1 называют запрещенной, так как сигнал на прямом выходе, соответствующий этой комбинации, может быть утерян при переходе в режим хранения информации из-за состязательности переходных процессов.

Для JK-тригтера сигналы J = 1, К = I вызывают изменение состояния триггера на противоположное по отношению к ранее существовавшему состоянию.

20

Некоторые триггеры имеют подготовительный вход V разрешения приема информации. При V = 1 триггеры работают в нормальном режиме, а при V = 0 триггеры сохраняют прежнее состояние независимо от изменения сигналов на других входах.

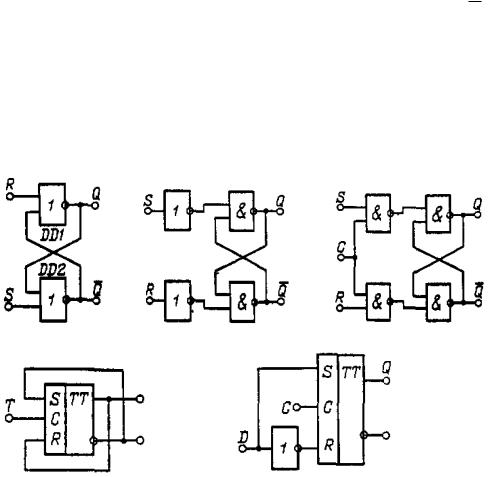

На рис. 2 представлены схемы триггеров различных типов. На рис. 2, а показана схема асинхронного RS-триггера с использованием элементов ИЛИ-НЕ. Входы R и S служат для установления триггера в состояние "0" и "1". Если на входах триггера с исходным состоянием Q = 1 действуют сигналы R = S = 0, то оба

элемента DD1 и DD2 работают по отношению к сигналам Q и Q как элементы НЕ, и состояние триггера сохраняется. Если на вход триггера подать сигнал R = 1, S = 0, то сигнал R установит выход элемента DD1 в "0", и на инверсном выходе триггера сформируется "1". Этот сигнал проходит на нижний вход элемента DD1, но не вызывает никаких изменений, так как при входных сигналах 1, 0 и 1, 1 на выходе элемента DD1 сохраняется "0”. Повторная подача сигналов R = S = 0 не приводит к изменению состояния триггера, поскольку выходной сигнал элемента DD1 равен "0" как при входных сигналах 1, 1, так и при сигналах 0, 1.

а |

б |

в |

г д

Рис. 2. Принципиальные схемы триггеров:

а – асинхронного RS-триггера на элементах ИЛИ–НЕ; б – асинхронного RS-триггера на элементах И–НЕ;

в – RS-триггера со статическим тактовым входом; г – асинхронного Т-триггера;

д – синхронного D-триггера;

В триггере типа RS на элементах И-НЕ (рис. 2, б) требуется установка дополнительных инверторов. В противном случае триггер имеет инверсное управление, так как устанавливается в состояние "1" сигналами S = 0, R = 1, а в состояние "0" - сигналами S = 1, R = 0. В триггере с инверсным управлением комбинации сигналов R = S = 0 запрещена, а режим хранения информации наступает при R = S = 1.

21

На рис. 2, в приведена схема синхронного RS-триггера со статическим тактовым входом. Если на вход С подан сигнал, равный 1, этот триггер работает так же, как триггер на рис. 2, б при нулевом сигнале на входе С состояние триггера изменить входными сигналами нельзя.

На рис. 2, г показана схема асинхронного T-триггера, срабатывающего по срезу входного сигнала. В данном случае счетным входом T-триггера является тактовый вход двухступенчатого RS-триггера. Ввиду наличия перекрестных обратных связей при каждом окончании единичного счетного сигнала Т в RS- триггер записывается состояние, противоположное ранее хранимому.

На рис. 2, д показана схема синхронного D-триггера. Выходной сигнал Q триггера повторяет входной сигнал D в момент окончания единичного тактового сигнала С, Это связано с тем, что при D = 1 на входе RS-триггера возникают сигналы S = 1, R = 0, которые устанавливают этот триггер в единичное состояние. При D =- 0 на входах RS-триггера формируются сигналы S=0, R=1, которые устанавливают триггер в нулевое состояние. В периоды времени, когда тактовый сигнал постоянен и равен 0 или 1, состояние D-триггера не изменяется. Двухступенчатый синхронный D-триггер может задерживать прохождение входного сигнала на период следования тактовых импульсов.

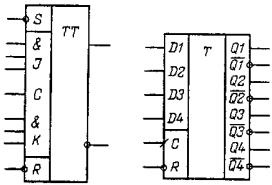

а б

Рис. 3. Изображения микросхем: а – JK-триггера; б – D-триггера;

На рис. 3 даны условные изображения микросхем с триггерами. Микросхема К155ТВ1 (рис. 3, а) представляет собой двухступенчатый JK-триггер с дополнительными инверсными входами S и R асинхронной установки состояния "1" и "0". Сигналы на асинхронных входах переключают триггер независимо от сигналов на входах синхронного триггера. Три входа J подаются на внутренний логический элемент И. Три входа К также связаны операцией И.

Микросхема К155ТМ8 (рис. 3, б) представляет собой четыре D-триг-гера, имеющих общий тактируемый фронтом вход С. Кроме того, микросхема имеет общий инверсный вход независимой установки триггеров в нулевое состояние.

22

Лекция №3. Электронно-логическое содержимое микропроцессорных систем.

Микросхемы средней степени интеграции

К микросхемам средней степени интеграции (СИС) относят преобразователи кодов, коммутаторы, арифметические устройства, счетчики и регистры. Эти микросхемы в устройствах логического управления применяют для выполнения сложных логических функций - таких как селектирование различных функциональных блоков, циклический опрос датчиков, сравнение текущих и заданных значений сигналов, счет числа событий, хранение и передача многоразрядных кодов.

Преобразователи кодов. Эти устройства переводят одну разновидность кода в другую. Число входов и выходов у преобразователя кодов может быть не равно друг другу. Условно преобразователи кодов изображают на схемах символом х/у.

В виде СИС выпускают преобразователи цифровых сигналов четырехразрядного двоичного кода в сигналы семисегментного кода. Эти преобразователи работают совместно с семисегментными буквенно-цифровыми индикаторами. Разновидностью преобразователей кодов являются шифраторы и дешифраторы, работающие соответственно с входным или выходным унитарным кодом. Шифраторы обычно выполняют в виде микросхем, имеющих 8 входов и 3 выхода (на схемах шифраторы обозначают символом СD). Каждый выходной трехразрядный код определяет, на какой из восьми входов подан единичный сигнал.

Дешифратор имеет единичный или нулевой, в зависимости от типа СИС, сигнал только на одном из выходов, выбор которого производится комбинацией входных сигналов. Для N выходных сигналов дешифратор строят следующим образом. Формируют множество из 2N сигналов, половина из которых является входными, а остальные - их инверсиями, полученными с помощью элементов НЕ. На входы 2N элементов типа И с N выходами подают неповторяющиеся комбинации сигналов из упомянутого множества. Выходы элементов И используют в качестве выходов дешифраторов. Построенный таким образом дешифратор называют полным. Неполные дешифраторы имеют число выходов меньше, чем 2N.

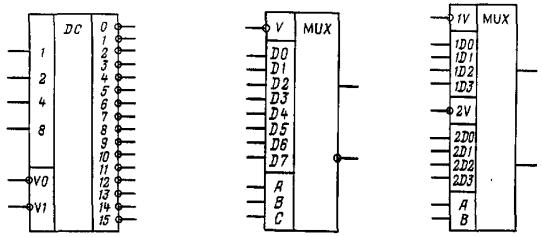

На рис. 4 показано условное изображение микросхемы К155ИДЗ, которая преобразует четырехразрядный код в код "1 из 16".

Разрешающие входы V0 и V1 можно использовать для увеличения разрядности дешифруемого кода при совместной работе нескольких дешифраторов с малой разрядностью.

Коммутаторы. К коммутаторам логических сигналов относят мультиплексоры и демультиплексоры. Мультиплексоры коммутируют сигнал с одного из многих информационных входов на единственный выход. Выбор канала передачи осуществляют сигналы на управляющих (адресных) входах. Демультиплексор коммутирует сигнал с единственного входа на один из нескольких выходов.

Мультиплексор в большинстве случаев представляет собой селектор, управляющие входы которого соединены с выходом дешифратора. В некоторых мультиплексорах, выполненных по КМОП-технологии, вместо селекторов используют управляемые ключи, имеющие общий вывод.

23

На рис. 5, а показано условное изображение микросхемы К155КП7, которая коммутирует сигнал с восьми входов на один выход. Микросхема имеет дополнительный инверсный выход и разрешающий вход V. При V= 0 трехразрядный код на адресных входах А, В, С определяет информационный вход, с которого передается сигнал на выход мультиплексора. При V= 1 на прямом выходе мультиплексора безусловно устанавливается уровень логического нуля. Мультиплексоры, выполненные в виде одной микросхемы, имеют до 16 информационных входов.

а |

б |

Рис. 4. Рис. 5. Изображение мультиплексора: Схема дешифратора а – одноканального; б – двухканального

На рис. 5, б показано условное изображение микросхемы К155КП2, содержащей два четырехвходовых мультиплексора с независимыми инверсными разрешающими входами 1V и 2V и общими двумя адресными входами А, В. Микросхема не имеет инверсных выходов у мультиплексоров.

В качестве демультиплексоров обычно используют либо мультиплексоры, выполненные по КМОП-технологии с управляемыми ключами (типа микросхемы 564КП2), либо дешифраторы с разрешающими входами (см. рис. 4).

Арифметические устройства. К группе микросхем средней степени интеграции, выполняющих арифметические операции, относят компараторы, сумматоры и арифметико-логические устройства.

Цифровые компараторы сравнивают значения двух чисел и вырабатывают единичный сигнал на одном из трех выходов ("Больше", "Равно", "Меньше"), в зависимости от соотношения между этими числами. Микросхема 564ИП2 позволяет сравнивать два четырехразрядных двоичных числа и имеет расширяющие входы, с помощью которых можно увеличивать разрядность компараторов.

Типовые микросхемы, выполняющие роль сумматоров, складывают одно-, двух- и четырехразрядные двоичные числа. Такие микросхемы имеют вход сигнала переноса в младший разряд и выход сигнала переноса из старшего разряда. Эти вход и выход служат для объединения нескольких микросхем с целью получения сумматоров повышенной разрядности. Кроме того, внешние вход и выход переноса позволяют использовать сумматоры для выполнения арифметических операций вычитания и умножения двух чисел.

24

На рис. 6. показано условное изображение микросхемы К155ИМ2, позволяющей находить двухразрядную сумму S2S1 двух чисел А2А1 и В2В1. Данный сумматор имеет вход Р0 и выход Р2 переноса.

Единичный сигнал переноса в старший разряд формируется, если результат сложения битов одноименных разрядов больше 1, т.е. если единичный сигнал возникает не более чем на одном входе сумматора.

Рис. 6. Двухразрядный сумматор.

Арифметико-логические устройства в зависимости от сигналов на управляющих входах выполняют различные операции с двумя входными числами. Например, микросхема 564ИП3 обрабатывает два четырехразрядных двоичных числа. Пять управляющих входов настраивают устройство на выполнение одной из 32 простейших арифметических и логических функций. Арифметические функции в основном представляют собой операции сложения и вычитания двух чисел.

Счетчики. Счетчики импульсов изготовляют в виде микросхем двух типов. Микросхема первого типа, называемая счетчиком-делителем, преобразует число импульсов, поступивших на счетный вход, в многоразрядный выходной код, а также вырабатывает на одном выходе единичный сигнал после поступления на вход определенного числа импульсов. Микросхема второго типа, называемая делителем, выполняет только вторую функцию.

Последовательные счетчики представляют собой последовательно соединенные счетные триггеры, причем выходной сигнал каждого триггера переключает последующий триггер, а входной сигнал подается только на первый. Совокупность выходных сигналов с триггеров представляет собой выходной код счетчика, причем первый триггер дает бит младшего разряда кода. У суммирующих счетчиков с приходом нового импульса показания увеличиваются, а у вычитающих - уменьшаются. Реверсивные счетчики позволяют вести счет в двух направлениях.

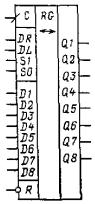

Рис.7. Обозначение двоично-десятичного счетчика кодов.

На рис.7. показано условное обозначение микросхемы К155ИЕ6, содержащей четырехразрядный двоично-десятичный счетчик. При прямом суммировании импульсов на входы "+1" и "-1" подают входной сигнал и единичный соответственно. При обратном счете поступают наоборот. Единичный сигнал на

25

входе R0 устанавливает ноль на выходах Q1, Q2, Q3, Q4. Начальное значение выходного кода, задаваемого на входах D1, D2, D3, D4, вводят при нулевом сигнале на входе С. На выходе переноса, обозначенном "≥9", в режиме сложения формируется нулевой импульс сразу после перехода выходного сигнала из состояния 1001 в состояние 0000, т.е. с приходом десятого входного импульса. На выходе заема "≤0" нулевой импульс формируется в режиме вычитания при смене состояний с 0000 на 1001. Выходы переноса и заема, соединенные с входом С, позволяют циклически вводить начальный код счетчика. Кроме того, эти выходы могут быть использованы для соединения микросхем с целью увеличения разрядности счетчика.

Для создания суммирующих счетчиков с последовательным переносом между микросхемами выход "≥9" предыдущей микросхемы соединяется с входом "+1" последующей микросхемы. Для организации счетчиков с параллельным переносом такое соединение производится через логический элемент И, на второй вход которого подается входной сигнал.

Регистры. В вычислительных устройствах широко используют регистры, представляющие собой логические узлы для хранения многоразрядного кода. Для построения регистров применяют D, RS- и JK-триггеры, причем каждый триггер служит для хранения одного бита информации. В регистрах памяти нет передачи информации от одного триггера к другому. В регистрах сдвига производят сдвиг хранимого двоичного кода по цепочке триггеров. В зависимости от направления сдвига информации регистры подразделяют на однонаправленные и реверсивные.

Рис.8. Обозначение микросхемы К155ИР13.

Условное обозначение микросхемы К155ИР13, реализующей регистр, показано на рис.8.

Микросхемы большой степени интеграции

Микросхемы большой степени интеграции (БИС) используют для построения оперативных и постоянных запоминающих устройств, предназначенных для хранения большого числа двоичных кодов.

Оперативные запоминающие устройства (ОЗУ) – (RAM - Random Access Memory, т.е. память с произвольным доступом). Эти устройства допускают запись и считывание кодов с одинаковой скоростью. После отключения источника питания

26

информация, записанная в ОЗУ, стирается. В статических ОЗУ один бит информации фиксируется в виде состояния триггера. В динамических ОЗУ значение сигнала определяют по наличию или отсутствию напряжения на электрической емкости, образующейся между выводами транзистора. Поскольку малые емкости быстро разряжаются, то динамические ОЗУ снабжают устройствами регенерации, периодически подзаряжающими емкость.

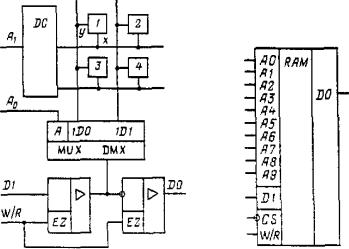

На рис.9, а показана схема ОЗУ для хранения четырех одноразрядных слов, каждое из которых запоминается в ячейках памяти 1 - 4.

а б

Рис.9. Оперативное запоминающее устройство: а –структура; б – условное изображение

Для обращения к нужной ячейке памяти, находящейся в ОЗУ (см. рис.9, а), адресная шина, состоящая в данном случае из двух линий A0 и A1 разделяется на две части. Сигнал на линии A1 через дешифратор обращается ко всем ячейкам памяти, находящимся в каком-либо горизонтальном ряду. Сигнал на линии A0 заставляет мультиплексор - демультиплексор соединить свой общий вывод только с одной ячейкой памяти, находящейся в выбранном горизонтальном ряду. При записи информации в ячейку памяти на вход W/R подается нулевой сигнал, включающий первый усилитель с тремя выходными состояниями, и сигнал D1 поступает на общий вывод мультиплексора -демультиплексора. При единичном сигнале на входе W/R сигнал с общего вывода мультиплексора - демультиплексора через второй усилитель проходит на выход D0.

На рис.9, б приведено условное изображение микросхемы К155РУ7, которая имеет десятиразрядную адресную шину и позволяет хранить 1024 одноразрядных слова. Дополнительный сигнал CS -"Выбор микросхемы" служит для включения ОЗУ в работу. Микросхема КР541РУЗ запоминает 16384 одноразрядных слова, а микросхема КР537РУ8А - 2048 восьмиразрядных слов.

Постоянные запоминающие устройства (ПЗУ) - (ROM – Read Only Memory,

т.е. память только для чтения). Эти устройства предназначены для длительного хранения информации даже после отключения источника питания. Запись информации в ПЗУ производят до установки его в цифровую систему. В так называемых масочных ПЗУ таким элементом является металлическая дорожка,

27

которая в зависимости от значения записываемого бита может формироваться или не формироваться на заключительной стадии изготовления микросхемы.

В программируемых ПЗУ роль упомянутого элемента выполняет плавкая электропроводящая перемычка, которую пережигают путем пропускания через нее большого тока при однократном программировании БИС. В перепрограммируемых (FLASH) ПЗУ роль восстанавливаемых перемычек выполняют, например, полевые транзисторы с плавающим затвором. При программировании ПЗУ транзистор "пробивают" повышенным напряжением питания, в результате чего электроны инжектируют в затвор и заряжают его. Заряд на затворе открывает транзистор. Поскольку затвор изолирован, заряд сохраняется на нем после снятия напряжения питания в течение десятков лет.

Для стирания информации БИС подвергают воздействию ультрафиолетового излучения, которое ионизируют изолирующую прослойку, что вызывает стекание заряда с затвора. Поскольку процедуры стирания информации вызывают старение изолирующей прослойки, число записей в перепрограммируемое ПЗУ ограничено. Существуют перепрограммируемые ПЗУ и с электрическим способом стирания информации. На условных обозначениях масочные, программируемые и перепрограммируемые ПЗУ с ультрафиолетовым и электрическим стиранием информации имеют символы соответственно ROM, PROM, EPROM и ЕЕРRОМ.

Распространенная большая интегральная схема ПЗУ типа К573РР12 имеет емкость в 512 восьмиразрядных слов.

Микропроцессорные комплекты больших интегральных схем

Микропроцессорные системы. Большие интегральные схемы (БИС) широко применяют при построении микропроцессоров (МП) - программно-управляемых устройств для обработки цифровой информации. Совокупность МП и других интегральных микросхем, совместимых по конструктивно-технологическому исполнению и предназначенных для совместного применения, образует микропроцессорный комплект. На базе таких комплектов конструируют разнообразные микропроцессорные системы (МП-системы), предназначенные для сбора и переработки контрольной информации и нахождения командных (управляющих) сигналов. К классу МП-систем относят микроЭВМ, состоящие из микропроцессора, запоминающих устройств на полупроводниковых элементах и устройств связи с периферийной аппаратурой. МП-системой является информационная или управляющая цифровая система, в состав которой входят микроЭВМ и устройство связи с объектом (УСО), выполняющие ограниченный набор программ, хранящихся в постоянном запоминающем устройстве (ПЗУ).

Существенное увеличение диапазона обрабатываемых чисел достигается использованием подпрограмм обработки чисел с плавающей запятой.

Во многих МП-системах функциональные блоки объединены с соответствующими контроллерами в единые модули (микропроцессорные, памяти, ввода - вывода). Каждый модуль выполняют в виде отдельной печатной платы с напаянными на нее корпусами интегральных схем. В этом случае МП-систему называют многоплатной. Если модули смонтированы на одной печатной плате, МП-

28