СПЭ и МСвП Лаб 1

.docxМинистерство образования Российской Федерации

Санкт-Петербургский государственный электротехнический

университет “ЛЭТИ”

Кафедра ЭУТ

Отчет по лабораторной работе № 1

«Изучение работы 8-миразрядных микропроцессоров (Intel 8085)».

|

|

Выполнили:

Факультет: ИБС Группа:

Проверил: Шевелько М.М.

|

|

|

|

|

|

|

|

|

|

|

|

|

Санкт-Петербург

2015

Цель работы — ознакомиться с функционированием восьмиразрядных микропроцессоров на примере выполнения команд микропроцессором Intel 8085.

Описание микропроцессора Intel 8085.

Микропроцессор Intel 8085 является типичным представителем серии восьмиразрядных однокристальных микропроцессоров, предназначенных для построения различных вычислительных и управляющих устройств. Он использует одно напряжение питания +5 В, имеет встроенный тактовый генератор, более расширенную систему прерываний.

Схема расположения

выводов Intel 8085 представлена на

рис. 1.1. Здесь AD0–AD7 – мультиплексированная

шина данных и 8 младших разрядов

адреса;

A8–A15 – старшие 8 разрядов шины

адреса; ALE – разрешение фиксации

адреса; S0, S1, IO/M – состояния

машинного цикла (см. таблицу), RD –

управление чтением; WR –

управление записью; READY – вход сигнала,

низкий уровень которого задерживает

работу процессора на целое число циклов;

HOLD – вход сигнала запроса использования

шин адреса и данных; HLDA – выход сигнала,

высокий уровень которого указывает,

что процессор освободит шины в

следующем цикле; INTR, RST5.5, RST6.5, RST7.5,

TRAP – входы сигналов прерываний;

INTA – выходной сигнал

подтверждения прерывания; RESET IN –

вход сигнала сброса (устанавливает

счетчик команд в нуль и сбрасывает

триггеры разрешения прерывания

и подтверждения захвата); RESET

OUT – выход сигнала, указывающего на

то, что произведен сброс центрального

процессора; X1 X2 – входы для подключения

частотозадающих LC- или RC‑цепей

или кварцевого резонатора или внешнего

генератора; CLK – выход тактовых

импульсов; SID – линия последовательных

входных данных; SOD – линия последовательных

выходных данных; VCC – питание + 5 В;

GND – земля.

Рисунок 1.1

Описание лабораторного стенда

Схема стенда представлена на рис. 1.2. Здесь CPU – микропроцессор Intel 8085, линии шины данных которого AD0–AD7 через резисторы R1–R8 подсоединены к шине питания + 5 В. Высокий уровень на входных линиях CPU (READY, RESET IN, TRAP, INTR, RST5.5, RST6.5, RST7.5, HOLD) также получен путем подсоединения их через резисторы к шине питания. Вывод S1 подведен к клемме “СИНХР.” для синхронизации осциллографа. Сигнал тактовой частоты вырабатывается внутренним генератором микропроцессора, для чего к входам Х1, Х2 подключен кварцевый резонатор Q. Сброс CPU осуществляется нажатием кнопки К (подача нулевого уровня на вход RESET IN).

Рисунок 1.2

Обработка результатов

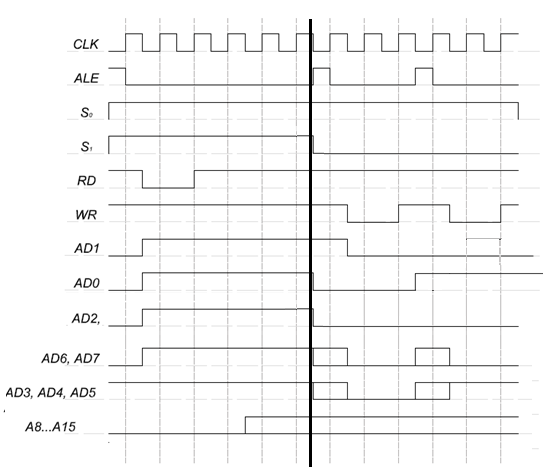

В ходе лабораторной работы были сняты временные диаграммы следующих сигналов: CLK, S1, S0, RD, WR, ALE, AD0–AD7, А8–А15. Они представлены на рисунке 1.3 Временные диаграммы были сняты с соблюдением временных соотношений между фронтами этих сигналов.

Рисунок 1.3

CLK – выход тактовых импульсов;

ALE – разрешение фиксации адреса. Этот сигнал появляется с началом машинного цикла. При изменении уровня этого сигнала, разрешается / запрещается запись на шину адреса данных (AD0..AD7). Сигналы шины адреса данных появляются с задержкой на полтакта;

S0, S1, IO/M – состояния машинного цикла. Анализируя временные диаграммы и таблицу 1, можно сделать вывод, что в первых 5,5 тактах происходит выборка кода операции / подтверждение прерывания, во время последующих тактов – запись в память / вывод (вывод S1 используется для синхронизации с осциллографом).

RD – управление чтением; WR – управление записью;

A8–A15 – старшие 8 разрядов шины адреса.

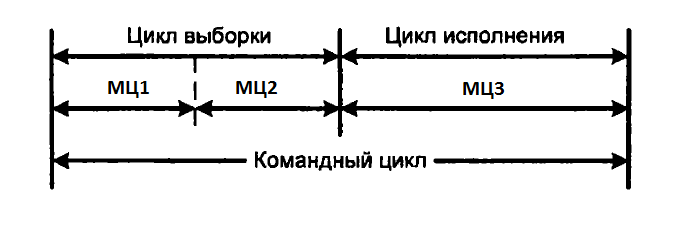

Каждая команда в МП выполняется на протяжении командного цикла (КЦ). КЦ состоит из цикла выборки команды и цикла выполнения команды.

Продолжительность цикла выборки команды зависит от формата команды (количества байт в машинном коде команды). Команда занимает от 1 до 3 байт в программной памяти. В связи с этим продолжительность командного цикла различна для различных команд.

Рисунок 1.4

Интервал, на протяжении которого осуществляется одно обращение процессора к памяти или к внешнему устройству, определяется как машинный цикл МЦ. КЦ обычно состоит от 1 до 5 МЦ в зависимости от типа команды.

В приведенном на рисунке 1.4 примере цикл выборки состоит из двух МЦ: МЦ1 и МЦ2, а цикл исполнения – из одного МЦ: МЦ3.

МЦ, в свою очередь, разбивается на некоторое количество машинных тактов (Т), на протяжении каждого из которых выполняется элементарное действие (микрооперация) в процессоре. МЦ обычно состоит из 3 - 5 Т.

По сигналу ALE можно судить о количестве МЦ, в нашем случае КЦ состоит из 3-х МЦ (рисунок 1.5). Как видно из рисунка МЦ1 состоит из 5,5 тактов, МЦ2 = 2,5Т, а МЦ3 = 2,5Т.

Рисунок 1.5

В данном случае МП за время выполнения команды находится в 2-х состояниях: 1 – S0=1, S1=1 – состояние выборки кода операции; 2 - S0=1, S1=0 – состояние записи в память (рисунок 1.6).

Рисунок 1.6

Данные входят в МП и покидают его через AD0-AD7. Эта шина передает адрес, когда линия управления ALE получает высокий сигнал (1) и данные низкий сигнал (0).

Рассмотрим состояние 1 (Рисунок 1.7):

При высоком уровне сигнала ALE на мультиплексированной шине (AD0-AD7) и шине адреса (A8-A15) находится адрес начала отсчета считывания. При изменении уровня сигнала управляющей шины ALE на низкий на AD0-AD7 появляются данные, которые будут считаны. Считывание данных происходит при низком уровне сигнала RD.

Состояние 2 (Рисунок 1.7):

При высоком уровне сигнала ALE на мультиплексированной шине (AD0-AD7) и шине адреса (A8-A15) находится адрес места записи данных в память. При изменении уровня сигнала управляющей шины ALE на низкий на AD0-AD7 появляются данные, которые будут записаны в память. Запись данных происходит при низких уровнях сигнала WR. Операция записи происходит в 2 и 3 машинных циклах.

Рисунок 1.7

При выполнении первого МЦ происходит операция чтения кода команды, при высоком уровне сигнала ALE, на шине (AD0-AD7) и шине адреса (A8-A15) находится адрес начала отсчета считывания: 0001 1100 0000 00002. При изменении уровня сигнала управляющей шины ALE на низкий на AD0-AD7 появляются данные – 1111 11112 = FFh которые будут считаны.

При высоком уровне сигнала ALE на шине (AD0-AD7) и шине адреса (A8-A15) находится адрес места записи данных в память. Адрес второго МЦ – 1011 1111 1111 11112. Адрес третьего МЦ – 0011 1111 1111 11112. При изменении уровня сигнала управляющей шины ALE на низкий на AD0-AD7 появляются данные, которые будут записаны в память. Данные записанные при выполнении операции WR на 2-ом МЦ – 0000 00002. Данные записанные при выполнении операции WRна 3-ем МЦ – 1001 11002.

Выводы: Ознакомились со схемой 8-миразрядного микропроцессора Intel 8085, сняли и проанализировали временные диаграммы сигналов на выходах процессора.