лаба 2.1

.docx|

|

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ «Белгородский Государственный Технологический Университет им. В.Г. Шухова» (БГТУ им. В.Г. Шухова) ИИТУС, Кафедра ТК |

||

|

«Информационные технологии» |

|||

|

Лабораторная работа № 2.1 «Элементы цифровой схемотехники» |

|||

|

|

|||

|

Выполнил: студент УС-11 Татаринов А.Е. Проверил: ст. преподават. Крюков А.В.

|

Отметка о выполнении

дата, роспись |

Отметка о защите

дата, роспись |

|

Любая область человеческих знаний,

основанная на синтезе, на изобретении,

неразрывно связана с понятием искусства.

М. В. Гальперин

Вариант №6

Цель работы: изучение логических операций и правил их преобразований. Получение навыков практической работы по моделированию цифровых схем, состоящих из логических вентилей. Ознакомление с различными способами описания логики работы логического устройства – таблицами истинности, временными диаграммами, аналитическими функциями, цифровыми схемами.

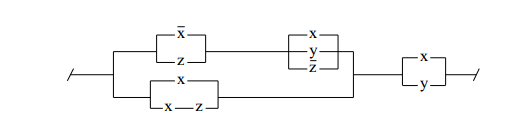

ЗАДАЧА 1

Постановка задачи: Для заданной переключательной схемы записать соответствующую функции проводимости. Построить аналог схемы, предварительно упростив ее.

Решение:

-

Составим логическое выражения для данной схемы:

В результате получим схему:

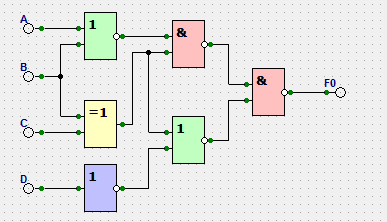

ЗАДАЧА 2

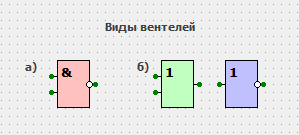

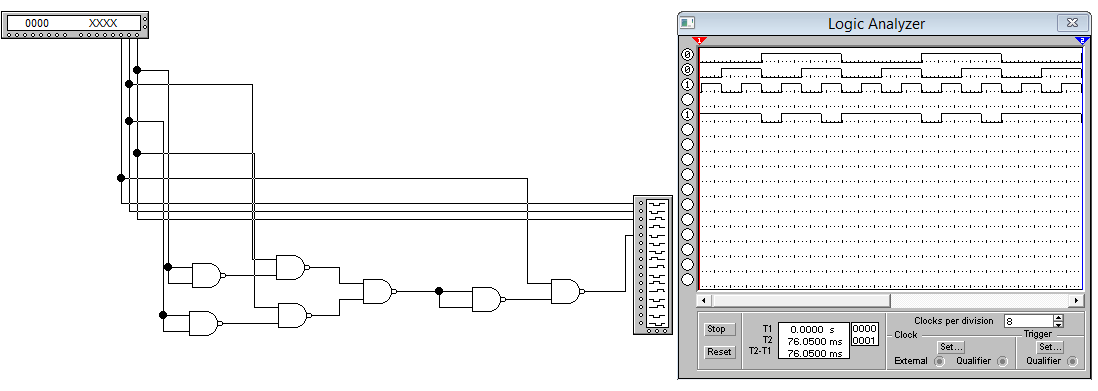

Постановка задачи: Задана логическая схема. 2.1. Определить, какие комбинации входных сигналов приводят к появлению «1» на выходе схемы, составив и решив соответствующее логическое уравнение. 2.2. Построить эквивалентные схемы, содержащие только указанные виды вентилей (отдельно для блоков вида а) и блоков вида б) ) предварительно максимально упростив логическую функцию, соответствующую данной цифровой схеме. 2.3. Проверить равносильность исходной и полученных в 2.2 схем, смоделировав их в среде Electronics Workbench и построив соответствующие временные диаграммы.

Решение:

Исходная логическая схема:

2.1

1) Запишем соответствующее логическое выражение и упростим его:

2) По полученному выражению составим систему:

По данной системе найдем количество решений:

-

B=0, C=0, D=0

-

B=0, C=1, D=0

-

B=0, C=1, D=1

-

B=1, C=0, D=0

-

B=1, C=0, D=1

-

B=1, C=1, D=0

Т.к. значение А не влияет на решение данного выражения, то ее значения можно не рассматривать.

6 решения.

2.2

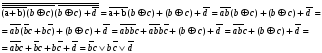

А) преобразуем данное выражения используя только штрих Шеффера:

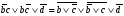

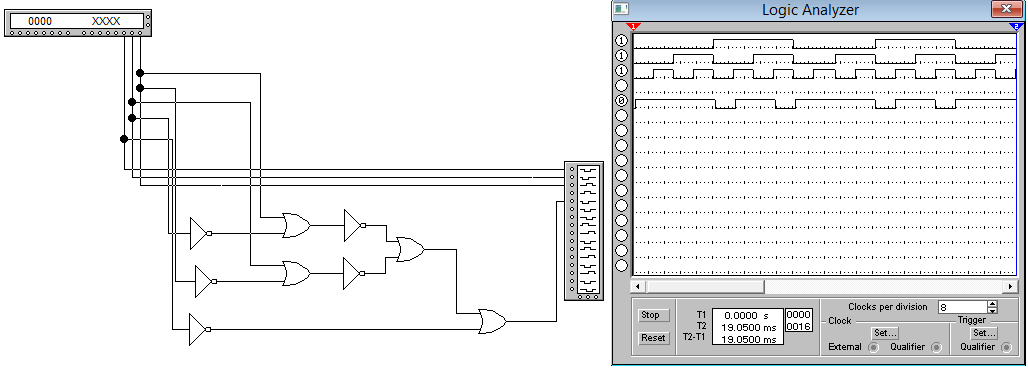

Логическая схема:

Б) преобразуем данное выражение используя только операции or и not:

Логическая схема:

Конечная логическая схема:

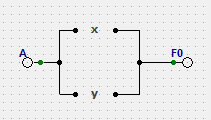

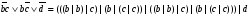

ЗАДАЧА 3

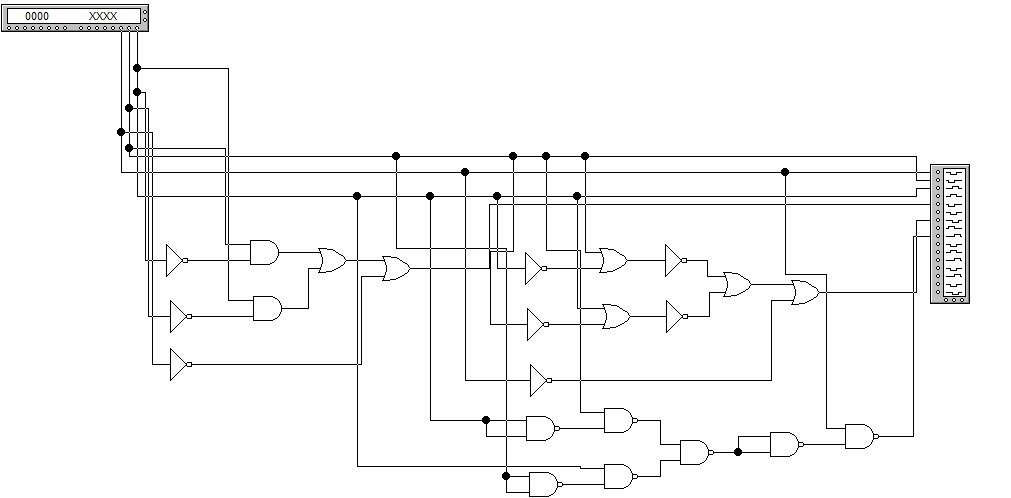

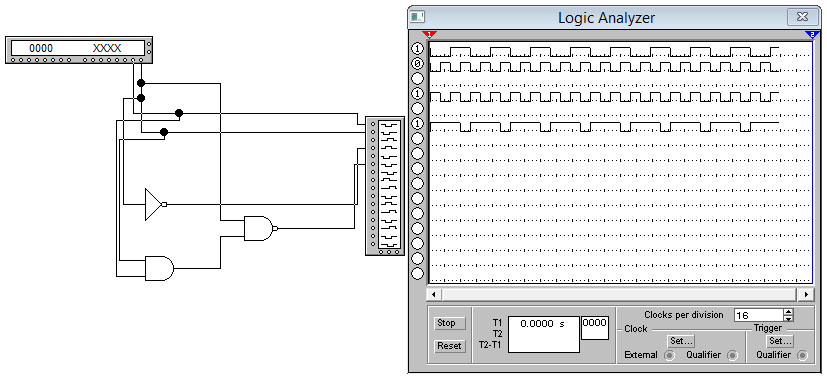

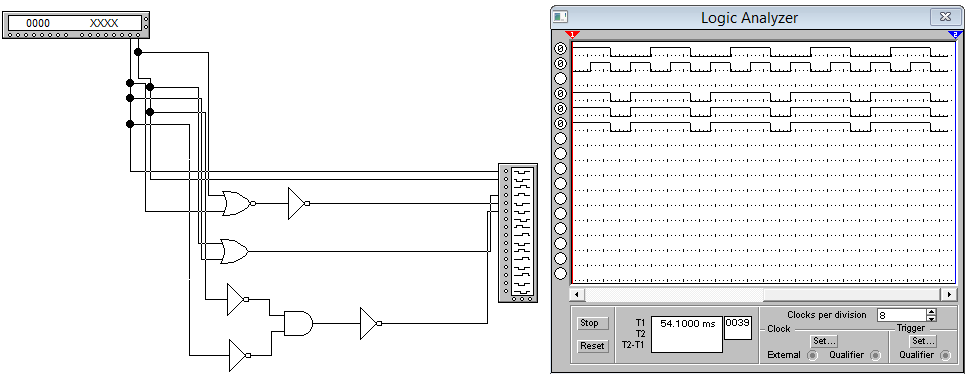

Постановка задачи: Используя пакет Electronics Workbench спроектировать схемы, соответствующие обоим частям тождества, и с помощью соответствия временных диаграмм доказать их тождество. В отчет включить соответствующие цифровые схемы и диаграммы входных и выходных сигналов каждой из выполненных схем. Докажите данные тождества и математически, применяя законы алгебры логики.

Решение:

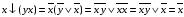

Исходные тождества:

-

Упростим обе части выражений и сравним их:

Данное тождество верно. Построим логическую схему:

Рассмотрим второе выражение:

Полученные выражения равны. Составим логическую схему:

Вывод: Следуя цели данной лабораторной работы, были изучены логические операции и правила их преобразования. Получены навыки практической работы по моделированию цифровых схем, состоящих из логических вентилей. Был ознакомлен с различными способами описания логики работы логического устройства – таблицами истинности, временными диаграммами, аналитическими функциями, цифровыми схемами.

-