лаба 2.2

.docx|

|

МИНИСТЕРСТВО ОБРАЗОВАНИЯ И НАУКИ РОССИЙСКОЙ ФЕДЕРАЦИИ ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ «Белгородский Государственный Технологический Университет им. В.Г. Шухова» (БГТУ им. В.Г. Шухова) ИИТУС, Кафедра ТК |

||

|

«Информационные технологии» |

|||

|

Лабораторная работа № 2.2 «Проектирование вычислительных устройств» |

|||

|

|

|||

|

Выполнил: студент УС-11 Татаринов А.Е. Проверил: ст. преподават. Крюков А.В.

|

Отметка о выполнении

дата, роспись |

Отметка о защите

дата, роспись |

|

«Мир не подчиняется больше силе оружия,

энергии или денег. Он управляется единичками и ноликами,

битами данных, всего лишь электронами.»

Вариант №13

Цель работы: получение навыков практической работы по моделированию цифровых схем, состоящих из логических вентилей. Ознакомление с различными способами описания логики работы логического устройства – таблицами истинности, временными диаграммами, аналитическими функциями, цифровыми схемами.

ЗАДАЧА 1

Постановка задачи: Спроектировать цифровую схему для сравнения многоразрядных двоичных чисел, состоящую из простейших элементов И, ИЛИ, НЕ.

Заданное условие: Сравнение одноразрядных двоичных чисел А, В и С с выходным сигналом:

Решение: 1. Построим таблицу истинности

2. выполним синтез

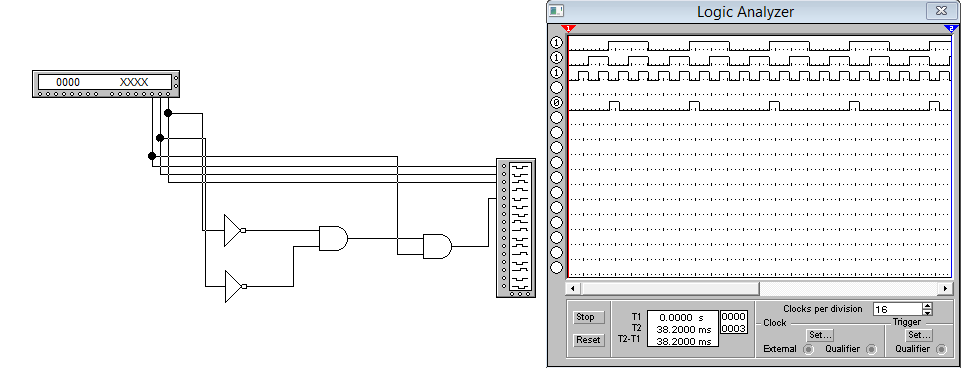

3. Построим схему по данному выражению:

ЗАДАЧА 2

Постановка задачи: Спроектировать цифровую схему, реализующую указанное действие. Рассмотреть разные подходы (если это возможно) к синтезу такой схемы – с использованием блоков полусумматора/сумматора, и с использованием лишь простейших вентилей.

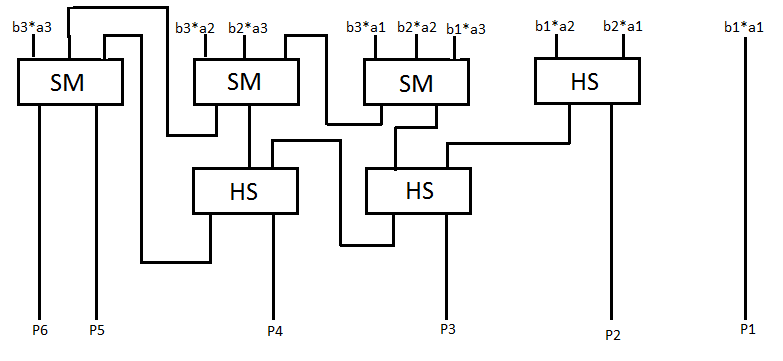

Заданное условие: Спроектировать множительный блок, предназначенный для умножения двух двухразрядных двоичных чисел.

Решение:

-

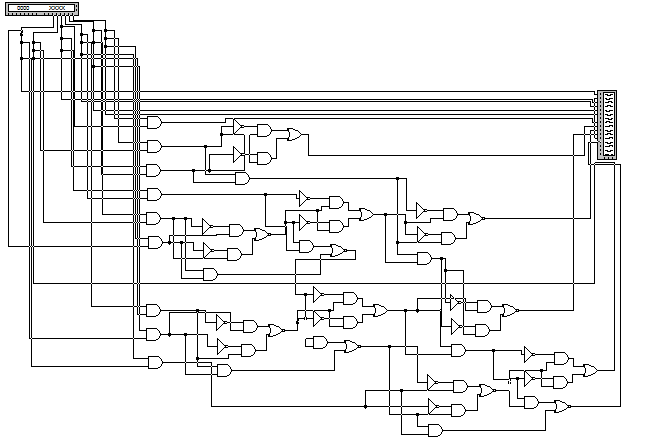

Составим схему по которой спроектируем данную задачу:

-

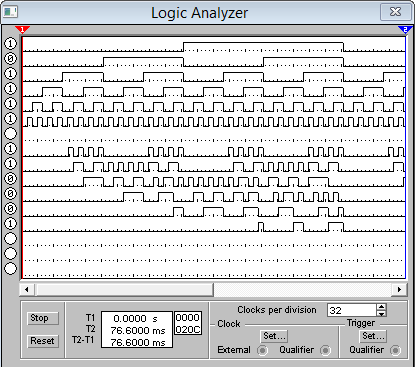

Составим цифровую схему:

-

Построим схему используя простейшие блоки:

ЗАДАЧА 3

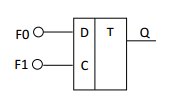

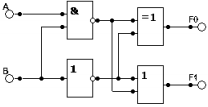

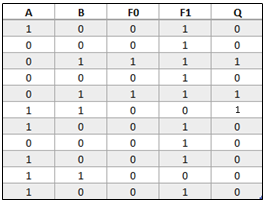

Постановка задачи: Выходные сигналы заданной цифровой схемы F0 и F1 подаются на входы D-триггера так как показано на рисунке:

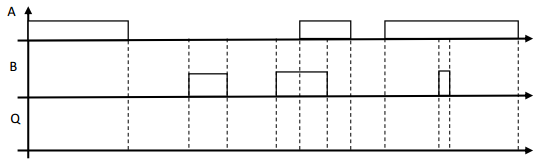

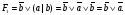

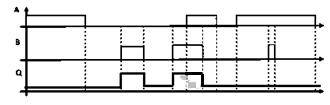

Построить временную диаграмму для выходного сигнала Q (принять исходное значение выходного сигнала Q = 0) при заданных значениях входных сигналов А и В.

Заданное условие:

Решение:

-

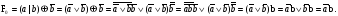

Преобразуем заданную логическую схему в выражение и упростим его:

-

По заданной временной диаграмме строим таблицу истинности и заполним столбцы F0 и F1:

-

Используя D-триггер заполним выходной столбец Q:

-

Строим временную диаграмму по получившимся значениям:

Вывод: были изучены навыки практической работы по моделированию цифровых схем, состоящих из логических вентилей. Был ознакомлен с различными способами описания логики работы логического устройства – таблицами истинности, временными диаграммами, аналитическими функциями, цифровыми схемами.

-