Рисунки к конспектам (11.10.10)

.doc

Таблица 6 – Коды условий для команд управления

|

УУУ |

Мнемокод |

Условия |

|

000 |

NZ |

Неравенство нулю |

|

001 |

Z |

Равенство нулю |

|

010 |

NC |

Отсутствие переноса |

|

011 |

C |

Наличие переноса |

|

100 |

PO |

Нечетность |

|

101 |

PE |

Четность |

|

110 |

P |

Плюс |

|

111 |

M |

Минус |

|

S |

Z |

0 |

AC |

0 |

P |

1 |

C |

|

бит 7 |

|

|

|

|

|

|

бит 0 |

Рисунок 6 – Формат регистра флажков RF

Рисунок 7 – Схемы, поясняющие выполнение сдвигов микропроцессором

Рисунки и таблицы к теме:

«ПРОГРАММИРОВАНИЕ МП»

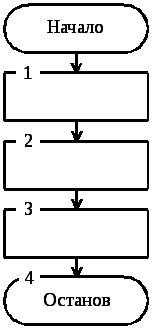

Рисунок 15 – Схема алгоритма инвертирования содержимого ЯП

Таблица 7 – Программа инвертирования содержимого ЯП на языке Ассемблера при использовании прямой адресации

|

Адрес |

Метка |

Команда |

Операнд |

Машинный код |

Комментарий |

|

0800 |

|

LDA |

0B00 H |

3A 00 0B |

; чтение числа из памяти |

|

0803 |

|

CMA |

|

2F |

; инвертирование числа |

|

0804 |

|

STA |

0B01 H |

32 01 0B |

; запись числа в память |

|

0807 |

|

HLT |

|

76 |

; останов |

Таблица 8 – Программа инвертирования содержимого ЯП на языке Ассемблера при использовании косвенной регистровой адресации

|

Адрес |

Метка |

Команда |

Операнд |

Машинный код |

Комментарий |

|

0800 |

|

LXI |

H,0B00H |

21 00 0B |

; запись в пару регистров ; H-L адреса числа |

|

0803 |

|

MOV |

A,M |

7E |

; чтение числа из памяти |

|

0804 |

|

CMA |

|

2F |

; инвертирование числа |

|

0805 |

|

INX |

H |

23 |

; увеличение на 1 адреса ; числа |

|

0806 |

|

MOV |

M,A |

77 |

; запись числа в память |

|

0807 |

|

HLT |

|

76 |

; останов |

Рисунок 16 – Схема алгоритма циклической программы суммирования однобайтных чисел

Таблица 9 – Циклическая программа суммирования однобайтных чисел на языке Ассемблера

|

Адрес |

Метка |

Команда |

Операнд |

Машинный код |

Комментарий |

|

0800 |

|

LXI |

H,0A00H |

21 00 0A |

; адрес первого слагаемого |

|

0803 |

|

MVI |

B,05H |

06 05 |

; количество слагаемых |

|

0805 |

ADDB: |

XRA |

AC |

AF |

; обнуление регистра AC |

|

0806 |

|

MOV |

C,AC |

4F |

; обнуление регистра C |

|

0807 |

M1: |

ADD |

M |

86 |

; суммирование |

|

0808 |

|

JNC |

M2 |

D2 0C 08 |

; условный переход на ; M2, если (TC) = 0 |

|

080B |

|

INR |

C |

0C |

; увеличение содержимого ; регистра C на единицу |

|

080C |

M2: |

INX |

H |

23 |

; увеличение содержимого ; пары регистров H-L на ; единицу |

|

080D |

|

DCR |

B |

05 |

; уменьшение на единицу ; содержимого счетчика ; циклов |

|

080E |

|

JNZ |

M1 |

C2 07 08 |

; условный переход на M1, если (TZ) = 0 |

|

0811 |

|

HLT |

|

76 |

; останов |

Таблица 10 – Программа суммирования массива однобайтных чисел на языке Ассемблера, содержащая подпрограмму

|

Адрес |

Метка |

Команда |

Операнд |

Машинный код |

Комментарий |

|

0800 |

|

LXI |

H,0A00H |

21 00 0A |

; адрес первого слагаемого |

|

0803 |

|

MVI |

B,05H |

06 05 |

; количество слагаемых |

|

0805 |

|

CALL |

ADDB |

CD 09 08 |

; вызов подпрограммы ; сложения |

|

0808 |

|

HLT |

|

76 |

; останов |

|

0809 |

ADDB: |

XRA |

AC |

AF |

; обнуление регистра AC |

|

080A |

|

MOV |

C,AC |

4F |

; обнуление регистра C |

|

080B |

M1: |

ADD |

M |

86 |

; суммирование |

|

080C |

|

JNC |

M2 |

D2 10 08 |

; условный переход на ; M2, если (TC) = 0 |

|

080F |

|

INR |

C |

0C |

; увеличение содержимого ; регистра C на единицу |

|

0810 |

M2: |

INX |

H |

23 |

; увеличение содержимого ; пары регистров H-L на ; единицу |

|

0811 |

|

DCR |

B |

05 |

; уменьшение на единицу ; содержимого счетчика ; циклов |

|

0812 |

|

JNZ |

M1 |

C2 0B 08 |

; условный переход на M1, если (TZ) = 0 |

|

0815 |

|

RET |

|

C9 |

; возврат в основную ; программу |

«ОБЩИЕ СВЕДЕНИЯ И ПРИНЦИПЫ ОРГАНИЗАЦИИ ОДНОКРИСТАЛЬНЫХ МИКРОКОНТРОЛЛЕРОВ»

Рисунок

1 – Структурная схема микроконтроллера

PIC16F84

Рисунок

1 – Структурная схема микроконтроллера

PIC16F84

Рисунок 2 – Условное графическое обозначение микроконтроллера PIC16F84

Таблица 1 – Назначение выводов ОМК PIC16F84

|

Наименование |

Номер |

Тип |

Логические уровни |

Назначение |

|

1 |

2 |

3 |

4 |

5 |

|

|

|

|

|

PORTA является двунаправленным портом ввода/вывода |

|

RA0 |

17 |

I/O |

TTL |

|

|

RA1 |

18 |

I/O |

TTL |

|

|

RA2 |

1 |

I/O |

TTL |

|

|

RA3 |

2 |

I/O |

TTL |

|

|

RA4/T0CKI |

3 |

I/O |

ST |

Выход с открытым стоком/вход таймера TMR0 |

|

|

|

|

|

PORTB является двунаправленным портом ввода/вывода. Имеет на всех выводах программно включаемые подтягивающие резисторы |

|

RB0/INT |

6 |

I/O |

TTL/ST(1) |

Вход внешних прерываний |

|

RB1 |

7 |

I/O |

TTL |

|

|

RB2 |

8 |

I/O |

TTL |

|

|

RB3 |

9 |

I/O |

TTL |

|

|

RB4 |

10 |

I/O |

TTL |

Прерывание по изменению состояния |

|

RB5 |

11 |

I/O |

TTL |

Прерывание по изменению состояния |

Окончание таблицы 1

|

1 |

2 |

3 |

4 |

5 |

|

RB6 |

12 |

I/O |

TTL/ST(2) |

Прерывание по изменению состояния, тактирование при программировании |

|

RB7 |

13 |

I/O |

TTL/ST(2) |

Прерывание по изменению состояния, данные при программировании |

|

|

4 |

I |

ST |

Вход сброса/напряжение программирования. Сброс низким уровнем |

|

OSC1/CLKIN |

16 |

I |

ST/CMOS(3) |

Вход генератора/внешняя тактовая частота |

|

OSC2/CLKOUT |

15 |

0 |

– |

Выход генератора. Подключается к резонатору. В режиме RC-генератора выход 1/4 тактовой частоты OSC1 |

|

|

14 |

P |

– |

Положительное напряжение питания |

|

|

5 |

P |

– |

Общий вывод |

|

Примечания 1 – I – вход, O – выход, I/O – вход/выход, P – питание, TTL – вход TTL, ST – вход с триггером Шмитта. 2 – Буфер является триггером Шмитта при использовании в режиме последовательного программирования. 3 – Буфер является триггером Шмитта при использовании в режиме последовательного программирования. |

||||

Рисунок 3 – Временные диаграммы тактирования и выполнения команд

Рисунок 4 – Организация памяти программ и стека

-

Регистры

00h

Косвенный адрес (*)

Косвенный адрес (*)

80h

01h

TMR0

OPRION

81h

02h

PCL

PCL

82h

03h

STATUS

STATUS

83h

04h

FSR

FSR

84h

05h

PORTA

TRISA

85h

06h

PORTB

TRISB

86h

07h

87h

08h

EEDATA

EECON1

88h

09h

EEADR

EECON2(*)

89h

0Ah

PCLATH

PCLATH

8Ah

0Bh

INTCON

INTCON

8Bh

0Ch

68 регистров

Отображаются

8Ch

2Fh

общего

назначения

(ОЗУ)

на банк 0

AFh

30h

B0h

4Fh

CFh

Банк 0

Банк 1

Примечания

-

Символ (*) означает нефизический адрес.

-

Символ

означает, что адресное пространство

не используется , содержимое считывается

как "0".

означает, что адресное пространство

не используется , содержимое считывается

как "0".

Рисунок 5 – Организация памяти данных PIC16F84

Таблица 2 – Описание разрядов регистра STATUS

|

Регистр STATUS |

Адрес: |

03h, |

83h |

Состояние по включению питания: |

0001 |

1XXX |

||||||||||||

|

R/W |

R/W |

R/W |

R |

R |

R/W |

R/W |

R/W |

|||||||||||

|

IRP |

RP1 |

RP0 |

|

|

Z |

DC |

C |

|||||||||||

|

бит 7 |

бит 0 |

|||||||||||||||||

|

|

|

Бит является флагом переноса для команд сложения ADDWF, ADDLW и инверсным флагом заёма для команд вычитания SUBWF, SUBLW. Бит устанавливается в "1" в командах сложения ADDWF и ADDLW, если в результате операции из старшего разряда произошёл перенос (результат больше 0FFh). При выполнении команд сдвига RRF, RLF бит загружается из младшего или старшего бита сдвигаемого регистра соответственно. Вычитание осуществляется путём прибавления дополнительного кода второго операнда. Бит устанавливается в "1" в командах вычитания SUBWF и SUBLW, если при вычитании не произошло заёма (результат больше или равен 0) |

||||||||||||||||

|

|

|

|||||||||||||||||

|

C |

(Carry/Borrow) Перенос/Заём |

|||||||||||||||||

|

DC |

(Decimal Carry/Borrow) Десятичный перенос/Заём |

Бит устанавливается в "1" в командах ADDWF и ADDLW, если произошёл перенос из бита 3 результата. Бит устанавливается в "1" в командах вычитания SUBWF и SUBLW, если при вычитании не произошло заёма из бита 4 |

||||||||||||||||

|

Z |

(Zero) Ноль |

Бит устанавливается в "1", если результат арифметической или логической операции равен нулю |

||||||||||||||||

|

|

(Power down) Выключение питания |

Бит устанавливается в "1" по включению питания или по команде CLRWDT. Бит сбрасывается в "0" по команде SLEEP |

||||||||||||||||

|

|

(Time-out) Тайм-аут |

Бит устанавливается в "1" по включению питания, а также командами CLRWDT и SLEEP. Бит сбрасывается в "0" по срабатыванию сторожевого таймера |

||||||||||||||||

|

|

(Register Bank Select) |

Биты RP0, RP1 выбирают одну из четырёх страниц памяти данных: |

||||||||||||||||

|

|

|

RP1 |

RP0 |

: |

|

|||||||||||||

|

RPO |

Выбор страницы памяти данных |

0 |

0 |

: |

страница 0 (000h…07Fh) |

|||||||||||||

|

RP1 |

0 |

1 |

: |

страница 1 (080h…0FFh) |

||||||||||||||

|

|

1 |

0 |

: |

страница 2 (100h…17Fh) |

||||||||||||||

|

|

|

1 |

1 |

: |

страница 3 (180h…1FFh) |

|||||||||||||

|

|

|

Для PIC16F84 используется только бит RP0. Бит RP1 должен быть установлен в 0 |

||||||||||||||||

|

IRP |

Не используется |

Не используется. Бит должен быть установлен в "0" |

||||||||||||||||

|

Примечание – R – только чтение, R/W – чтение и запись. |

||||||||||||||||||