- •Синтез цифровых схем c памятью

- •1. Анализ и синтез rs-триггера

- •Условия работы триггера

- •Диаграмма Вейча для таблицы переходов триггера

- •Синтез электрической функциональной схемы

- •Порядок выполнения лабораторной работы

- •Отчет должен содержать

- •2. Анализ и синтез d-триггера и t-триггера

- •Синтез электрической функциональной схемы

- •Порядок выполнения лабораторной работы

- •Отчет должен содержать

- •3. Анализ и синтез сдвигающего регистра

- •Синтез электрической функциональной схемы

- •Порядок выполнения лабораторной работы

- •Отчет должен содержать

- •4. Анализ и синтез двоичного счетчика

- •Синтез электрической функциональной схемы

- •Порядок выполнения лабораторной работы

- •Отчет должен содержать

- •5. Анализ и синтез накапливающего сумматора

- •Синтез электрической функциональной схемы

- •Порядок выполнения лабораторной работы

- •Отчет должен содержать

Лабораторная работа

Синтез цифровых схем c памятью

1. Анализ и синтез rs-триггера

Цель работы изучение принципов построения RS-триггера путем осуществления следующих действий:

составление таблицы истинности работы RS-триггера;

составление логического выражения в соответствии с составленной таблицей истинности и его минимизация;

составление схемы электрической функциональной синтезируемого устройства в соответствии с составленным логическим выражение;

проверка работоспособности схемы по таблице истинности;

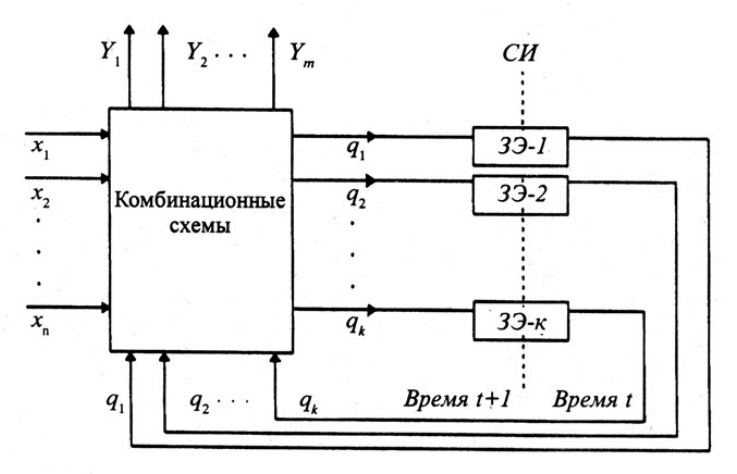

Более сложными преобразователями информации после комбинационных являются схемы с памятью. Наличие памяти в схеме позволяет запоминать промежуточные состояния обработки и учитывать их значения в дальнейших преобразованиях. Выходные сигналыY = (у1, у2,..., уm) в схемах данного типа формируются не только по совокупности входных сигналовХ = (х1, х2..., хп), но и по совокупности состояний схем памятиQ◦=◦(q1,◦q2...,◦qп). При этом различают текущий дискретный момент времениtи последующий (t+1) момент времени (рис. 1. 1).

Рис. 1.1. Обобщенная структура схемы с памятью

Передача значения Qмежду моментами времениtи (t+1) осуществляется обычно с применением двухступенчатой памяти и синхронизирующих импульсов (СИ).

В качестве простейшего запоминающего элемента в современных ЭВМ используют триггеры. Самая простейшая схема триггера (RS-триггер) может быть синтезирована по общим правилам. В данном случае для этого необходимо построить автомат памяти - триггер, имеющий вход R(Reset - сброс), для установки элемента в «нулевое состояние» и входS(Set - установка) - для установки элемента в «единичное» состояние. При отсутствии сигналовR=S=0элемент должен сохранять свое состояние до тех пор, пока не будут получены новые сигналы на входеRилиS.

Условия работы триггера могут быть показаны в виде таблицы переходов, представляющей собой модификацию таблицы истинности. Наиболее простой вид она имеет для автомата, описываемого системой уравнений автомата Мура.

Таблица 1. 1

Условия работы триггера

-

Входы

Выход

R

S

qt

Состояние qt+1

Режим

0

0

0

0

Хранение

0

0

1

1

Хранение

1

0

0

0

Установка 0

1

0

1

0

Установка 0

0

1

0

1

Установка 1

0

1

1

1

Установка 1

1

1

0

?

Запрещенное состояние

1

1

1

?

Запрещенное состояние

Содержание таблицы расшифровывается следующим образом. Элемент памяти может сохранять значение qt=0 илиqt=1 в зависимости от установки ранее установленного состояния. При отсутствии входных сигналов на входах R и S (R=0 и S=0) значенияqt+lв первой строке таблицы в точности повторяют значенияqt. При поступлении сигнала R=l (сигнала установки «нуля») элемент независимо от своего состояния принимает значение, равное нулю,qt+l= 0. Если же на вход S поступает сигнал установки «единицы» (S=l), тоqt+l=l независимо от предыдущего состоянияqt. Одновременное поступление сигналов на входы R и S является запрещенной ситуацией, так как она может привести к непредсказуемому состоянию. В схемах формирования сигналов R и S должны быть предусмотрены блокировки, исключающие их совпадения, S=R=1.

Для таблицы переходов может быть построена диаграмма Вейча (табл. 1.2).

Таблица 1.2