- •7. Примеры электронных устройств

- •7.1 Формирование временных задержек

- •7.1.1 Формирование временной задержки на rc-цепочке

- •7.1.2 Формирование временной задержки на операционных усилителях

- •7.1.3 Синтез таймера

- •7.1.4 Формирование временной задержки защитных устройств

- •7.2 Схема управления пассажирским лифтом

- •7.3 Надежность электронной аппаратуры

- •7.3.1 Основные понятия теории надежности

- •7.3.2 Надежность элементов

- •7.3.3 Надежность аппаратуры без восстановления

- •7.3.4 Надежность аппаратуры с восстановлением

- •Литература

7. Примеры электронных устройств 157

7.1 Формирование временных задержек 157

7.1.1 Формирование временной задержки на RC-цепочке 157

7.1.2 Формирование временной задержки на операционных усилителях 158

7.1.3 Синтез таймера 159

7.1.4 Формирование временной задержки защитных устройств 160

7.2 Схема управления пассажирским лифтом 163

7.3 Надежность электронной аппаратуры 165

7.3.1 Основные понятия теории надежности 165

7.3.2 Надежность элементов 165

7.3.3 Надежность аппаратуры без восстановления 166

7.3.4 Надежность аппаратуры с восстановлением 167

Литература 169

7. Примеры электронных устройств

7.1 Формирование временных задержек

7.1.1 Формирование временной задержки на rc-цепочке

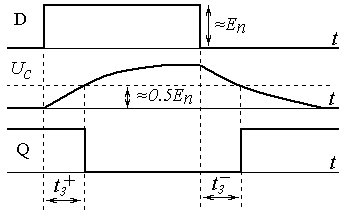

Элементы КМОП логики обладают большим входным сопротивлением, поэтому на ней можно построить временные задержки, используя обычные RC-цепи. На рис. 7. 1, а приведена схема такой временной задержки, а на рис. 7. 1, б ее временные диаграммы.

а) б)

Рис. 7. 1. Формование временной задержки на RC-цепочке

Уровни выходного сигнала КМОП логики близки к напряжению питания (при единичном сигнале) и к нулевому напряжению (при нулевом логическом сигнале). Порог переключения примерно равен половине напряжения питания.

При перепаде входного сигнала 0-1, конденсатор заряжается через резистор R1, напряжение на конденсаторе определяе6тся следующим уравнением

![]() ,

где

,

где

![]() . (7.1)

. (7.1)

При

![]() уравнение (7.1) примет вид

уравнение (7.1) примет вид

![]() ,

отсюда

,

отсюда

![]() и

и

![]() . (7.2)

. (7.2)

При перепаде входного сигнала 1-0, конденсатор разряжается через резистор R2, процесс симметричен заряду, время задержки равно

![]() ,

где

,

где

![]() . (7.3)

. (7.3)

Если задержки на включение и выключение должны быть одинаковы, то достаточно одного резистора без диодов. Схемы с RC-цепями формируют стабильные выдержки длительностью не превышающие нескольких секунд.

7.1.2 Формирование временной задержки на операционных усилителях

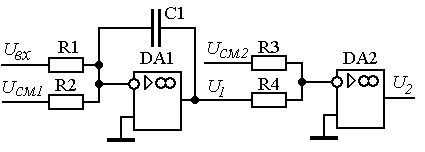

Применение операционных усилителей позволяет сформировать стабильные временные задержки длительностью несколько десятков секунд. Вариант схемы задержки на операционных усилителях приведен на рис. 7 2, а, е ее временные диаграммы на рис. 7. 2,б. На усилителе DA1 реализован интегратор, а на усилителе DA2 - компаратор.

а) б)

Рис. 7. 2. Формирование временных задержек на операционных усилителях

Выходное напряжение ненасыщенного интегратора в общем случае определяется уравнением

![]() ,

(7.4)

,

(7.4)

где

![]() ,

,![]()

Порог переключения

компаратора найдем из уравнения для

момента переключения

![]() .

.

![]() . (7.5)

. (7.5)

Рассмотрим процесс

формирования

![]() ,

при

,

при![]() ,

,![]()

![]() ,

отсюда

,

отсюда

![]() . (7.6)

. (7.6)

Аналогично при

формировании

![]() ,

при

,

при![]() ,

,![]()

![]() ,

отсюда

,

отсюда

![]() . (7.7)

. (7.7)

Пример:

При

![]() с,

с,![]() с,

с,![]() В,

В,![]() В,

В,![]() :

:![]() с,

с,![]() с.

с.

При

![]() с,

с,![]() с,

с,![]() В,

В,![]() В,

В,![]() :

:![]() с,

с,![]() с.

с.

При

![]() с,

с,![]() с,

с,![]() В,

В,![]() В,

В,![]() :

:![]() с,

с,![]()

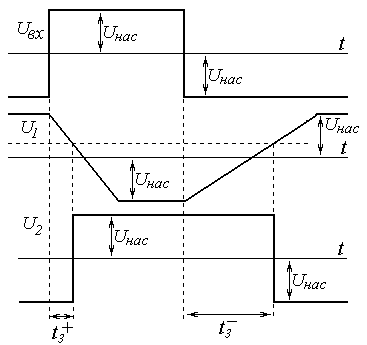

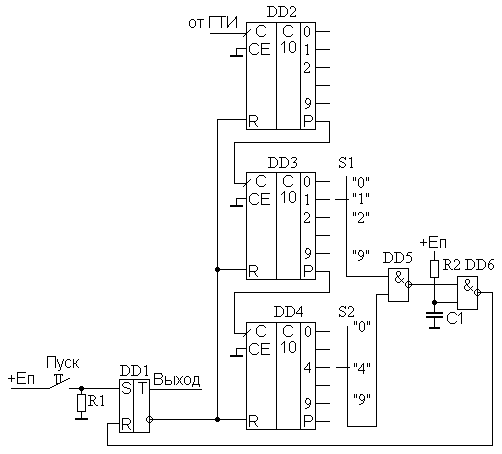

7.1.3 Синтез таймера

Задание: Разработать таймер, формирующий импульсы длительностью от 1 до 99 секунд. Длительность импульсов устанавливается двумя переключателями. Запуск таймера осуществляется кнопкой.

Синхронизация

запуска генератора импульсов дает

погрешность, поэтому будем использовать

предделитель, понижающий частоту

импульсов в 10 раз и ограничивающий

ошибку запуска на уровне

![]() с.

В качестве счетчиков будем использовать

двоично-десятичные счетчики К561ИЕ8,

имеющие на своем выходе дешифратор

двоично-десятичного кода в единичный

код. Функциональная схема таймера

приведена на рис. 7. 3.

с.

В качестве счетчиков будем использовать

двоично-десятичные счетчики К561ИЕ8,

имеющие на своем выходе дешифратор

двоично-десятичного кода в единичный

код. Функциональная схема таймера

приведена на рис. 7. 3.

Рис. 7. 3. Функциональная схема таймера

Входная логика Л1 формирует сигнал запуска счетчиков, выходная логика, которой относится дешифратор ДШ и логика Л2, формируют выходной сигнал. В частном случае входная и выходная логика совмещается.

В качестве входной логики возьмем RS-триггер, который будет запускать счетчики СЧ1, СЧ2, СЧ3. Триггер будем переключать в состояние сигналом «Пуск». В исходное состояние он будет переключаться дешифратором при достижении нужного времени, или при подаче питания.

Принципиальная схема таймера приведена на рис. 7. 4. Счетчик СЧ1 является предделителем, счетчик СЧ2 отсчитывает секунда, а СЧ3 десятки секунд. Связь счетчиков осуществляется через сигнал переноса р. Единичный сигнал на инверсном выходе триггера DD1 сбрасывает все счетчики в ноль. Это состояние триггера DD1 является исходным. В это состояние его переводит RC-цепочка R2, C1 при подаче напряжения питания, когда заряд емкости С1 воспринимается элементом DD6 как нулевой сигнал.

Запуск таймера осуществляется кнопкой «Пуск», которая формирует единичный сигнал на S входе триггера, устанавливая его в единичное состояние. Сигнал R на входах счетчиков принимает нулевое значение, разрешая счетчикам работать. Прямой выход триггера является выходом таймера.

Дешифратор выполнен на элементе DD5 и переключателях S1, S2. Переключатели подключают соответствующий выход дешифраторов счетчиков, DD3, DD4 к дешифратору DD5. Элемент DD6 инвертирует сигнал дешифратора DD5, устанавливая триггер DD1 в исходное (нулевое) состояние после окончания формирования временного интервала.

Временные диаграммы работы таймера при формировании импульса длительностью 14 секунд приведены на рис. 7. 3. Переключатель S1 находится в положении «1», а переключатель S2 в положении «4».

Рис. 7. 4 Принципиальная схема таймера