Основы автоматизации Ямный,Яновский

.pdf

плитудой 30–40 В. Электроны вытесняются в подложку. При отсутствии заряда электронов под затвором передаточная характеристика смещается в область высоких пороговых напряжений.

Структурная схема РПЗУ на МНОП-транзисторах не отличается от описанного ранее ПЗУ (рис. 7.7). Единственно вместо МОП-транзис- торов используются МНОП-транзисторы, затворы которых соединены с соответствующими выходами дешифратора адреса. В таком РПЗУ возбуждение соответствующей адресной линии при считывании информации приводит к появлению нулевого потенциала на разрядных линиях, к которым подключены находящиеся в единичном состоянии МНОП-тран- зисторы. Ненулевой потенциал сохраняется на разрядных линиях, к которым подключены находящиеся в нулевом состоянии МНОП-тран- зисторы.

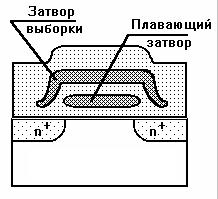

ЛИЗМОП-транзистор с двойным затвором представляет собой р-ка- нальный нормально закрытый МОП-транзистор. Его конструкция приведена на рис. 7.10. Плавающий затвор представляет собой область поликремния, окруженную со всех сторон диэлектриком, т. е. он электрически не связан с другими электродами и его потенциал «плавает».

В режиме программирования высо- |

|

|

|

кое напряжение подается на второй за- |

|

|

|

твор, находящийся над плавающим затво- |

|

|

|

ром, и в плавающем затворе накапливает- |

|

|

|

ся отрицательный заряд. Величину заряда |

|

|

|

выбирают такой, чтобы он обеспечил по- |

|

|

|

явление электропроводящего канала, со- |

p |

p |

|

единяющего сток и исток. |

|||

|

|

||

После снятия программирующего |

Подложка n-типа |

||

напряжения индуцированный заряд остается на плавающем затворе и, следова- Рис. 7.10. ЛИЗМОП-транзистор тельно, транзистор остается в проводящем

состоянии. Заряд на плавающем затворе может храниться десятки лет. Транзистор становится неэлектропроводящим, если убрать электри-

ческий заряд с «плавающего» затвора. Для этого область затвора облучают ультрафиолетовым излучением. Мощность его должна быть достаточной для ионизации и возникновения в цепи затвора фототока, в результате чего заряд исчезает. Время стирания микросхемы колеблется в пределах 10–30 минут. Для того чтобы ультрафиолетовое излучение могло беспрепятственно проходить к полупроводниковому кристаллу, в корпус микросхемы встраивается окошко из кварцевого стекла. Количество циклов записи–стирания микросхем колеблется в диапазоне от 10 до

91

100 раз, после чего микросхема выходит из строя. Это связано с разрушающим воздействием ультрафиолетового излучения.

В ЛИЗМОП-структурах с двойным затвором стирание информации может производиться также импульсами напряжения положительной полярности с амплитудой около 30 B.

7.4.4. Флэш-память

Флэш-память является энергонезависимой памятью. Однако в отличие от РПЗУ содержимое ИС флэш-памяти можно многократно перезаписывать, не вынимая ее из схемы. Запись происходит медленнее, чем считывание. Вследствие этого, а также из-за ее стоимости флэш-память не заменит схемы ОЗУ. Она широко используется в качестве памяти программ микроконтроллеров.

Запоминающий элемент флэш-памяти выполнен по технологии EPROM Thin Oxide. На подложке р-типа сформированы n-области истока и стока МОП-транзистора. Управляющий затвор его отделен от подложки тонким слоем оксида кремния. Между подложкой и управляющим затвором в слое оксида сформирована область поликремния, выполняющая функции плавающего затвора. При наличии отрицательного заряда транзистор имеет высокое сопротивление на участке исток/сток.

Толщина слоя между плавающим затвором и подложкой уменьшена в 3 раза по сравнению с EPROM (до 0,01 мкм), поэтому напряжение записи уменьшено и появилась возможность электрического стирания при пониженном напряжении. Эти свойства позволили применять флэш-па- мять как перепрограммируемую память, установленную прямо на системной плате.

92

Лекция 8 МИКРОПРОЦЕССОРЫ

Микропроцессор (МП) – это программно-управляемое цифровое устройство, предназначенное для обработки цифровой информации и управления процессом этой обработки, выполненное на одной или нескольких интегральных схемах. Используется в качестве центрального процессора в микро-ЭВМ и в микропроцессорных системах автоматизации эксперимента.

Основные характеристики МП:

–тактовая частота, определяющая время выполнения команды в микропроцессорах;

–разрядность шины данных (ШД), т. е. максимальное число одновременно обрабатываемых двоичных разрядов;

–разрядность шины адреса (ША), определяющая размер адресного пространства памяти;

–архитектура.

Архитектура микропроцессора включает его организацию и характеристики, рассматриваемые с позиций пользователя, способы представления и форматы данных, способы обращения ко всем программнодоступным элементам структуры (адресация к регистрам, ячейкам памяти, внешним устройствам), систему команд, характеристики вырабатываемых микропроцессором и поступающих в него извне управляющих сигналов и т. д.

8.1. Базовая структура микропроцессорной системы

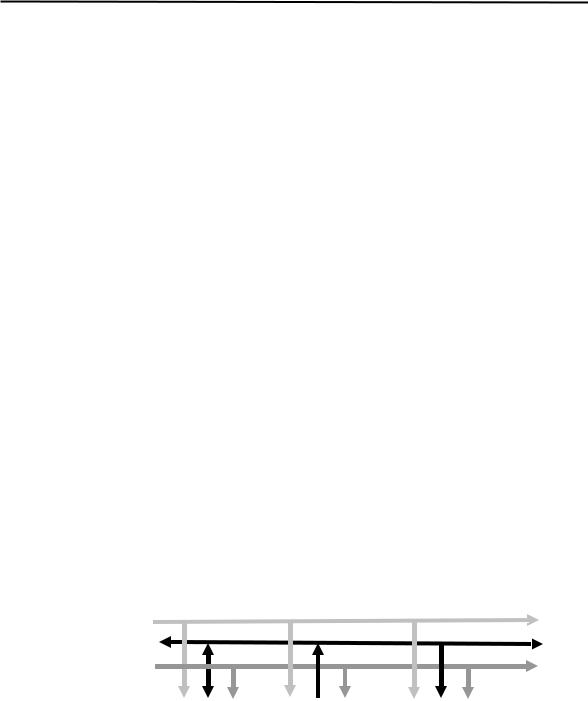

Базовая структура микропроцессорной системы представлена на рис. 8.1. Задача управления системой возлагается на МП, который связан с памятью, устройствами ввода и устройствами вывода системной магистралью.

Микропроцессор |

|

|

|

|

|

|

ША |

|

|

|

|

|

ШД |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ШУ |

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

Память |

|

Устройства |

|

Устройства |

|

|

|

|

ввода |

|

вывода |

|

|

|

|

|

|

|

|

||

Рис. 8.1. Базовая структура микропроцессорной системы

Системная магистраль состоит из однонаправленной шины адреса (ША), двунаправленной шины данных (ШД) и шины управления (ШУ).

93

ША обеспечивает передачу формируемых МП адресов ячеек памяти, устройств ввода и устройств вывода. Передача адресов в обратном направлении невозможна.

ШД используется для обмена данными (операндами) между МП, с одной стороны, и памятью, устройствами ввода и вывода, с другой. ШД является двунаправленной, т. е. по ней возможна передача данных как из МП в память или устройства вывода, так и из памяти или устройств ввода в МП.

ШУ предназначена для передачи управляющих сигналов, необходимых для организации обмена данными и управления работой всех элементов микропроцессорной системы.

МП непосредственно выполняет арифметические и логические операции над данными, осуществляет программное управление процессом обработки данных, организует взаимодействие всех элементов системы.

Фактическая последовательность операций определяется командами программы, записанной в памяти. МП поочередно считывает команды и декодирует их. В зависимости от результатов декодирования команды МП осуществляет выборку данных из памяти или портов ввода, обрабатывает их и пересылает обратно в память или порты вывода.

Врассматриваемой микропроцессорной системе используется так называемая фон неймановская организация памяти, при которой для хранения программ и данных используется одно пространство памяти. Программы и данные хранятся в этом пространстве, и нет никаких признаков, указывающих на тип информации в ячейке памяти. Память подразделяется на ПЗУ и ОЗУ.

Вмикропроцессорной системе имеется так называемо стековое ЗУ (стек). Стеком называется ЗУ с последовательным доступом, в котором слова считываются в порядке, обратном записи, т. е. по правилу LIFO (Last-in First-out – последним вошел – первым вышел). Чаще всего в качестве стека используется часть ОЗУ микропроцессорной системы.

Устройства ввода и вывода обеспечивают возможность обмена информацией между МП и внешней средой. Устройства ввода преобразуют вводимые данные из формы представления во внешнем устройстве в воспринимаемые МП электрические сигналы. К таким устройствам относятся клавиатура, датчики состояния управляемых объектов, аналогоцифровые преобразователи и т. п.

Устройства вывода преобразуют выходные данные МП в неэлектрические, цифровые или аналоговые электрические сигналы, удобные для восприятия человеком или используемые для непосредственного управления исполнительными механизмами в системах автоматизации. К

94

устройствам вывода относятся такие внешние устройства, как индикаторы, печатающие устройства, цифро-аналоговые преобразователи и т. д.

8.2. Структурная схема микропроцессора

Первый МП Intel 4004 был разработан фирмой Intel в 1970 году. Это был четырехразрядный МП с восьмиразрядными командами, с раздельной памятью программ и данных, по своим функциональным возможностям аналогичный центральному процессору большой ЭВМ. Он обладал ограниченными возможностями ввода/вывода и неразвитой системой команд.

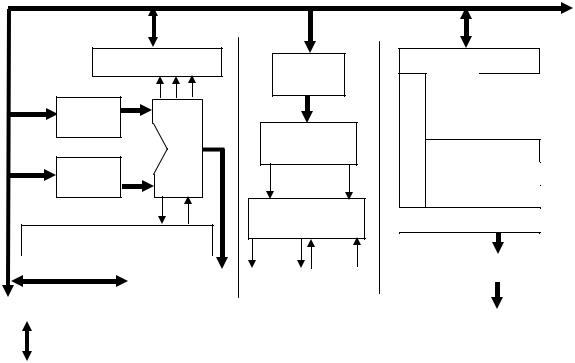

В 1974 году фирма Intel выпускает МП Intel 8080, положив начало целому семейству МП. Упрощенная структурная схема этого МП приведена на рис. 8.2.

Внутренняя шина данных

|

PSW |

Регистр |

|

Мультиплексор |

||

|

|

|

|

|

||

|

|

команд |

С |

B |

C |

|

|

|

|

||||

Буферный |

|

|

е |

D |

E |

|

Σ |

|

л |

||||

регистр |

|

|

|

|||

Дешифратор |

е |

H |

L |

|||

|

|

|||||

|

|

к |

|

|

||

|

|

команд |

Указатель стека |

|||

|

|

т |

||||

Буферный |

|

|

о |

Счетчик команд |

||

регистр |

|

|

р |

Схема +1/–1 |

||

|

|

Схема управления |

|

|||

|

|

|

Регистр адреса |

|||

|

|

и синхронизации |

|

|||

Схема десятичной коррекции |

|

|

|

|||

|

|

|

|

|||

|

|

|

|

|

|

… |

… |

|

|

|

|

|

|

|

|

|

Буфер ША |

||

|

|

|

|

|

|

|

ШУ |

|

|

|

|

|

Аккумулятор |

|

|

|

|||

|

|

|

ША |

||||||

|

|

|

|

|

|

Блок регистра |

|

||

Буфер ШД |

|

|

|

|

Блок регистров |

||||

|

АЛУ |

|

команд |

||||||

|

|

|

|

|

|

||||

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

ШД

Рис. 8.2. Структурная схема МП Intel 8080

МП содержит арифметико-логическое устройство (АЛУ), блок регистра команд, блок регистров, внутреннюю 8-разрядную ШД и буферы ШД и ША.

Арифметико-логическое устройство. АЛУ выполняет арифметиче-

скую и логическую обработку данных, представленных в двоичном или в двоично-десятичном коде. Оно состоит из аккумулятора, комбинационного сумматора Σ, двух буферных регистров, регистра состояния (признаков) и схемы десятичной коррекции.

95

Комбинационный двоичный сумматор предназначен для выполнения арифметических и логических операций над 8-разрядными числами.

Аккумулятор (А) – 8-разрядный программно доступный регистр, используемый для приема одного из операндов и для хранения результата при выполнении сумматором логических и арифметических операций.

Буферные регистры предназначены для приема и хранения операндов на время выполнения операций в АЛУ.

Регистр слова состояния (PSW) – 8-разрядный параллельный регистр, используемый для индикации результатов выполняемых в АЛУ операций. Он содержит флаги основного переноса (С), вспомогательного переноса (СY), нуля (Z), знака (S) и четности. Регистр слова состояния часто называют регистром признаков.

Схема десятичной коррекции обеспечивает коррекцию результата сложения двоичным сумматором десятичных чисел, представленных в двоично-десятичном коде 8-4-2-1.

Блок регистра команд. Блок регистра команд организует работу МП под управлением программы. Он содержит регистр команд, дешифратор команд и схему управления и синхронизации.

Регистр команд – 8-разрядный параллельный регистр, используемый для приема кода операции считываемой из памяти команды и для хранения его в течение времени выполнения этой команды.

Дешифратор команд декодирует код операции выполняемой команды.

Схема управления и синхронизации – микропрограммное устройство,

хранящее в своей памяти микропрограммы выполнения всех команд МП. Вырабатывает сигналы управления, необходимые для выполнения каждого машинного цикла и всей команды в целом.

Блок регистров. Блок регистров обеспечивает возможность обмена информацией между различными функциональными узлами МП в процессе выполнения программы. Он состоит из регистров общего назначения (РОН), указателя стека, счетчика команд (программного счетчика), схемы инкремента/декремента (схема +1/–1), мультиплексора, селектора и регистра адреса.

Шесть 8-разрядных РОН (B, C, D, E, H и L) в зависимости от типа выполняемой команды используются индивидуально для хранения 8-раз- рядных операндов или парами (B, C; D, E; H, L) для хранения 16-раз- рядных операндов. Эти регистры обеспечивают быстрый доступ к хранящимся в них операндам, поэтому их часто называют сверхоперативным запоминающим устройством.

96

Счетчик команд (СК) – 16-разрядный регистр, служащий для приема, хранения и выдачи текущего адреса команды. Так как при чтении каждого байта команды содержимое СК увеличивается на единицу, то после выполнения текущей команды СК автоматически указывает адрес следующей команды. В некоторых случаях содержимое СК может быть изменено самой программой (например, при выполнении команд переходов).

Схема инкремента/декремента служит для увеличения содержимого СК на единицу или увеличения/уменьшения на единицу содержимого регистров и регистровых пар.

Указатель стека – программно доступный 16-разрядный регистр, используемый для приема и хранения адреса плавающей вершины стековой памяти (стека).

Регистр адреса содержит значение исполнительного адреса ячейки памяти или устройств ввода/вывода.

Мультиплексор обеспечивает возможность двунаправленного обмена информацией между внутренней ШД МП и блоком регистров. При этом выбор регистров блока осуществляется селектором.

Внутренняя ШД предназначена для организации обмена информацией между различными функциональными узлами МП.

Буфер ША – 16-разрядный буферный регистр обеспечивает передачу исполнительного адреса на ША системной магистрали МП.

Буфер ШД – 8-разрядный буферный регистр обеспечивает двунаправленный обмен данными между ШД системной магистрали МП и его внутренней ШД.

Системная магистраль МП Intel 8080 состоит из:

–8-разрядной двунаправленной трехстабильной ШД;

–16-разрядной однонаправленной трехстабильной ША, обеспечивающей адресацию памяти объемом до 64 Кбайтов, адресацию 256 устройств ввода и 256 устройств вывода;

–ШУ, предназначенной для передачи управляющих сигналов, необходимых для правильного функционирования МП в составе системы.

ШУ состоит из 6 линий, используемых для передачи на входы схемы управления и синхронизации внешних (входных) сигналов, и 6 линий, предназначенных для передачи управляющих сигналов, формируемых схемой управления и синхронизации. Рассмотрим наиболее важные сигналы, передаваемые по линиям ШУ.

SR – входной сигнал установки МП в исходное состояние. Сигнал SR = 1 устанавливает счетчик команд и регистр команд, триггеры разрешения прерывания и захвата шин в нулевое состояние. Во время дейст-

97

вия этого сигнала (SR = 1) ША и ШД находятся в высокоомном состоянии. При этом все выходные управляющие сигналы переходят в неактивное состояние. При переходе сигнала SR от уровня напряжения логической единицы к уровню напряжения логического нуля МП начинает работу с машинного цикла загрузки кода операции в регистр команд.

ROINR – входной сигнал запроса устройства ввода/вывода на обмен данными по прерыванию. Запрос воспринимается, если прерывания разрешены.

TR – входной сигнал запроса устройства ввода/вывода на прямой доступ к памяти. Сигнал TR = 1 переводит МП в состояние «захват», в котором линии ШД и ША находятся в высокоомном состоянии.

RD – выходной сигнал чтения памяти или устройств ввода.

WR – выходной сигнал записи данных в память или в устройства вывода. Логический нуль на этом выходе указывает на то, что на ШД находятся данные, поступающие из МП.

8.3. Команды микропроцессора

МП организует обработку данных под управлением программы, представляющей собой определенным образом организованную совокупность машинных команд.

Машинной командой называется двоичное слово, воспринимаемое МП и определяющее все его действия при выполнении команды. Каждая машинная команда состоит из кода операции и поля адреса. Код операции определяет вид выполняемой операции. Поле адреса определяет местоположение обрабатываемых данных (операндов) и результата операции.

С целью сокращения длины команды в МП для размещения одного из операндов и результата некоторых команд используется аккумулятор.

В зависимости от числа ячеек памяти, необходимых для размещения одной команды, различают команды в одно слово (байт), два слова (байта) и в три слова (байта). Формат команд МП Intel 8080 приведен на рис. 8.3. Байты многобайтной команды обязательно размещаются в соседних ячейках памяти, и адрес первого байта является адресом команды в целом.

По своей структуре команды подразделяются на одноадресные, двухадресные и безадресные.

98

Байт 1 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

код операции |

|

|

|

|

|

|

|

|

|

|

|

|

возможные адресные поля |

|

|

|

а |

|||||

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

код операции |

Байт 1 |

D7 |

D6 |

D5 |

D4 |

D3 |

|

D2 |

D1 |

D0 |

||

Байт 2 |

|

|

|

|

|

|

|

|

|

данные или адрес |

|

|

|

|

|

|

|

|

|

|

|||

D7 |

D6 |

D5 |

D4 |

D3 |

|

D2 |

D1 |

D0 |

|||

|

|

|

|

|

|

|

|

|

|

|

б |

|

|

|

|

|

|

|

|

|

|

|

|

Байт 1 |

|

|

|

|

|

|

|

|

|

|

код операции |

|

D7 |

D6 |

D5 |

D4 |

D3 |

|

D2 |

D1 |

D0 |

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Байт 2 |

|

D7 |

D6 |

D5 |

D4 |

D3 |

|

D2 |

D1 |

D0 |

данные |

|

|

|

|

|

|

|

|

|

|

|

или |

|

|

|

|

|

|

|

|

|

|

|

|

Байт 3 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

адрес |

||

|

|

|

|

|

|

|

|

|

|

|

|

в

Рис. 8.3. Форматы команд МП Intel 8080:

а – однобайтная; б – двухбайтная; в – трехбайтная

Базовая система команд современных микропроцессоров содержит от 20 до 150 команд форматом от одного до трех слов. Многие из них порождают несколько различных кодов операций. Запоминание двоичных кодов всех этих команд не представляется возможным. Представление кодов команд в восьмеричной или в шестнадцатеричной системе счисления несколько упрощает запись программ, но не решает проблему, так как одинаковое представление данных, адресов и кодов операций затрудняет понимание программы, значительно усложняет ее коррекцию и использование на практике.

Данная проблема решается применением мнемонических обозначений команд, в которых для обозначения кода операции используется сокращенная запись названия команды, отражающая содержательный смысл, а адрес и данные выражены символическим именем, двоичным, десятичным или шестнадцатеричным числом. Например, мнемоническое обозначение команды пересылки содержимого регистра В в аккумулятор имеет следующий вид: MOV А, В.

Такое сочетание сокращенного буквенного обозначения кода операции с числовой формой записи адреса и данных является одной из наиболее удобных форм записи команды и широко применяется при использовании одного из наиболее распространенных языков программирования микропроцессорных систем – языка ассемблера.

99

По функциональному назначению команды микропроцессора можно подразделить на команды передачи данных, команды преобразования данных и команды управления программой.

Команды передачи данных. Команды этой группы подразделяются на команды внутрипроцессорного обмена, команды обращения к памяти, команды ввода/вывода и команды, оперирующие со стеком. Ни одна из команд этой группы не изменяет содержимое регистра слова состояния.

Команды внутрипроцессорного обмена обеспечивают передачу и обмен данными между регистрами МП, а также обеспечивают загрузку этих регистров константами.

Загрузка регистров общего назначения или регистровых пар МП осуществляется соответственно двухбайтными и трехбайтными командами с непосредственной адресацией.

Команды обращения к памяти обеспечивают запоминание содержимого РОН или регистровых пар в памяти, загрузку РОН или регистровых пар данными из памяти, а также загрузку ячеек памяти константой.

Вкомандах обращения к памяти широко используются косвенная, регистровая и прямая адресации.

Группа команд, оперирующая со стеком, обеспечивает загрузку указателя стека и обмен данными между стеком и РОН МП.

Команды преобразования данных. Эти команды выполняют опера-

ции обработки данных. Они включают команды арифметических и логических операций, операций сравнения и сдвига.

Вычислительные возможности МП определяются простыми командами сложения содержимого одного из регистров общего назначения или ячейки памяти с содержимым аккумулятора и командами вычитания содержимого одного из регистров общего назначения или ячейки памяти из содержимого аккумулятора.

Втех случаях, когда применение однобайтных чисел не обеспечивает требуемую точность вычислений, приходится вводить многобайтные числа с последовательной обработкой отдельных байтов. Для обработки таких чисел удобно использовать команды сложения содержимого аккумулятора с переносом, полученным в предыдущей операции при сложении младших байтов, и с содержимым одного из регистров общего назначения или ячейки памяти, а также команды вычитания из содержимого аккумулятора заема и содержимого регистра или ячейки памяти.

Во всех рассмотренных командах арифметических операций местоположением одного из операндов является аккумулятор, а результат операции помещается опять в аккумулятор. При этом операнд, который ра-

100