- •Компьютерная

- •Запоминающие устройства

- •Классификация ОЗУ

- •Классификация ОЗУ

- •Классификация ОЗУ

- •Классификация ОЗУ

- •Запоминающий элемент на биполярных транзисторах

- •Запоминающий элемент на биполярных транзисторах

- •Запоминающий элемент на биполярных транзисторах

- •Запоминающий элемент на МДП-транзисторах

- •Запоминающий элемент на КМДП-транзисторах

- •Запоминающий элемент на КМДП-транзисторах

- •Структурная схема ОЗУ с одномерной адресацией

- •Структурная схема ОЗУ с одномерной адресацией

- •Структурная схема ОЗУ с двумерной адресацией

- •Структурная схема ОЗУ с двумерной адресацией

- •Обобщенные временные диаграммы (режим записи)

- •Обобщенные временные диаграммы (режим чтения)

- •Особенности ОЗУ

- •Динамические ОЗУ

- •Запоминающий элемент динамических ЗУ

- •Обобщенная структура динамического ЗУ

- •Динамические ЗУ

- •Обобщенные временные диаграммы (режим записи)

- •Обобщенные временные диаграммы (режим чтения)

- •Обобщенные временные диаграммы (режим регенерации)

- •Обобщенные временные диаграммы

- •Особенности динамических ОЗУ

Компьютерная

схемотехника

Лекция 15. Оперативные запоминающие устройства

Запоминающие устройства

Запоминающие устройства (ЗУ) предназначены для хранения информации и обмена ею с другими частями ЭВМ или компьютерных систем.

По функциональному назначению ЗУ подразделяют на внешние, буферные и внутренние.

Внешние ЗУ служат для хранения больших объемов информации и программного обеспечения (магнитные барабаны, магнитные диски, лазерные диски и т.д.).

Буферные ЗУ предназначены для промежуточного хранения данных при обмене между внешней и внутренней памятью.

Внутренние ЗУ, являются неотъемлемой частью ЭВМ и непосредственно управляют ею.

Классификация ОЗУ

Классификация ОЗУ

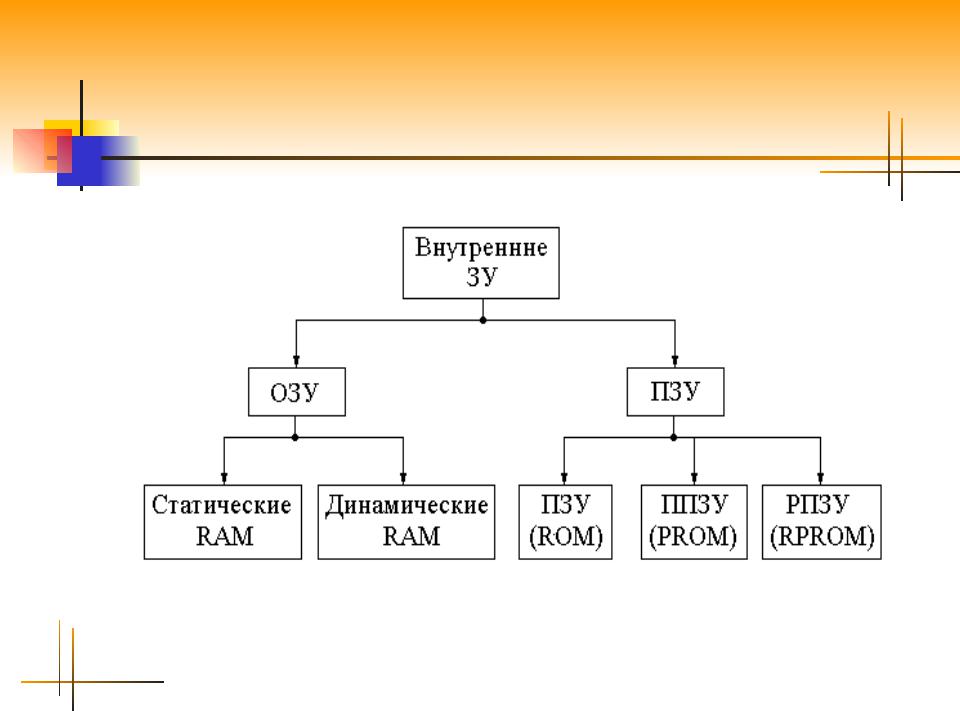

Внутренние ЗУ по выполняемым функциям делят на оперативные (ОЗУ) и постоянные (ПЗУ).

ОЗУ выполняет запись, считывание и хранение произвольной двоичной информации, обеспечивающей хранение программ для текущей обработки информации и массивов обрабатываемых данных.

Встатических ОЗУ запоминающий элемент представляет собой бистабильный элемент (обычно триггер), поэтому обеспечивается считывание информации без ее разрушения.

Вдинамических ОЗУ для хранения информации используются инерционные свойства реактивных элементов (обычно заряд и разряд конденсатора), что требует периодического восстановления (регенерации) состояния запоминающих элементов при хранении и считывании.

Классификация ОЗУ

ПЗУ осуществляет хранение и выдачу постоянной записываемой информации, содержание которой не изменяется во время работы системы.

ПЗУ делят по способу занесения информации:

ПЗУ, программируемое заводом-изготовителем (ROM);

ПЗУ, программируемые пользователем однократно (PROM.OTP);

репрограммируемые ПЗУ (RPROM).

Классификация ОЗУ

По способу обращения ЗУ подразделяют на адресные и ассоциативные.

Вадресных ЗУ обращение к запоминающему элементу производится по его физическим координатам, задаваемым внешним двоичным кодом адреса. Адресные ЗУ бывают с произвольной выборкой, которые допускают любой порядок следования адресов и с последовательным обращением, в котором выборка запоминающих элементов возможна только в порядке возрастания или убывания адреса.

Вассоциативных ЗУ поиск информации производится по признакам, заключающимся в самой хранимой информации, независимо от физических координат ЗУ.

Запоминающий элемент на биполярных транзисторах

Запоминающий элемент представляет собой бистабильный элемент, в котором информация при считывании не разрушается.

Запоминающий элемент на биполярных транзисторах

Разрядная шина предназначена для считывания состояния триггера и для записи в него новой информации.

Если на одну или обе адресные шины подано низкое напряжение (уровень ‘0’), то триггер будет находиться в устойчивом состоянии и ток открытого транзистора будет замыкаться на землю через эмиттеры, подключенные к адресным шинам.

Если напряжение на адресных шинах повысить до уровня лог. ‘1’, то эмиттеры, подключенные к разрядной шине, управляют током транзисторов. Если транзистор VT1 открыт, то ток пойдет через левый резистор (R1). В это время транзистор VT2 закрыт и, таким образом, через резистор R4 ток не протекает. Это означает, что напряжение на резисторе R1 будет больше, чем напряжение на резисторе R2.

Из изложенного следует, что состояние триггера можно определить, измеряя напряжение на резисторах R1 и R2. Это обычно выполняется  усилителем считывания.

усилителем считывания.

Запоминающий элемент на биполярных транзисторах

Используя линии разряда, можно также записывать информацию

вячейку. Предположим, что на адресных шинах уровень лог. ‘1’, и напряжение на R1 установлено выше, чем на R4. Тогда транзистор VT2 откроется и закроет транзистор VT1.

Таким образом, одни и те же разрядные шины используют для считывания состояния триггера и для установки заданного значения

ввыбранную ячейку.

Запоминающий элемент на МДП-транзисторах

ЗЭ на основе МДП-структур представляет собой простейший RS- триггер. На их базе создают ЗУ большой и сверхбольшой емкости.

Основной их недостаток - потребление тока в режиме хранения, так как один из транзисторов триггера всегда находится в открытом состоянии. Для уменьшения потребляемой мощности необходимо увеличить сопротивление нагрузки, но это приводит к снижению быстродействия. Поэтому используют схемы на КМДП - транзисторах, где ток потребляется только в момент переключения.