Микропроцессорная техника / Конспект лекций

.pdf

11: /8

MCx (биты 5…4) – управление режимом таймера. Установка MCx = 00h при неиспользуемом таймере уменьшает общее потребление микроконтроллера.

00: Останов: таймер остановлен.

01: Прямой счёт: таймер считает от 0000h до TACCR0.

10:Непрерывный счёт: таймер считает от 0000h до 0FFFFh.

11:Реверсивный счёт: таймер считает от 0000h до TACCR0, а потом в обратном направлении до 0000h.

Unused (бит 3) – не используется.

TACLR (бит 2) – очистка таймера. Установка этого бита обнуляет регистр

TAR, делитель и сбрасывает признак направления счёта. Бит TACLR

автоматически сбрасывается; всегда читается как 0.

TAIE(бит 1) – разрешение прерывания таймера. Этот бит разрешает генерацию запроса прерывания TAIFG.

0:Прерывание запрещено

1:Прерывание разрешено

TAIFG(бит 0) – флаг прерывания таймера.

0:Прерывания не было

1:Прерывание было

TAR, регистр счётчика Таймера А

TARx (биты 15…0) – регистр счётчика Таймера А. В этом регистре содержится текущее значение Таймера А.

TACCRx, регистр захвата/сравнения x Таймера А

TAССRx (биты 15…0) – регистр захвата/сравнения Таймера А. Режим сравнения: регистр TACCRx содержит число, которое сравнивается с содержимым регистра счётчика TAR. Режим захвата: содержимое регистра TAR копируется в

61

регистр TACCRx в момент выполнения операции захвата.

TACCTLx, регистр управления блока захвата/сравнения

CMx (биты 15…14) – режим захвата. 00: Нет захвата

01: Захват по нарастающему фронту

10:Захват по спадающему фронту

11:Захват по обоим фронтам

CCISx (биты 13…12) – выбор входа захвата/сравнения. Эти биты определяют входной сигнал блока захвата/сравнения. Соответствие сигналов каждому из входов приводится в документации на конкретные модели.

00: CCIxA

01: CCIxB

10:GND

11:VCC

SCS (бит 11) – синхронизация захвата. Этот бит используется для синхронизации сигнала захвата с тактовым сигналом таймера.

0:Асинхронный захват

1:Синхронный захват

SCCI (бит 10) – синхронизованный вход захвата/сравнения. Входной сигнал блока захвата/сравнения фиксируется по сигналу EQUx и может быть считан при помощи этого бита.

Unused (бит 9) – не используется. Только для чтения. Всегда читается как 0.

CAP (бит 8) Режим работы блока захвата/сравнения.

0:Режим захвата

1:Режим сравнения

OUTMODx (биты 7…5) – режим работы модуля вывода. Для регистра

TACCR0 использование режимов 2, 3, 6 и 7 не имеет смысла, поскольку в этом случае EQUx = EQU0.

000: Состояние бита OUT 001: Установка

010: Переключение/сброс

011: Установка/сброс

62

100:Переключение

101:Сброс

110:Переключение/установка

111:Сброс/установка

CCIE(бит 4) – разрешение прерывания захвата/сравнения. Этот бит разрешает генерацию запроса прерывания при установке соответствующего фла га CCIFG.

0:прерывание запрещено

1:прерывание разрешено

CCI (бит 3) – вход захвата/сравнения. Посредством этого бита можно определить значение входного сигнала блока захвата/сравнения.

OUT (бит 2) Состояние выхода. При работе модуля вывода в режиме 0 этот бит напрямую управляет состоянием выхода.

0:На выходе НИЗКИЙ уровень

1:На выходе ВЫСОКИЙ уровень

COV (бит 1) – переполнение захвата. Этот бит индицирует переполнение при операциях захвата. Бит COV должен сбрасываться программно.

0:Не было переполнения при захвате

1:Было переполнение при захвате

CCIFG (бит 0) – флаг прерывания захвата/сравнения

0:Прерывания не было

1:Прерывание было

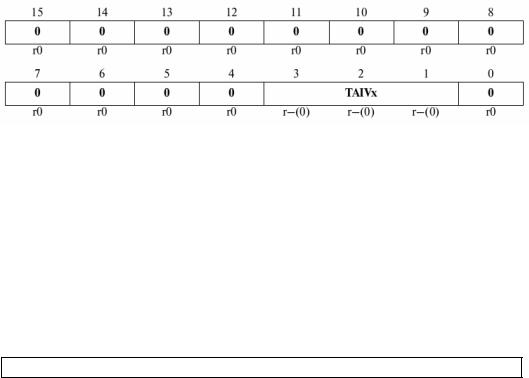

TAIV, регистр вектора прерывания

TAIVx (биты 15…0) – значение вектора прерывания таймера

Содержи- |

Источник прерывания |

Флаг |

Приоритет |

мое TAIV |

|

прерывания |

прерывания |

00h |

Не было прерываний |

— |

|

02h |

Захват/сравнение 1 |

TACCR1 CCIFG |

Высший |

04h |

Захват/сравнение 2* |

TACCR2 CCIFG |

|

06h |

Зарезервировано |

— |

|

08h |

Зарезервировано |

— |

|

0Ah |

Переполнение таймера |

TAIFG |

|

0Ch |

Зарезервировано |

— |

|

0Eh |

Зарезервировано |

— |

Низший |

* Не реализовано в моделях MSP430x20xx.

63

СПИСОК РЕКОМЕНДОВАННОЙ ЛИТЕРАТУРЫ

1. Семейство микроконтроллеров MSP340. Рекомендации по применению:

Пер. с англ. — М: Серия «Библиотека Компэла». ЗАО «Компэл», 2005. — 544 с. 2. Семейство микроконтроллеров MSP430x2xx. Архитектура,

программирование, разработка приложений / пер. с англ. Евстифеева А. В. — М. :

Додэка XXI, 2010. — 544 с.: ил.

3. Семейство микроконтроллеров MSP340х4хх. Руководство пользователя:

Пер. с англ. — М: Серия «Библиотека Компэла». ЗАО «Компэл», 2005. — 416 с. 4. Б.Ю. Семенов. Микроконтроллеры MSP430: первое знакомство. — М.:

СОЛОН-ПРЕСС, 2006 – 128 с.: ил.

64