Electro_lection_full

.pdf

Регистры.

– это устройства для хранения и преобразования многоразрядных двоичных чисел. Регистры строятся на триггерах, работающих согласованно и выполняющих общую функцию.

По принципу хранения информации делятся на:

1. Статические регистры.

Подобно триггеру хранят в себе информацию неопределенно долго.

2. Динамические регистры.

Должны постоянно тактироваться с некоторой минимальной частотой.

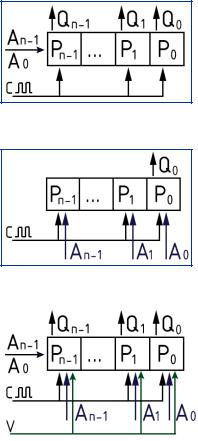

Классификация регистров по способу подачи/выдачи информации.

1. Регистр с параллельной подачей и параллельной выдачей информации.

Многоразрядное слово подается одновременно и на младший и на старший разряды и снимается так же одновременно со всех разрядов.

2. Регистр с последовательной подачей и последовательной выдачей информации.

Число поступает в старший разряд, а снимается последовательно с выхода младшего разряда

3. Регистр с последовательной подачей и параллельной выдачей информации.

Подается в старший разряд а снимается одновременно со всех разрядов.

4. Регистр с параллельной подачей и последовательной выдачей.

Подается одновременно на все разряды, а снимается с младшего.

5. Универсальный регистр.

Содержит дополнительный разрешающий вход V , позволяющий менять по мере надобности способы подачи и выдачи информации.

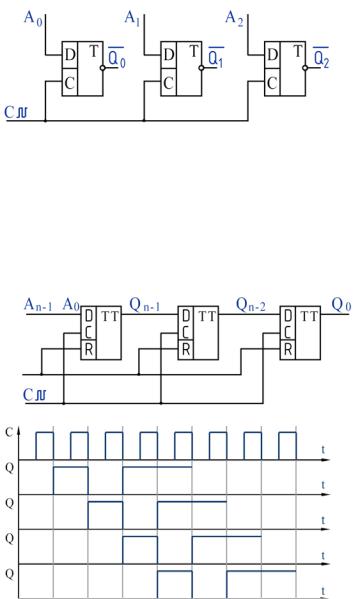

Схема регистра памяти.

Регистр памяти представляет из себя набор синхронных триггеров на инф. входы которых одновременно подаются сигналы (А0-А2). При этом инф. также одновременно снимается со всех инверсных выходов триггеров. Таким образом осуществляется параллельная подача и параллельная выдача информации.

Регистр сдвига.

Регистр сдвига также представляет собой последовательность синхронных RS-триггеров. Как и в предыдущем случае, двоичное число подается на инф. входы, при включении синхроимпульсов. Допустим, что в четырехразрядный регистр последовательно вводится кодовое слово 1101, после обнуления регистра с первым тактовым импульсом в триггер записывается ед. младшего разряда кодового слова. Со след. тактовым импульсом происходит сдвиг ед. во второй триггер и её появление на входе. Одновременно в первый триггер поступает 0.

Таким же образом будут происходить сдвиги последующих разрядов кодового слова.

После 4-х тактовых импульсов, код на выходах триггеров будет соответствовать входному коду.

Затем информация продолжает сдвигаться вправо и младший разряд исчезает. После прохождения второй группы из 4-х тактовых импульсов вся информация будет считана и регистр полностью очистится.

Реверсивный регистр.

Регистр включает в себя Д-триггер с динамическим управлением, а так же лог. схему на вход которой подаются сигналы V и Q.

Qi-1 – сигнал с выхода младшего разряда.

Qi+1 – сигнал с выхода старшего разряда.

V = 0 – сдвиг влево

V = 1 – сдвиг вправо.

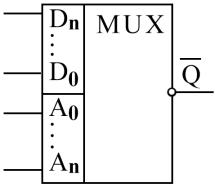

Мультиплексор (mux).

Служит для временного разделения информации и включает в себя 2 вида входов:

А – адресные входы.

D – информ. входы.

Числовые комбинации одновременно подаются и на А и на D входы. В зависимости от комбинации, подаваемой на А – входы, включается один из D-входов, и сигнал, подаваемый на этот вход снимается с выхода MUX.

Например, на входы А подается число 1101, тогда подключается соответствующий вход D, например D3, который в инверсном входе снимается с выхода MUX.

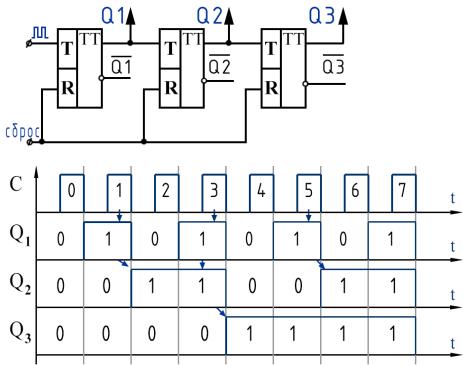

Счетчики.

Счетчик с постоянным модулем с чета.

Цифровым счетчиком импульсов называют устройство, реализующее счёт числа входных импульсов и фиксирующее это число в каком-либо коде на выходе.

Суммирующий счетчик.

С

Q3 Q2 Q1

0 0 0 0

1 0 0 1

2 |

0 |

1 |

0 |

3 0 1 1

4 1  0

0  0

0

5 1 0 1

61 1  0

0

71 1 1

Суммирующий счетчик включает в себя последовательность триггеров со счетным входом Т. В данном счетчике с приходом каждого тактового импульса его содержимое увеличивается на ед. При этом перенос информации из младшего разряда в след. более высокий происходит при изменении состояния с 1 на 0.

Вход R устанавливает счетчик в нулевое состояние. Если в исходном положении все триггеры были в сост. 0, то по окончании первого тактового импульса первый триггер перейдет в состояние 1. По окончании второго импульса 1 триггер переходит в состояние 0, а второй – в 1.

Таким образом, происходит перемещение одного триггера к другому. Счет заканчивается в тот момент, когда на всех триггерах устанавливается 1.

ЦАП (Цифроаналоговый преобразователь).

На вход ЦАП подается двоичное число, которое преобразуется в аналоговый сигнал в виде тока или напряжения.

ЦАП с суммированием весовых токов.

ЦАП включает в себя резистивную матрицу. На вход подается, а на выходе снимается соответствующее значение тока или напряжение. На вход также подается двоичное число.

В зависимости от комбинации нулей и единиц замыкаются те или иные ключи, таким образом, меняется выходное сопротивление схемы, а следовательно – уровень сигнала либо повышается, либо понижается.

Если подается 111, то на вых. нужно получить выс. уровень сигнала, а для этого должно замкнуться малое кол-во ключей.

Так как ключи постоянно замыкаются/размыкаются, то возникают помехи, что и является основным недостатком схемы.

АЦП.

На вход подается ток или напряжение, на выходе снимаем двоичное число, соответствующее входному напряжению или току.

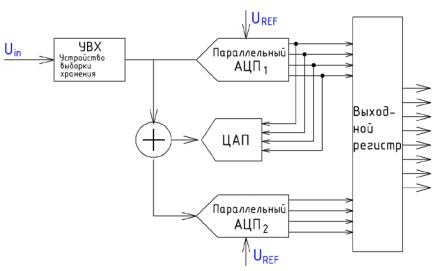

Многоступенчатый АЦП.

Входной сигнал в виде напряжения подается на устройство выборки хранения (УВХ), затем поступает на АЦП1, где происходит грубое преобразование напряжения в 4 старших разряда. Часть сигнала подается на ЦАП, на выходе которого формируется аналоговый сигнал в виде напряжения, поступающий на элемент сравнения. Разность входного сигнала и сигнала с АЦП поступает на АЦП2, на выходе которого формируется 4 младших разряда, поступающих в выходной регистр.

Таким образом, выходной регистр принимает сначала старший, а затем младший разряд.

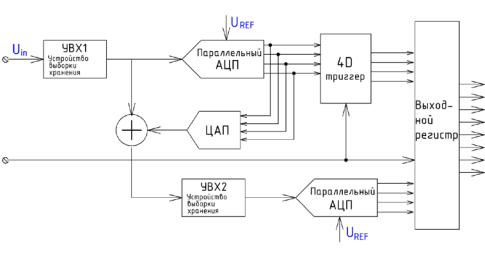

Конвейерный АЦП.

Преобразование аналогично предыдущей схеме, но в данную схему включены 4D – триггеры, осуществляющие цифровую задержку информации, а УВХ2 – аналоговую.

Таким образом и старшие и младшие разряды поступают одновременно в выходной регистр.