3472

.pdf3472 |

МИНИСТЕРСТВО ТРАНСПОРТА РОССИЙСКОЙ ФЕДЕРАЦИИ |

ФЕДЕРАЛЬНОЕ АГЕНТСТВО ЖЕЛЕЗНОДОРОЖНОГО ТРАНСПОРТА |

ФЕДЕРАЛЬНОЕ ГОСУДАРСТВЕННОЕ БЮДЖЕТНОЕ ОБРАЗОВАТЕЛЬНОЕ УЧРЕЖДЕНИЕ ВЫСШЕГО ПРОФЕССИОНАЛЬНОГО ОБРАЗОВАНИЯ

«САМАРСКИЙ ГОСУДАРСТВЕННЫЙ УНИВЕРСИТЕТ ПУТЕЙ СООБЩЕНИЯ»

Кафедра «Автоматика, телемеханика и связь на железнодорожном транспорте»

ИССЛЕДОВАНИЕ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АВТОМАТИКИ

МЕТОДИЧЕСКИЕ УКАЗАНИЯ

квыполнению лабораторной работы № 8 по дисциплине «Теоретические основы автоматики и телемеханики» для студентов специальности

190901 «Системы обеспечения движения поездов» очной и заочной форм обучения

Составитель: Л. А. Плешакова

Самара

2014

1

УДК 656.25

Исследование логических элементов дискретной автоматики : методические указания к выполнению лабораторной работы № 8 по дисциплине «Теоретические основы автоматики и телемеханики» для студентов специальности «Системы обеспечения движения поездов» очной и заочной форм обучения / составитель : Л. А. Плешакова. – Самара : СамГУПС, 2014. – 18 с.

В методических указаниях приведены схемы некоторых наиболее распространенных полупроводниковых логических элементов. Даны подробные указания по проведению экспериментов, выполняемых при исследовании этих элементов.

Утверждены на заседании кафедры 22 апреля 2014 г., протокол № 8. Печатаются по решению редакционно-издательского совета университета.

Составитель: Лариса Александровна Плешакова

Рецензенты: д. т. н., профессор, СамГУПС А. Е. Дубинин; к. т. н., профессор, СамГУПС В. Б. Гуменников

Под редакцией составителя

Подписано в печать 30.07.2014. Формат 60х90 1/16. Усл. печ. л. 1,13. Тираж 100 экз. Заказ 173.

© Самарский государственный университет путей сообщения, 2014

2

В В Е Д Е Н И Е

Лабораторная работа № 8 посвящена изучению и исследованию некоторых типов полупроводниковых логических элементов (ЛЭ), используемых в дискретных устройствах (ДУ) железнодорожной автоматики, телемеханики и связи.

При подготовке к лабораторной работе необходимо, прежде всего, ознакомиться с программой выполнения работы. Теоретические сведения по изучаемым ЛЭ приведены в настоящих методических указаниях в ограниченном объеме. Поэтому при подготовке к работе необходимые сведения следует почерпнуть из литературы [1 – 8] и лекционного материала.

Экспериментальная часть работы рассчитана на 2 часа. К выполнению этой части студент допускается только после проверки усвоения необходимой теории.

Отчет по работе оформляется каждым студентом индивидуально в процессе выполнения работы.

Цель работы: изучение принципа действия и устройства некоторых полупроводниковых логических элементов; их экспериментальное исследование.

КРАТКИЕ СВЕДЕНИЯ ИЗ ТЕОРИИ

Устройства железнодорожной автоматики, телемеханики и связи в основном относятся к классу дискретных устройств. В дискретных устройствах входные, выходные и промежуточные сигналы являются дискретными и обычно принимают только два значения. Эти значения целесообразно обозначить через 1 и 0 (при этом традиционно за «1» принимают: наличие сигнала, высокий уровень сигнала, отпирающее напряжение и т. д., а за «0» соответственно – отсутствие сигнала, низкий уровень сигнала, запирающее напряжение и т. д.). Все переменные и сигналы в алгебре логики обозначают буквами (по аналогии с переменными в обычной алгебре).

Всякую переменную, которая независимо от конкретной сущности может принимать только два значения (0 и 1), называют логической или булевой переменной, а всякую функцию f(x1, x2, x3, , xn) от n переменных, если она, как и ее аргументы, может принимать только два значения (0 и 1), называют функцией алгебры логики или булевой

функцией (БФ).

Логические элементы (ЛЭ) могут быть выполнены в виде самых разнообразных электрических схем. При этом аргументы изображают сигналами, поступающими на вход схемы, а функции – выходными сигналами. При этом все логические элементы должны обладать свойствами направленности и независимости. Первое свойство означает, что передача сигналов возможна только от входа к выходу ЛЭ (входные сигналы не

3

зависят от выходных), второе – что сигнал, поступающий на один из входов, не влияет на значения сигналов на других входах.

На рис. 1 показано условное обозначение ЛЭ, на вход которого подаются сигналы a, b, c, изображающие аргументы, а с выхода получают сигналы x, y, изображающие функции. Это значит, что схема реализует несколько логических связей. Здесь определенной комбинации сигналов на входах ЛЭ отвечает определенная комбинация сигналов на его выходах.

a |

|

x |

|

b |

ЛЭ |

||

y |

|||

c |

|

||

|

|

Рис. 1. Общее условное обозначение ЛЭ

Логические элементы делятся на контактные и бесконтактные. Контактные ЛЭ обычно реализуют на электромагнитных реле, бесконтактные в большинстве случаев строят на базе полупроводниковых приборов.

Из-за большого многообразия полупроводниковых ЛЭ, широко используемых в технике в настоящее время, принципиально невозможно в рамках одной лабораторной работы изучить и экспериментально исследовать даже наиболее распространенные из них. Поэтому экспериментальное исследование ограничивается некоторыми наиболее простыми ЛЭ, на которых можно изучить основные свойства, характерные для ЛЭ различных типов. Это элементы ИЛИ, И, НЕ, ИЛИ-НЕ, И-НЕ и И-ИЛИ-НЕ.

Элемент ИЛИ реализует дизъюнкцию (логическое сложение), т. е. такую БФ f (x1, x2 ,...,xn ) x1 x2 ... xn , которая равна 1 на тех наборах переменных, в которых хотя бы одна переменная равна 1, и равна 0, когда все переменные равны 0.

Элемент И реализует конъюнкцию (логическое умножение), т. е. такую БФ f (x1, x2 ,...,xn ) x1x2...xn , которая равна 1 только на том наборе переменных, в котором все переменные равны 1, и равна 0 на всех остальных наборах, т. е. когда равна 0 хотя бы одна переменная.

Элемент НЕ реализует логическое отрицание (инверсию) одной переменной х, т. е. такую БФ f (x) x , значение которой противоположно значению переменной х.

Логический элемент ИЛИ-НЕ реализует функцию Вебба (стрелку Пирса) f (x1, x2 ,...,xn ) x1 x2 ... xn , представляющую собой дизъюнкцию с инверсией (от-

рицание дизъюнкции): x1 x2 ... xn x1 x2 ... xn . Эта БФ принимает значение 0 на тех наборах, в которых хотя бы одна переменная равна 1, т. е. на всех наборах, кроме набора 00…0.

4

Логический элемент И-НЕ реализует функцию Шеффера (штрих Шеффера) f (x1, x2 ,...,xn ) x1 / x2 / .../ xn , являющуюся конъюнкцией с отрицанием (отрицанием

конъюнкции): x1 / x2 / .../ xn x1x2...xn . Эта БФ равна 1 на наборах, в которых хотя бы одна переменная равна 0, т. е. на всех наборах, кроме набора 11…1.

Элемент И-ИЛИ-НЕ можно рассматривать как комбинацию нескольких элементов И и элемента ИЛИ-НЕ, входы которого подключены к выходам элементов И. То есть этот ЛЭ реализует отрицание дизъюнкции нескольких конъюнкций.

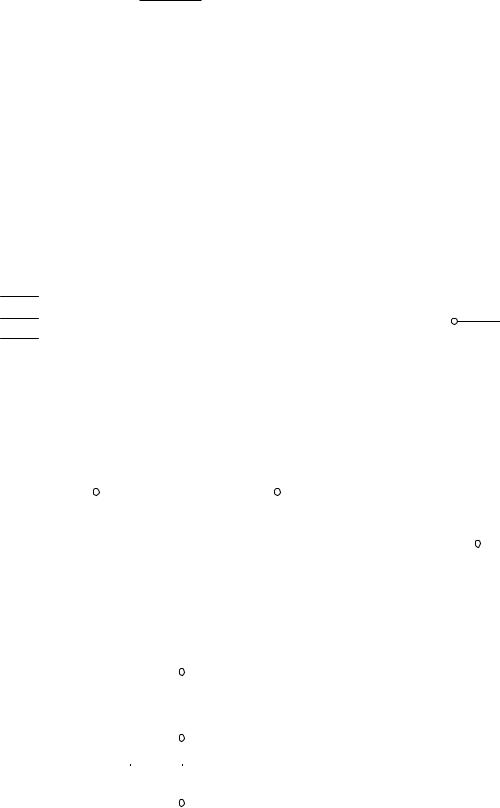

Условные графические обозначения и названия всех исследуемых ЛЭ, а также реализуемые ими БФ приведены на рис. 2. Всем ЛЭ присвоены номера (с № 1 по № 8), которым соответствуют номера соответствующих блоков в лабораторном стенде.

x1

x2 x3

x1

x2 x3

ЛЭ № 1 |

ЛЭ № 2 |

ЛЭ № 3 |

ЗИЛИ |

ЗИ |

НЕ |

|

1 |

|

|

x1 |

|

& |

|

|

|

|

|

|

|

|

|

|

|

1 |

|

|||

|

|

|

|

|

|

|

||||

|

|

x2 |

|

|

|

|

|

|

||

|

|

f1 |

|

|

|

f2 x |

|

|

f3 |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|||||||

|

|

|

x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

f1= x1 V x2 V x3 |

|

|

|

f2= x1 x2 x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

f3= x |

|

|

|||||||||||||||||

|

a) |

|

|

|

|

|

|

|

б) |

|

|

|

|

|

|

в) |

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

ЛЭ № 4 |

|

|

|

|

|

|

|

ЛЭ № 5 |

|

|

|

|

|

|

ЛЭ № 6 |

|

|

||||||||||

ЗИЛИ-НЕ |

|

|

|

|

ЗИ-НЕ |

|

|

|

x1 |

2-2-2-3И-4ИЛИ-НЕ |

|||||||||||||||||

|

|

|

|

|

|

|

|

x1 |

|

|

|

|

|

|

|

|

|

& |

1 |

|

|

|

|||||

|

1 |

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

x2 |

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

f4 |

|

|

|

|

|

f5 |

x3 |

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

x3 |

|

|

|

|

|

|

|

x4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x5 |

|

& |

|

|

|

|

f6 |

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

f4= x1 x2 x3 |

|

|

|

f5= x1 / x2 / x3 |

|

|

|

x6 |

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

д) |

|

|

|

|

|

& |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

г) |

|

|

|

|

|

|

|

|

|

|

x8 |

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x9 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЛЭ № 7 |

|

|

|

|

|

|

|

|

A |

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

x1 |

|

|

3 3И-НЕ |

|

|

|

|

|

|

|

|

|

B |

|

|

|

|

|||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

& |

|

|

|

f7.1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

x2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

f6 = x1 x2 V x3 x4 V x5 x6 V x7 x8 x9 |

||||||||||||||||||

|

x3 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

е) |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

x4 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

& |

|

|

|

f7.2 |

|

|

|

|

|

|

|

|||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

x5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

x6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

|

x7 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

ЛЭ № 8 |

|

|

|||||||||

|

|

|

& |

|

|

|

f7.3 |

|

|

|

|

|

|

||||||||||||||

|

x8 |

|

|

|

|

|

|

|

|

|

МОД-2 |

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||||||

|

x9 |

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

М2 |

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

f7.1= x1 / x2 / x3 |

|

|

|

|

x2 |

|

|

|

|

|

|

f8 |

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||||

|

|

|

|

|

f7.2= x4 / x5 / x6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

f8 = x1 x2 |

|

|

||||||||||||||

|

|

|

|

|

f7.3= x7 / x8 / x9 |

|

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||

|

|

|

|

|

|

|

ж) |

|

|

|

|

|

|

|

|

|

|

|

з) |

|

|

||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 2. Обозначение логических элементов

5

Принципиальные схемы исследуемых ЛЭ приведены на рис. 3 – 9.

Элементы 3ИЛИ (ЛЭ № 1) и 3И (ЛЭ № 2) выполнены на диодах (рис. 3 и 4). Элемент НЕ (ЛЭ № 3) выполнен на базе транзисторного усилителя с общим эмиттером (рис. 5). Элементы 3ИЛИ-НЕ (ЛЭ № 4) и 3И-НЕ (ЛЭ № 5) представляют собой соответственно комбинации диодных схем ИЛИ и И с транзисторными инверторами (рис. 6 и 7).

Логический элемент 2-2-2-3И-4ИЛИ-НЕ с возможностью расширения по ИЛИ (ЛЭ № 6) и элемент 3 3И-НЕ (ЛЭ № 7) являются микросхемами (соответственно типов К155ЛР3 и К155ЛА4) транзисторно-транзисторной логики (ТТЛ). Схемы одного из элементов 3И-НЕ (схемы двух других элементов такие же) и ЛЭ 2-2-2-3И-4ИЛИ-НЕ приведены на рис. 8 и 9.

Элемент № 6 (2-2-2-3И-4ИЛИ-НЕ) ввиду ограниченности лабораторной установки исследуется как элемент 3ИЛИ-НЕ; схема подключения его входов для этого случая приведена на рис. 10. При таком включении

f6 00 x1x1 x2 x2 x3x3x3 x1 x2 x3 .

В работе также исследуется логический элемент МОД-2, реализующий булеву функцию «Сумма по модулю два» (для двух аргументов называемую также неэквивалентность, исключающее ИЛИ – ЛЭ № 8 на рис. 2, з). Для двух переменных такая БФ f (x1, x2 ) x1 x2 равна 1 тогда, когда равна 1 только одна из двух переменных, т. е. когда значения переменных не равны между собой. В общем случае (при n 2 ) значение функции f (x1, x2 ,...,xn ) x1 x2 ... xn определяется арифметической суммой (в двоичной системе счисления) значений переменных, при этом учитывается значение суммы только в младшем разряде. Например, 0 0 0 0; 0 0 1 1;1 1 0 0;1 1 1 1, т. е. такая БФ равна 1 только тогда, когда равны 1 нечетное число переменных.

В лабораторной установке элемент МОД-2 на два входа (исключающее ИЛИ) реализован на элементах 2И-НЕ (две микросхемы К155ЛА3) в соответствии с выражением

|

|

|

|

|

|

|

|

|

|

|

|

|

|

x1 / x1 / x2 / x1 / x2 / x2 . |

|

|

|

|

|

|

|

|

|

|

|

|

x1 |

|

|

f8 x1 x2 x1x2 x1 x2 x1x2 x1 x2 x1x2 |

x2 |

|||||||||||||

Условное изображение микросхемы К155ЛА3, а также схема соединения элементов 2И-НЕ при реализации элемента МОД-2 показаны на рис. 11.

Логические связи И, ИЛИ и НЕ называют основными связями. Совокупность элементарных булевых функций (или соответствующих им логических элементов), с помощью которых можно реализовать любую, как угодно сложную БФ, называют полным базисом (основным). Базис, из которого нельзя исключить ни одной БФ, не утратив свойства полноты, называется минимальным базисом. Базис «И,ИЛИ,НЕ» не является минимальным, так как как из него могут быть удалены функции «И» или «ИЛИ». К минимальным базисам относятся базисы: «И,НЕ» и «ИЛИ,НЕ», а также базисы, «И-НЕ» (штрих Шеффера) и «ИЛИ-НЕ» (стрелка Пирса).

6

x1

x2

x3

x3

f1

f1

Рис. 3. Элемент 3ИЛИ

+  Eп

Eп  –

–

|

|

|

|

|

|

|

|

|

|

|

f3 |

|

|

|

|

|

|

|

|

|

|

|

|

||

x |

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|||||||

|

|

|

|

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Рис. 5. Элемент НЕ

+  Eп

Eп  –

–

x1

x2

f5

x3

Рис. 7. Элемент 3И-НЕ

+ Eп

Eп  –

–

x1

x2

x3

x3

f2

f2

Рис. 4. Элемент 3И |

|

|

+ |

Eп |

– |

x1 |

|

|

x2 |

|

f4 |

|

|

|

x3 |

|

|

Рис. 6. Элемент 3ИЛИ-НЕ

+  Eп

Eп  –

–

x1

x2

x3 |

f7.1 |

Рис. 8. Элемент 3И-НЕ (один из ЛЭ микросхемы К155ЛА4)

7

А |

+ Eп – |

x1 |

|

x2 |

|

x3 x4

x5

f6 x6

f6 x6

x7 x8

x9

В

В

Рис. 9. Элемент 2-2-2-3И-4ИЛИ-НЕ (микросхема К155ЛР3)

& 1

x1 &

&

x2 |

& |

f6 |

|

x3 &

&

A

B

Рис. 10. Схема включения элемента 2-2-2-3И-4ИЛИ-НЕ

8

К155ЛА3

(4 2И-НЕ)

1 |

& |

|

|

|

|

3 |

|

|

|

|

|

|

|

|

2 |

|

|

DD1.1 |

|

|

|

|

DD1.2 |

|

|

& |

x1 |

& |

|

4 |

& |

|||

|

|

6 |

|

|

5 |

|

|

|

|

|

& |

|

|

& |

9 |

|

|

f8 |

|

|

8 |

|

||

10 |

|

|

& |

|

|

|

|

||

|

x2 |

& |

|

|

|

|

|

||

12 |

& |

|

|

|

|

11 |

|

|

|

13 |

|

|

DD1.4 |

|

|

|

|

|

DD1.3

DD1

Рис. 11. Условное изображение микросхемы К155ЛА3 и схема соединения элементов 2И-НЕ при реализации элемента МОД-2

Для всех исследуемых ЛЭ значение логической единицы соответствует напряжению U1 2,0 В . Значению логического нуля для диодных ЛЭ соответствует U 0 0,9 В,

для остальных ЛЭ – U 0 0,4 В. Все входные и выходные напряжения имеют только положительные значения относительно общей шины, т. е. рассматриваемые ЛЭ относятся к так называемой положительной логике.

ОБОРУДОВАНИЕ И ПРИБОРЫ

Образцы интегральных микросхем; лабораторная установка для исследования ЛЭ; дополнительные измерительные приборы; соединительные провода.

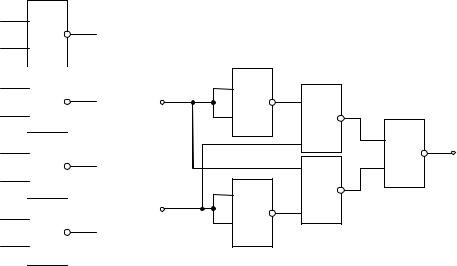

Описание лабораторной установки

Лабораторная установка выполнена в виде переносного стенда, на котором смонтированы платы с исследуемыми логическими элементами (блоки № 1 – № 8), задатчик входных сигналов, нагрузка ЛЭ и часть измерительных приборов. Общий вид стенда показан на рис. 12. Номера блоков соответствуют номерам ЛЭ на рис. 2.

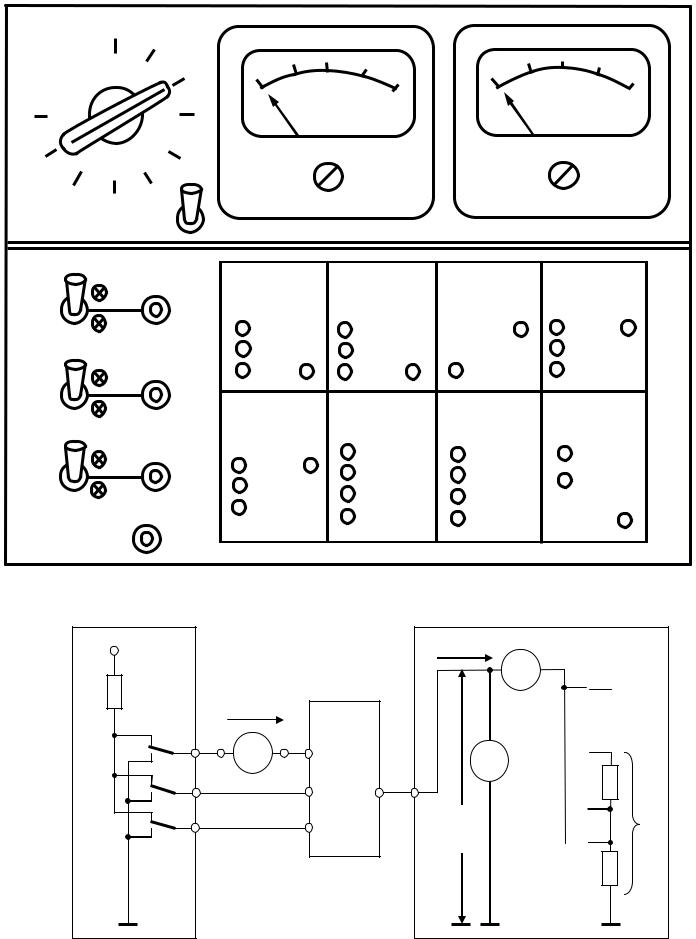

Принципиальная схема задатчика входных сигналов, схема измерительной части установки и схема подключения исследуемого ЛЭ приведены на рис. 13.

9

|

|

1 |

2 |

|

|

|

|

|

|

|

|

|

|

|

П4 |

|

|

|

|

|

|

|

|

|

|

|

|

||

|

3 |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

10 |

|

|

|

4 |

|

|

|

|

|

|

|

mA |

|

|

9 |

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

|

8 |

7 |

6 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

П5 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Блок 1 |

|

Блок 2 |

Блок 3 |

|

Блок 4 |

|

|||

П1 |

|

1 |

1 |

|

3ИЛИ |

|

3И |

|

НЕ |

|

3ИЛИ-НЕ |

|

||

|

0 |

|

x1 |

|

x1 |

|

|

|

|

x1 |

|

|

||

|

|

|

|

y |

|

|

|

|

|

|

||||

|

|

|

|

|

x2 |

x2 |

|

y |

x |

y |

x2 y |

|

||

|

|

1 |

|

|

x3 |

|

x3 |

|

|

|

|

x3 |

|

|

П2 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

2 |

|

Блок 5 |

|

Блок 6 |

Блок 7 |

|

Блок 8 |

|

||||

|

|

0 |

|

|

|

|

||||||||

|

|

|

|

|

|

|

||||||||

|

|

|

|

|

3И-НЕ |

|

3ИЛИ-НЕ |

3И-НЕ |

|

МОД-2 |

|

|||

|

|

|

|

|

|

|

x1 |

|

|

x |

|

x1 |

|

|

|

|

1 |

|

|

x1 |

|

x2 |

|

|

1 |

|

|

|

|

П3 |

|

|

|

|

|

|

x2 |

|

x2 |

|

|

|||

|

|

3 |

|

x2 |

y |

|

|

|

|

|

||||

|

0 |

|

x3 |

|

|

x3 |

|

y |

|

|||||

|

|

|

|

x3 |

|

|

|

|

|

|||||

|

|

|

|

|

|

y |

|

|

y |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Нагрузка |

Н |

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

Рис. 12. Общий вид лабораторной установки |

|

|

|

|

||||||

|

|

+5В |

|

|

|

|

|

|

Iвых |

|

П4 |

|

|

|

|

|

|

|

|

|

|

|

PA1 |

|

|

||||

|

|

|

|

|

|

|

|

|

|

10 |

|

|

||

|

|

R1 |

|

|

Iвх1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

П1 |

|

|

|

ЛЭ |

|

|

|

|

|

|

|

|

|

|

1 |

PA2 |

|

x1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

9 |

|

|

|||

|

|

|

|

|

|

|

|

PV |

|

|

|

|||

|

|

|

П2 |

|

|

|

|

Н |

|

|

|

|

|

|

|

|

|

2 |

|

|

x2 y |

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

П3 |

|

|

|

|

|

|

|

8 |

|

|

|

|

|

|

3 |

|

|

x3 |

|

|

Uвых |

|

|

Rн |

||

|

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

1 |

|

|||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Исследуемый |

|

|

|

|

|

|

|||

|

|

|

|

|

|

|

ЛЭ |

|

|

|

|

|

|

|

|

Задатчик входных |

|

|

|

|

|

Измерительная часть |

|

||||||

|

|

сигналов |

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

|

|

|

|

||

|

|

|

|

|

Рис. 13. Схема подключения ЛЭ |

|

|

|

|

|||||

|

|

|

|

|

|

|

10 |

|

|

|

|

|

|

|