-

Основные логические функции и элементы.

Логические элементы — устройства, предназначенные для обработки информации в цифровой форме (последовательности сигналов высокого — «1» и низкого — «0» уровней в двоичной логике). Логические элементы выполняют логическую функцию (операцию) над входными сигналами (операндами, данными).

Функции:

-

«Не» - отрицание.

-

«И» - логическое умножение (конъюнция).

-

«Или» - логическое сложение (дизъюнкция).

-

Декодер. Десятичный дешифратор.

Декодеры (дешифраторы) позволяют преобразовывать одни виды бинарных кодов в другие. Например, преобразовывать позиционный двоичный код в линейный восьмеричный или шестнадцатеричный.

Десятичный код обычно отображается одним битом на одну десятичную цифру. Это классический пример, иллюстрирующий, что нулями и единицами описываются не только двоичные коды. В десятичном коде десять цифр, поэтому для отображения одного десятичного разряда требуется десять выходов дешифратора. Около каждого разряда десятичного кода подписана десятичная цифра, которую отображает логическая единица в этом разряде. Сигнал с этих выводов дешифратора можно подать на десятичный индикатор. В простейшем случае над светодиодом можно просто подписать индицируемую цифру. На входе дешифратора двоичный код записывается в соответствии с правилами двоичной системы счисления.

-

Сумматор.

Сумма́тор — устройство, преобразующее информационные сигналы (аналоговые или цифровые) в сигнал, эквивалентный сумме этих сигналов.

Сумматор имеет вход расширения или вход переноса, который используется для объединения нескольких сумматоров с целью увеличения разрядности. Если на этот вход приходит единица, то выходная сумма увеличивается на единицу, если приходит ноль, то выходная сумма не увеличивается. Если используется одна микросхема сумматора, то на её вход переноса необходимо подать ноль.

-

Бистабильные схемы.

Бистабильная ячейка - электронная схема, находящаяся в одном из двух устойчивых состояний (логическая 1 или логический 0), пока через один из своих входов не получит импульс, при помощи которого она переключается в другое состояние.

Триггер (триггерная система) — класс электронных устройств, обладающих способностью длительно находиться в одном из двух устойчивых состояний и чередовать их под воздействием внешних сигналов. Каждое состояние триггера легко распознаётся по значению выходного напряжения. По характеру действия триггеры относятся к импульсным устройствам — их активные элементы (транзисторы, лампы) работают в ключевом режиме, а смена состояний длится очень короткое время.

Отличительной особенностью триггера как функционального устройства является свойство запоминания двоичной информации. Под памятью триггера подразумевают способность оставаться в одном из двух состояний и после прекращения действия переключающего сигнала. Приняв одно из состояний за «1», а другое за «0», можно считать, что триггер хранит (помнит) один разряд числа, записанного в двоичном коде.

-

RS-триггер.

RS триггер получил название по названию своих входов. Вход S (Set — установить англ.) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset — сбросить англ.) позволяет сбрасывать выход триггера Q (Quit — выход англ.) в нулевое состояние (записывать ноль).

Пусть на входы R и S подаются единичные потенциалы. Если на выходе верхнего логического элемента "2И-НЕ" Q присутствует логический ноль, то на выходе нижнего логического элемента "2И-НЕ" появится логическая единица. Эта единица подтвердит логический ноль на выходе Q. Если на выходе верхнего логического элемента "2И-НЕ" Q первоначально присутствует логическая единица, то на выходе нижнего логического элемента "2И-НЕ" появится логический ноль. Этот ноль подтвердит логическую единицу на выходе Q. То есть при единичных входных уровнях схема RS триггера работает точно так же как и схема на инверторах.

Подадим на вход S нулевой потенциал. Согласно таблице истинности логического элемента "И-НЕ" на выходе Q появится единичный потенциал. Это приведёт к появлению на инверсном выходе триггера нулевого потенциала. Теперь, даже если снять нулевой потенциал с входа S, на выходе триггера останется единичный потенциал. То есть мы записали в триггер логическую единицу.

-

Синхронный rs-триггер.

Схема RS триггера позволяет запоминать состояние логической схемы, но так как в начальный момент времени может возникать переходный процесс (в цифровых схемах этот процесс называется "опасные гонки"), то запоминать состояния логической схемы нужно только в определённые моменты времени, когда все переходные процессы закончены.

Это означает, что большинство цифровых схем требуют сигнала синхронизации (тактового сигнала). Все переходные процессы в комбинационной логической схеме должны закончиться за время периода синхросигнала, подаваемого на входы триггеров. Триггеры, запоминающие входные сигналы только в момент времени, определяемый сигналом синхронизации, называются синхронными. Для того чтобы отличать от них рассмотренные ранее варианты (RS триггер и триггер Шмитта) эти триггеры получили название асинхронных.

Для этого нам потребуется схема, пропускающая входные сигналы только при наличии синхронизирующего сигнала.

-

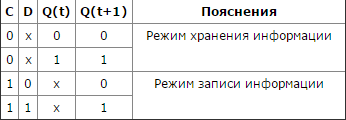

Статический D-триггер.

Название D триггера происходит от английского слова delay — задержка. Конкретное значение задержки определяется частотой следования импульсов синхронизации.

-

Динамический D-триггер.

Основным недостатком простейшего D-триггера (защелки), является наличие режима "прозрачности". Пока на входе синхронизации присутствует высокий потенциал, триггер записывает входную информацию. Для того, чтобы избежать прохождения входного сигнала на выход схемы приходится на вход триггера подавать очень узкие импульсы.

Фронт сигнала синхронизации, в отличие от высокого (или низкого) потенциала, не может длиться продолжительное время. В идеальном случае длительность фронта импульса равна нулю. Поэтому в триггере, запоминающем входную информацию по фронту не нужно предъявлять требования к длительности тактового сигнала.

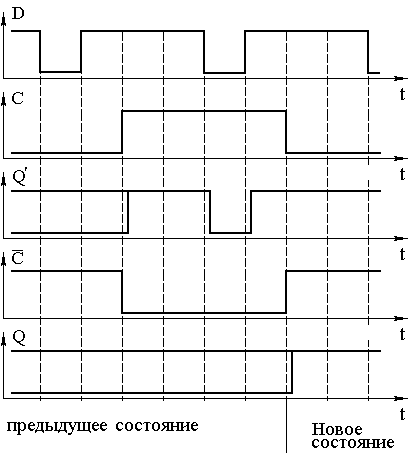

Динамический D триггер, запоминающий входную информацию по фронту, может быть построен из двух статических D триггеров.

На этих временных диаграммах обозначение Q' соответствует сигналу на выходе первого статического D триггера. Так как на вход синхронизации второго статического D триггера тактовый сигнал поступает через инвертор, то когда первый триггер находится в режиме хранения, второй пропускает сигнал на выход схемы. И наоборот, когда первый D триггер пропускает сигнал с входа схемы на свой выход, то второй находится в режиме хранения.

Обратите внимание, что сигнал на выходе всей схемы D триггера в целом не зависит от сигнала на входе "D". Если первый D триггер пропускает сигнал данных со своего входа на выход, то второй статический D триггер в это время находится в режиме хранения и поддерживает на выходе предыдущее значение сигнала, то есть сигнал на выходе схемы тоже не может измениться.

В результате проведённого анализа временных диаграмм мы определили, что сигнал в схеме, приведенной на рисунке 1 запоминается только в момент изменения сигнала на синхронизирующем входе "C" с единичного потенциала на нулевой.

-

T-триггер. Суммирующий асинхронный счётчик.

T-триггер — это счетный триггер. У данного триггера имеется только один вход. Принцип работы T-триггера заключается в следующем. После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T-триггер как бы подсчитывает количество импульсов, поступивших на его вход. Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

T-триггеры строятся только на базе двухступенчатых триггеров, подобных рассмотренному ранее D-триггеру. Использование двух триггеров позволяет избежать неопределенного состояния схемы при разрешающем потенциале на входе синхронизации "C", так как счетные триггеры строятся при помощи схем с обратной связью. T-триггер можно синтезировать из любого двухступенчатого триггера.

Счётчик представляет собой несколько последовательно включенных счётных триггеров. Напомним, что по каждому входному импульсу счётный триггер изменяет своё состояние на противоположное.

Рассмотрим работу счетчика. Итак, в счетчике “000”. Подали первый счетный импульс. По его срезу триггер Т1 переключится в инверсное состояние ‘1’. На входе второго триггера сформировался фронт с ‘0’ на ‘1’. Следовательно, триггер T2 не переключается.

Подадим второй счетный импульс. По его срезу T1 переключается в инверсное состояние 0. На выходе сформировался перепад с ‘1’ на ‘0’ (срез). Следовательно, T2 переключается в инверсное состояние ‘1’. На входе третьего триггера образовался перепад с ‘0’ на ‘1’ (фронт). Следовательно, третий триггер не переключается. В счетчик записано число 2.

Обратите внимание, что младший разряд переключается каждым счетным импульсом. Каждый следующий разряд переключается, когда во всех предыдущих разрядах ‘1’.