- •Конвейеризация вычислений. Конвейер команд, конвейер данных.

- •Суперскаляризация

- •37.Классификация вс в зависимости от числа потоков команд и данных: окод (sisd), окмд (simd), мкод (misd), мкмд (mimd).

- •38.Классификация многопроцессорных вс. Сравнительные характеристики, аппаратные и программные особенности.

- •Общая память uma

- •Распределённая память numa

- •Классификация:

- •40.Системная bios, интерфейс, тест начального включения, начальная загрузка системные вызовы (прерывания).

- •Тест начального включения

- •Начальная загрузка системные вызовы (прерывания).

33.Переключение задач. Переключение между реальным и защищенным режимами.

Ответ:

Переключение ЦП из реального в защищенный режим осуществляется загрузкой в системный сегмент CR0 слова с единичным значением бита PE до переключения.

В память должны быть проинициализированы локальная и глобальная таблицы дескрипторов.

Переключение ЦП из защищенного в реальный возможно не только через аппаратные средства, как в процессоре i80286, но и с помощью сброса единичного бита PE в регистре CR0.

До этого переключения необходимо загрузить в сегментный регистр селектора дескриптор, описывающий свойства сегмента стандартного реального режима.

34. Современные процессоры.

Ответ:

Процессор – это основное устройство ЭВМ, выполняющее логические и арифметические операции, и осуществляющее управление всеми компонентами ЭВМ.

Современный процессор – это сложное и высокотехнологическое устройство, включающее в себя все самые последние достижения в области вычислительной техники и сопутствующих областей науки.

Процессоров состоит из:

|

|

|

|

И характеризуется следующими параметрами:

|

|

|

|

|

|

|

|

|

|

Ядро процессора – это его основная часть, содержащая все функциональные блоки и осуществляющая выполнение всех логических и арифметических операций.

ЦП состоит из нескольких функциональных блоков:

-

блока выборки инструкций;

-

блоков декодирования инструкций;

-

блоков выборки данных;

-

управляющего блока;

-

блоков выполнения инструкций;

-

блоков сохранения результатов;

-

блока работы с прерываниями;

-

ПЗУ, содержащего микрокод;

-

набора регистров;

-

счетчика команд.

(продолжение вопроса 34)

Блок выборки инструкций осуществляет считывание инструкций по адресу, указанному в счетчике команд. Обычно, за такт он считывает несколько инструкций.

Для того чтобы блок выборки инструкций работал оптимально, в ядре процессора имеется предсказатель переходов.

Предсказатель переходов пытается определить, какая последовательность команд будет выполняться после совершения перехода.

Блоки декодирования – это блоки, которые занимаются декодированием инструкций, т.е. определяют, что надо сделать процессору, и какие дополнительные данные нужны для выполнения инструкции (задача эта построенных на базе концепции CISC)

Блоки выборки данных осуществляют выборку данных из КЭШ-памяти или ОЗУ, необходимых для выполнения текущих инструкций.

Обычно, каждое процессорное ядро содержит несколько блоков выборки данных.

Управляющий блок на основании декодированных инструкций управляет работой блоков выполнения инструкций, распределяет нагрузку между ними, обеспечивает своевременное и верное выполнение инструкций. Это один из наиболее важных блоков ядра процессора.

Блоки выполнения инструкций включают в себя несколько разнотипных блоков:

ALU – арифметическое логическое устройство;

FPU – устройство по выполнению операций с плавающей точкой;

Блоки для обработки расширения наборов инструкций – это дополнительные инструкции используются для ускорения обработки потоков данных, шифрования и дешифрования, кодирования видео и так далее. Для этого в ядро процессора вводят дополнительные регистры и наборы логики.

Блок сохранения результатов обеспечивает запись результата выполнения инструкции в ОЗУ по адресу, указанному в обрабатываемой инструкции.

Блок работы с прерываниями. Работа с прерываниями – одна из важнейших задач процессора, позволяющая ему своевременно реагировать на события, прерывать ход работы программы и выполнять требуемые от него действия. Благодаря наличию прерываний, процессор способен к многозадачности.

Регистры – сверхбыстрая оперативная небольшого объема для временного хранения промежуточных результатов выполнения инструкций.

Регистры процессора делятся на два типа:

-

Регистры общего назначения - используются при выполнении арифметических и логических операций, или специфических операций дополнительных наборов инструкций

-

Специальные регистры - содержат системные данные, необходимые для работы процессора (регистры управления, регистры системных адресов, регистры отладки и т.д.).

Счетчик команд – регистр, содержащий адрес команды, которую процессор начнет выполнять на следующем такте работы.

35.Назначение и характеристики ВС. Организация вычислений в вычислительных системах. ЭВМ параллельного действия, понятия потока команд и потока данных.

Ответ:

Вычислительная система – это совокупность взаимосвязанных и взаимодействующих процессоров или ЭВМ.

Отличие ВС от классических ЭВМ является наличие в ней нескольких вычислителей, реализующих параллельную обработку.

Параллельная обработка повышает быстродействие, надежность и достоверность функционирования системы.

В качестве элементов ВС выступают отдельные ЭВМ и процессоры. В ВС, относящихся к классу больших систем, можно рассматривать структуры технических, программных средств, структуры управления и т.д.

ВС делаться на:

-

Многомашинные ВС.

Несколько ЦП, входящих в систему, не имеют общей ОП, а имеет каждый свою.

Каждый компьютер имеет классическую архитектуру. Достигается мах. эффект при выполнении задачи, разбитой на подсистемы, сколько компьютеров в системе.

-

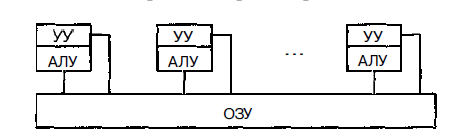

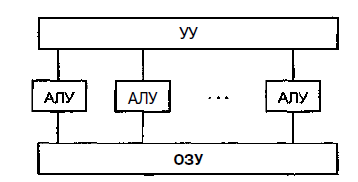

Многопроцессорные ВС.

Здесь параллельно может быть организовано много потоков команд и много потоков данных. Таким образом параллельно могут выполняться несколько фрагментов задачи.

Несколько ЦП имеет общую ОП.

-

Архитектура с параллельным процессором.

Здесь несколько АЛУ работают под одним УУ. Это означает, множество данных могут обрабатываться по одной программе, т.е. по одному потоку команд.

Поток команд - естественная последовательность команд, проходящая по конвейеру процессора.

Поток данных - это информация, передаваемая через некоторое соединение от источника к приемнику.

36. Конвейеризация вычислений. Конвейер команд, конвейер данных. Суперскаляризация.

Ответ:

Конвейеризация вычислений. Конвейер команд, конвейер данных.

Каждая инструкция, выполняемая процессором, последовательно проходит все блоки ядра, в каждом из которых совершается своя часть действий, необходимых для выполнения инструкции. Если приступать к обработке новой инструкции только после завершения работы над первой инструкцией, то большая часть блоков ядра процессора в каждый момент времени будет простаивать, а, следовательно, возможности процессора будут использоваться не полностью.

Для решения этой проблемы выполнение инструкций построено по принципу конвейера, то есть по мере освобождения блоков ядра, они загружаются обработкой следующей инструкции, не дожидаясь пока предыдущая инструкция выполнится полностью.

Так как процессор выполняет команды непрерывно, то, в идеале, он мог бы быть занят на 100%, при этом, чем длиннее был бы конвейер, тем больший выигрыш в производительности был бы получен. Но на практике это не так.

-

В инструкциях часто встречаются переходы. При этом пока команда условного перехода не будет обработана полностью, конвейер не сможет начать выполнение новой команды, так как не знает, по какому адресу она находится.

Поэтому в ядро процессора вводятся блоки предсказания условных переходов. Основная задача этих блоков – определить, когда будет совершен условный переход и какие команды будут выполнены после совершения условного перехода.

-

Часто обрабатываемые инструкции – взаимосвязаны, то есть одна из инструкций требует в качестве исходных данных результата выполнения другой инструкции.

Поэтому процессоры могут анализировать код на несколько инструкций вперед и, например, параллельно с первой инструкцией обработать третью инструкцию, которая никак не зависит от первых двух.

Суперскаляризация

Суперскалярность – архитектура вычислительного ядра, при которой наиболее нагруженные блоки могут входить в нескольких экземплярах.

Например: в ядре процессора блок выборки инструкций может нагружать сразу несколько блоков декодирования.

В этом случае блоки, выполняющие более сложные действия и работающие дольше, за счет параллельной обработки сразу нескольких инструкций не будут задерживать весь конвейер.

Однако параллельное выполнение инструкций возможно, только если эти инструкции – независимые.

Структурная схема ядра конвейера гипотетического процессора, построенного с использованием принципа суперскалярности, в нем в каждом ядре процессора работает несколько блоков декодирования, несколько блоков выборки данных и несколько блоков выполнения инструкций.

37.Классификация вс в зависимости от числа потоков команд и данных: окод (sisd), окмд (simd), мкод (misd), мкмд (mimd).

Ответ:

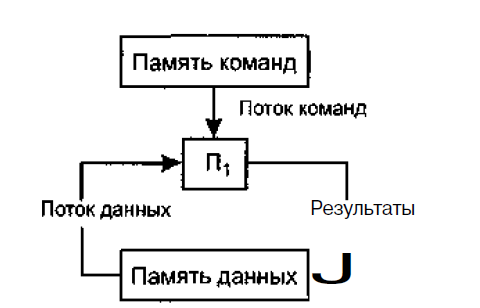

Архитектура ОКОД (SISD) - одиночный поток команд – одиночный поток данных.

Охватывает все однопроцессорные и одномашинные варианты схем.

Все ЭВМ классической структуры относятся

к этому классу.

Здесь параллелизм вычислений обеспечивается путем совмещения выполнения операций отдельными блоками АЛУ, а так же параллельной работой устройств ввода-вывода и процессора.

Архитектура ОКМД (SIMD) - одиночный поток команд – множественный поток данных.

Предполагает создание структур векторной и матричной обработки.

Здесь системы строятся однородными, т.е. процессорные элементы, входящие в систему, идентично, и все они управляются одной и той же последовательностью команд. Однако каждый процессор обрабатывает свой поток данных.

Структуры ВС этого типа специализируются в суперЭВМ.

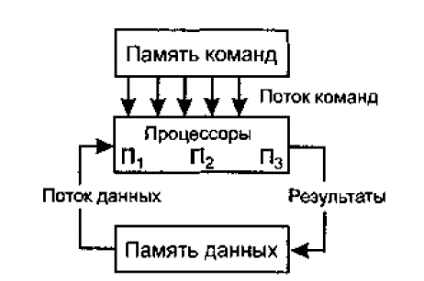

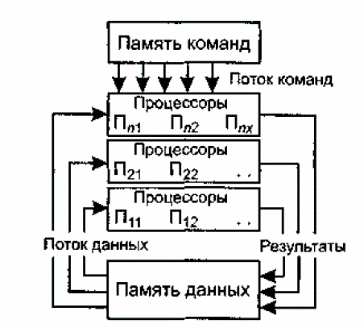

Архитектура МКОД (MISD) - множественный поток команд – одиночный поток данных.

Предполагает построение процессорного конвейера, в котором результаты обработки передаются от одного процессора к другому по цепочки.

Здесь конвейеры должны образовывать группы процессоров. Однако при переходе на системный уровень очень трудно выяснить подобный регулярный характер в универсальных вычислениях.

Архитектура МКМД (MIMD)

- множественный поток команд –

множественный поток данных.

Предполагает, что все процессоры системы работают по своим программам с собственным потоком команд. В простейшем случае они могут быть автономны и независимы.

Здесь возможно согласовывать работы ЭВМ (процессоров), когда каждый элемент делает часть общей задачи.

Подобные системы могут быть многопроцессорными и многомашинными.