3 лаба по ПДИУС

.docxМинистерство образования и науки Российской Федерации

Федеральное государственное бюджетное образовательное учреждение

высшего образования

«Пермский национальный исследовательский политехнический университет»

Кафедра автоматики и телемеханики

ОТЧЁТ ПО ЛАБОРАТОРНОЙ РАБОТЕ № 3

|

по дисциплине: Передача данных в информационно – управляющих системах Тема: Исследование систем передачи данных, использующих циклические (БЧХ) коды Вариант № 3 |

|

|

|

|

|

|

Выполнили студенты гр. _________________________________ (дата, подпись) _________________________________ (дата, подпись) Проверил старший преподаватель кафедры АТ Кулагина М. М. _________________________________ (оценка) _________________________________ (дата, подпись) |

Пермь 2018 г.

Цель работы:

1. Ознакомиться c функциональной моделью системы передачи данных (СПД), использующей циклические (БЧХ) коды, реализованной в среде MATLAB.

2. Исследовать принципы построения функциональных моделей кодеров циклических систематических кодов (ЦСК).

3. Исследовать принципы построения функциональных моделей декодеров Меггита в режимах обнаружения и исправления ошибок.

Вариант задания для лабораторной работы:

В соответствии с вариантом №1 определим используемые в СПД коды БЧХ:

Код №1 (7,3,4): g(x) = x4+x2+x+1

Код №2 (14,10,3): g(x) = x4+x3+1

Ход выполнения работы:

Целью является построение структур кодеров и декодеров БЧХ кодов и анализ их функционирования с использованием временных диаграмм.

1. Построение функциональной модели СПД с заданными параметрами для первого кода (7,3,4) g(x) = x4+x2+x+1

Число избыточных символов k = 4

Число информационных символов m = 3

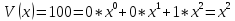

Зададимся

Тогда

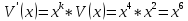

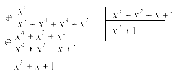

Найдем

:

:

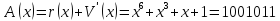

Кодовый

вектор

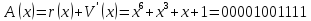

1.2 Построение блока деления на полином в составе кодера

Блок Divider реализует

блок деления на полином. Перестроим

структуру блока в соответствии с кодом

и получим временные диаграммы его

функционирования.

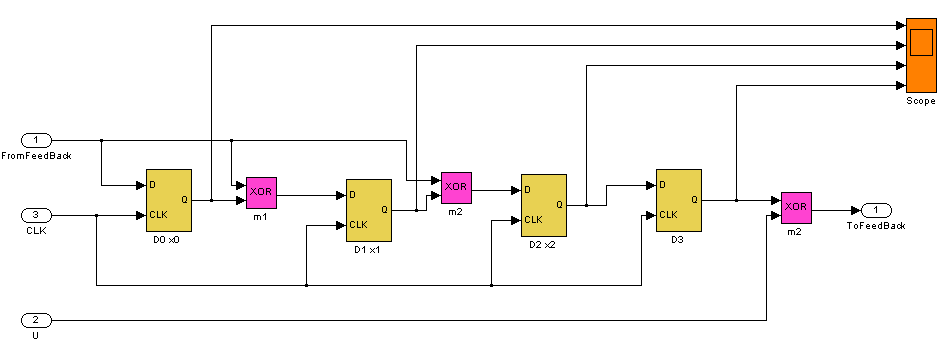

Рисунок 1 – Блок Divider СПД модели блока кодера

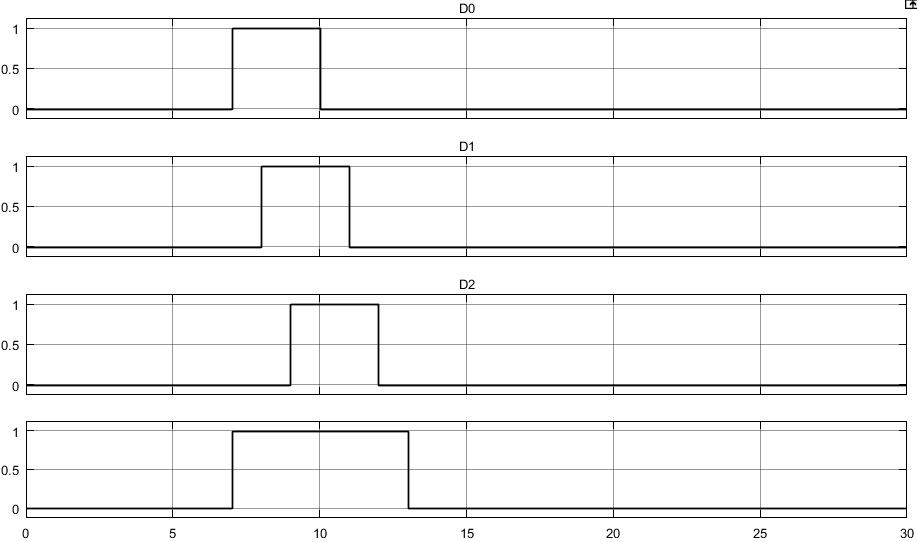

Рисунок 2 – Временная диаграмма в блоке Divider

|

№ такта |

Состояние ключей |

D0 |

D1 |

D2 |

D3 |

V(Выход) |

|

0 |

k1 |

0 |

0 |

0 |

0 |

|

|

1 |

1 |

1 |

1 |

0 |

1 |

|

|

2 |

0 |

1 |

1 |

1 |

0 |

|

|

3 |

1 |

1 |

0 |

1 |

0 |

|

|

4 |

k2 |

0 |

1 |

1 |

0 |

1 |

|

5 |

0 |

0 |

1 |

1 |

0 |

|

|

6 |

0 |

0 |

0 |

1 |

1 |

|

|

7 |

0 |

0 |

0 |

0 |

1 |

1.2 Построение

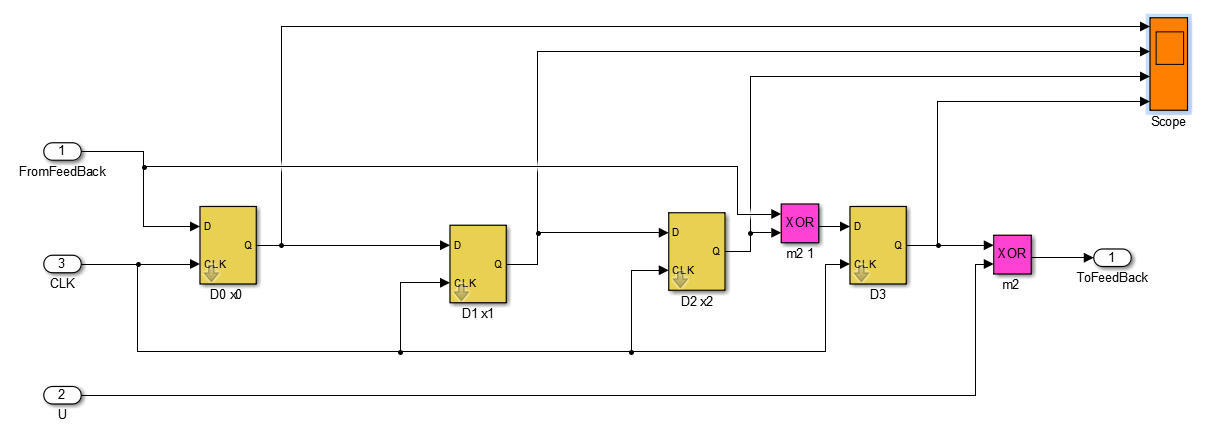

декодера

Рисунок

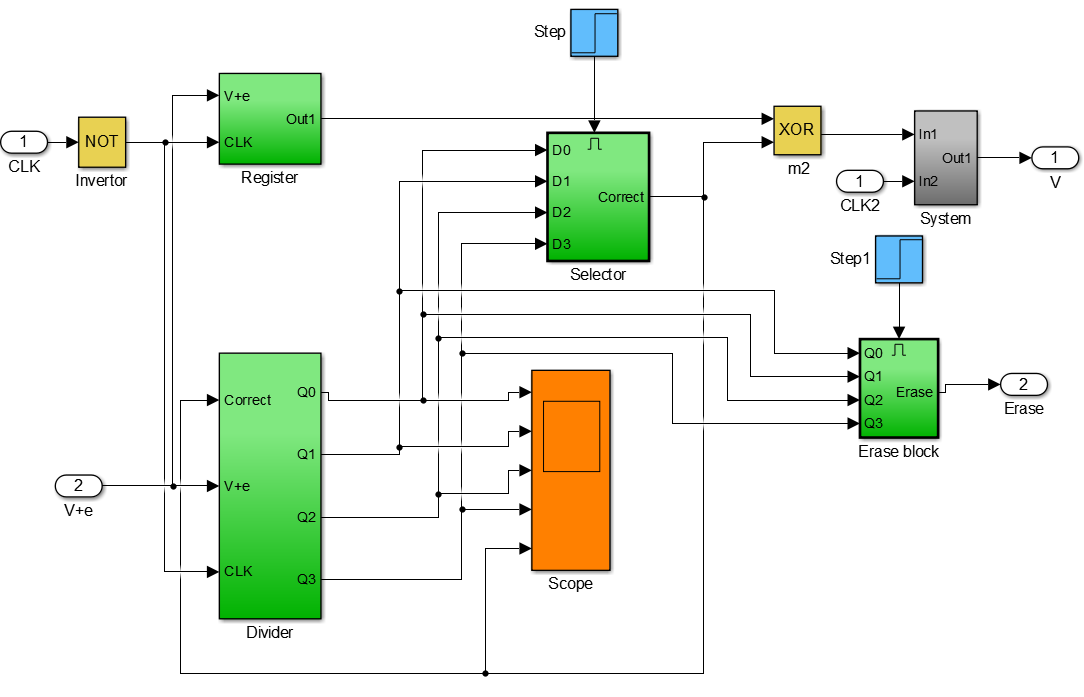

3 – Схема декодера

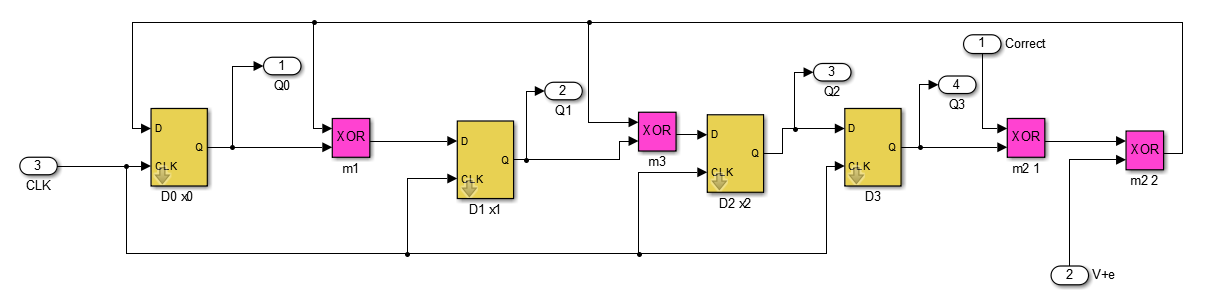

Рисунок 4 – Схема блока Divider декодера

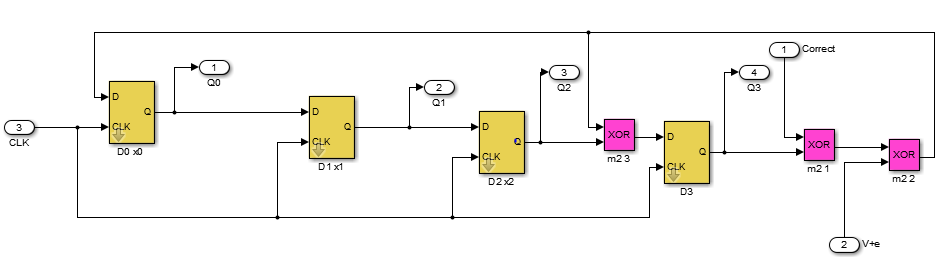

Register

– Сдвиговый регистр, «запоминающий»

пришедший кодовый вектор.

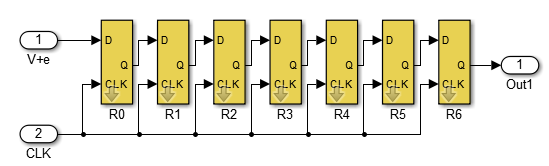

Рисунок 5 – Сдвиговый регистр

Selector – Селектор, настраиваемый на определенные синдромы (в соответствии с выбранным кодом).

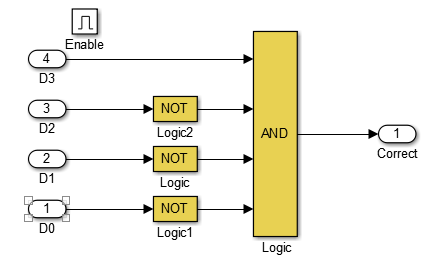

Рисунок 6 – Селектор блока декодера

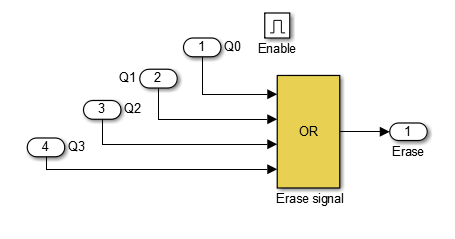

Eraseblock – формирует сигнал стирания.

Рисунок 7 – Блок формирования сигнала на стирание

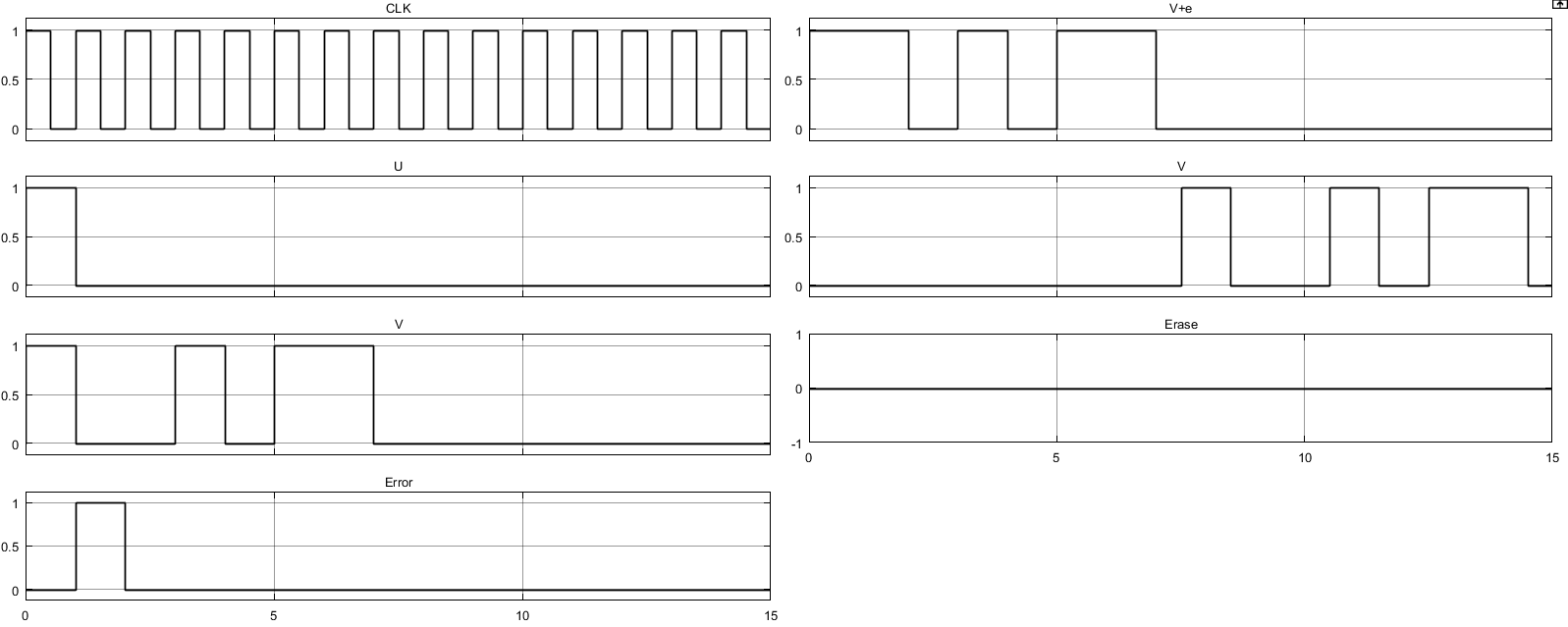

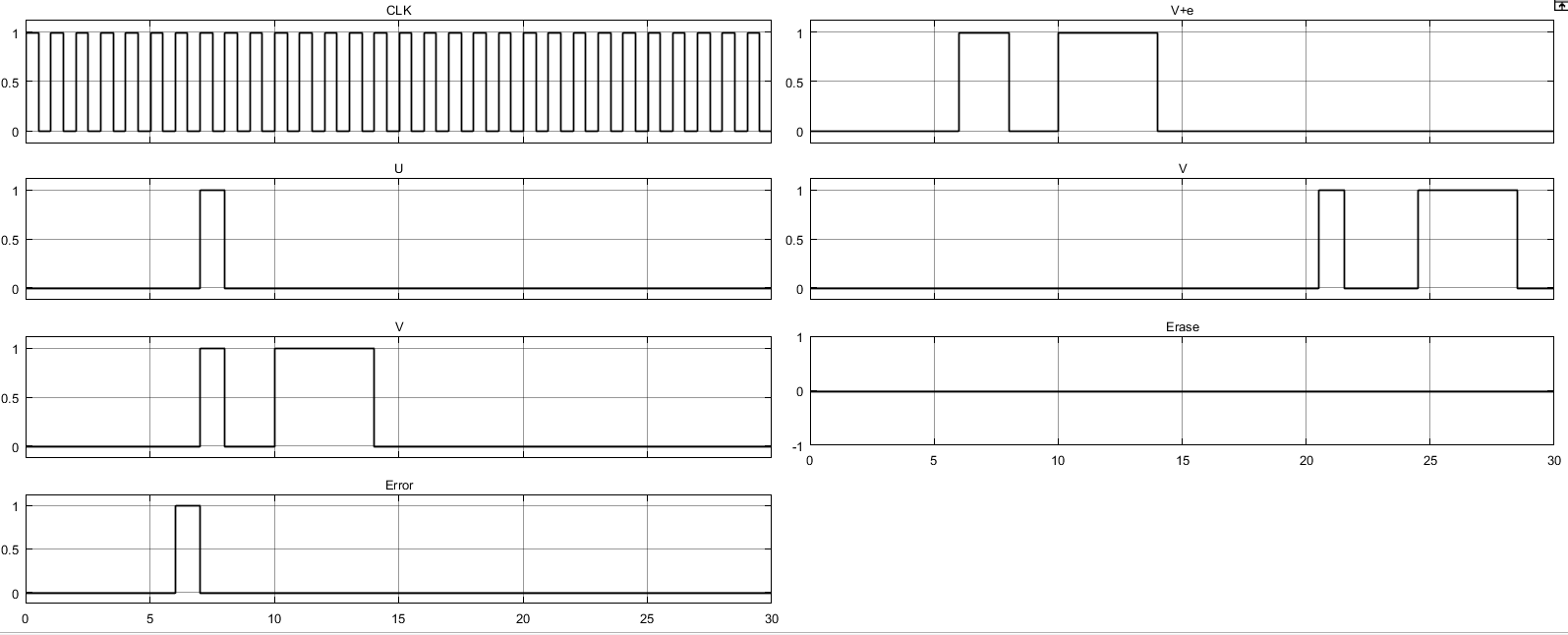

Рисунок 8 – Исправление однократной ошибки

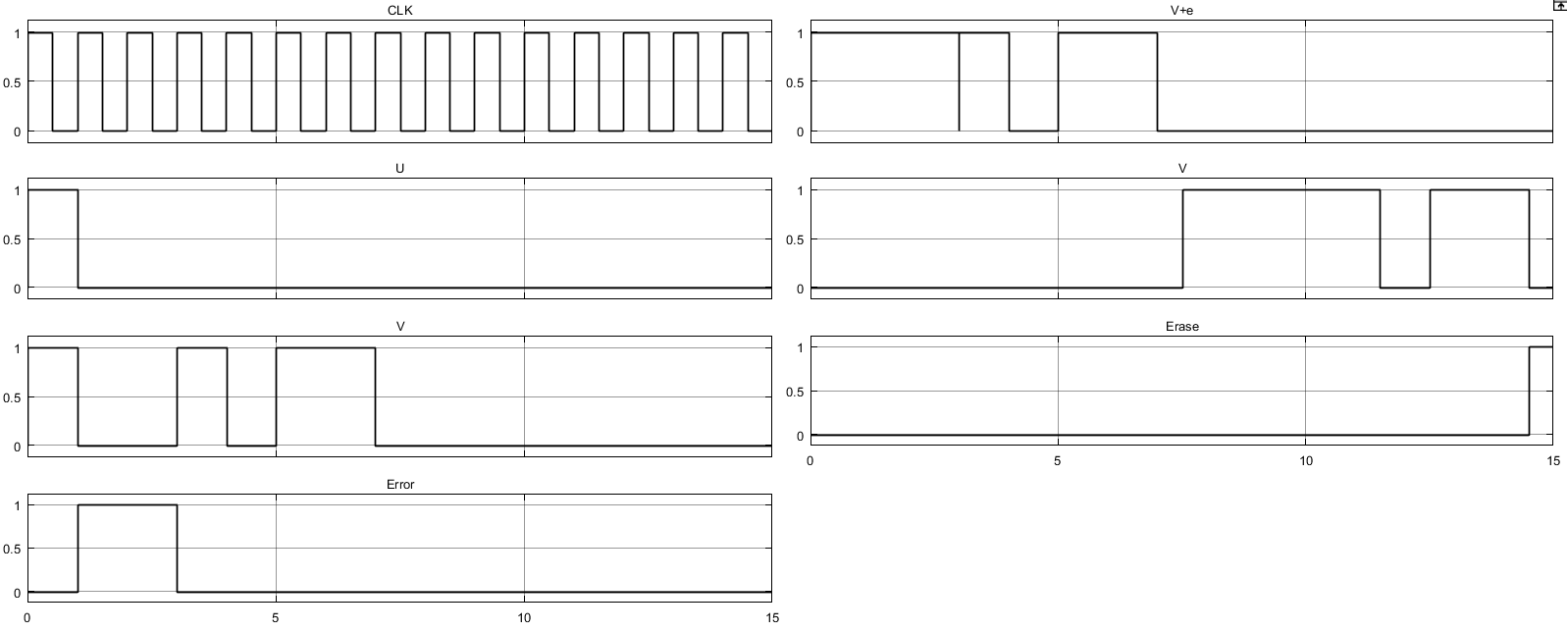

Рисунок 8 – Обнаружение и стирание двухкратной ошибки

2. Построение функциональной модели СПД с заданными параметрами для второго кода (12,8,3) g(x) = x4+x3+1

Число избыточных символов k = 4

Число информационных символов m = 10

Зададимся

Тогда

Найдем

:

:

Кодовый

вектор

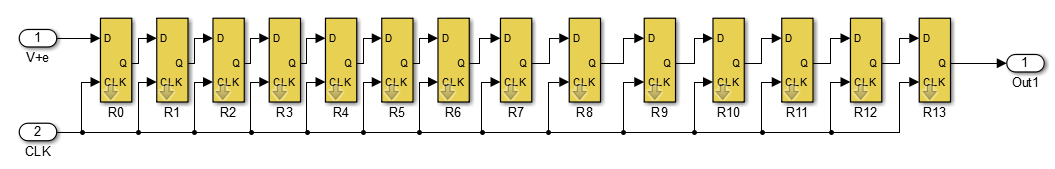

Рисунок 9 – Описание блока Divider кодера

Рисунок 10 – Блок Divider

декодера

Рисунок 11 - Сдвиговый регистр

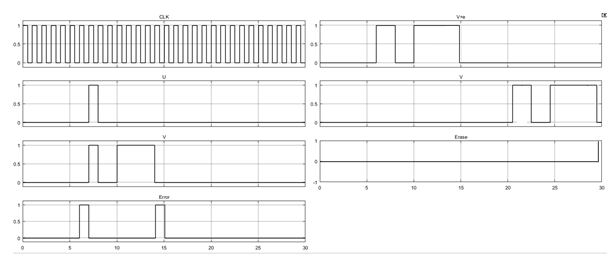

Рисунок 12 - Временная диаграмма в блоке

Divider

Рисунок 13 - Исправление однократной ошибки

Рисунок 14 – Обнаружение двухкратной ошибки

Вывод:

В процессе выполнения лабораторной работы были изучены принципы построения циклических кодов(БЧХ). Разработан кодер и декодер циклических кодов с последующей проверкой передачи ошибки без стирания и со стиранием.