Опорний конспект

Тема 1.3. Типові функціональні вузли комбінаційних цифрових пристроїв.

Дешифратор (Decoder)

Дешифратором називається функціональний вузол комп’ютера призначений для перетворення кожної комбінації вхідного двійкового коду в керуючий сигнал лише на одному із “m” виходів. Цей сигнал називається активним.

Якщо дешифратор має n входів і m=2n – виходів, то такий дешифратор є повним. Якщо число виходів менше 2n, то дешифратор називають неповним.

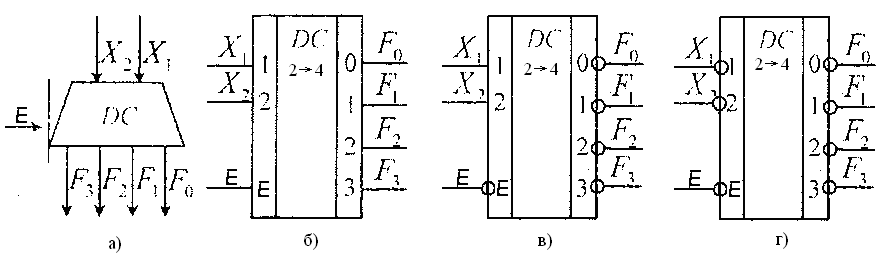

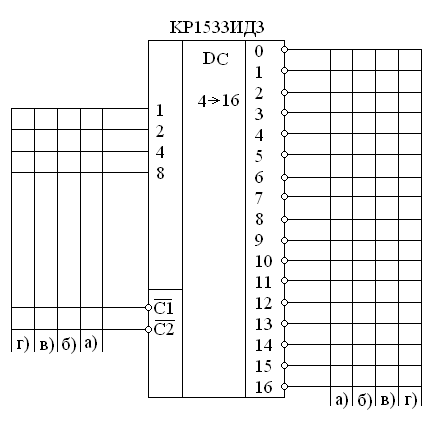

Умовно графічне позначення дешифратора приведене на рис. 1.

Рис. 1. УГП дешифратора: а) на функціональних схемах; б, в, г) на принципіальних схемах.

У схему дешифраторів

вбудовуються один, два або три стробуючих

(дозволяючих) входи, наприклад Е рис. 1

або

![]() рис.

2. при наявності дозволу

рис.

2. при наявності дозволу

![]() дешифратор працює, при його відсутності

всі виходи дешифратора пасивні.

дешифратор працює, при його відсутності

всі виходи дешифратора пасивні.

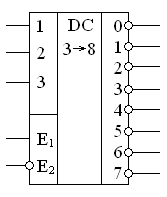

Вказати рівні сигналів:

Виходи DC активні Виходи DC пасивні

Е1= ____________ Е1= ____________

Е2= ____________ Е2= ____________

Рис. 2

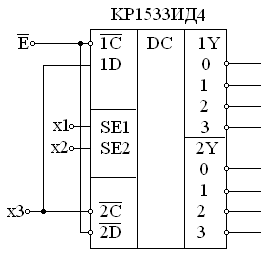

Використання

входів дозволу

![]() дає змогу досить просто будувати схему

дешифратора більшої розрядності вхідного

коду. З’єднання двох три розрядних

дешифраторів дає декодування чотирозрядного

коду, показано на рис. 3. Інтегральна

мікросхема КР1533ИД4 – це здвоєний

дешифратор 2→4 з інверсними виходами.

Цю ІС дешифратора можна використовувати

для побудови 8-ми канального дешифратора,

рис. 4.

дає змогу досить просто будувати схему

дешифратора більшої розрядності вхідного

коду. З’єднання двох три розрядних

дешифраторів дає декодування чотирозрядного

коду, показано на рис. 3. Інтегральна

мікросхема КР1533ИД4 – це здвоєний

дешифратор 2→4 з інверсними виходами.

Цю ІС дешифратора можна використовувати

для побудови 8-ми канального дешифратора,

рис. 4.

Рис. 3. Рис. 4.

В комп'ютерах дешифратори використовують для виконання таких операцій:

-

дешифрації коду операції, записаного в регістр команд процесора, що забезпечує вибір потрібної мікропрограми;

-

перетворення коду адреси операнда в команді в керуючі сигнали вибору заданої комірки пам'яті в процесі записування або читання інформації;

-

забезпечення візуалізації на зовнішніх пристроях;

-

реалізації логічних операцій та побудови мультиплексорів і демультиплексорів.

Завдання для самоконтролю

Задача 1. Використовуючи таблицю істинності для дешифратора 2→4 записати логічні вирази.

|

х1 |

х2 |

F1 |

F2 |

F3 |

F4 |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

1 |

F1=_______________________________________

F2=_______________________________________

F3=_______________________________________

F4=_______________________________________

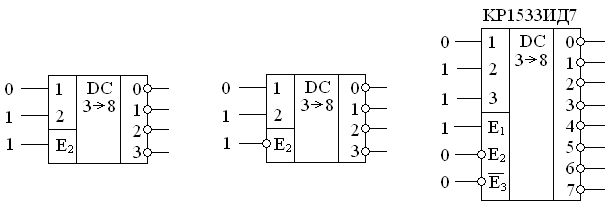

Задача

2. Аналізуючи

рис.4 кожну комбінацію вхідного двійкового

коду (х1,х2,х3),

при

![]() ,

вказати порядковий номер виходів,

позначивши їх через уі(і=0,1,2,…,7).

,

вказати порядковий номер виходів,

позначивши їх через уі(і=0,1,2,…,7).

Задача 3. Який вихід дешифратора буде активним на рис. 5. Вказати на виходах DC активні та пасивні рівні сигналів.

Рис. 5.

Задача 4. Вказати двійковий код на інформаційних входах та рівні сигналів на стробуючих входах, а також на виходах дешифратора, для активізації 9, 12, 5, 14 виходів, рис. 6.

а) активний 9 вихід

б) активний 12 вихід

в) активний 5 вихід

г) активний 14 вихід

Рис. 6.

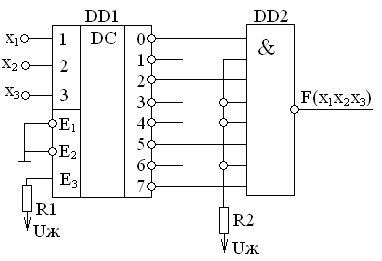

Задача 5. Запишіть логічну функцію в МДНФ, яку виконує наступна електрична принципова схема на рис. 7а, для чого спочатку дати відповіді на запитання.

Рис. 7a. DD1 – KP1533ИД7, DD2 – KP1533ЛА2