- •4 Разработка модуля дискретного ввода / вывода

- •4.1 Анализ технических характеристик сигналов

- •4.2 Анализ режима обмена с модулем

- •4.3 Разработка структурной схемы

- •4.4 Выбор элементов и разработка принципиальной схемы

- •4.5 Расчет надежности модуля дискретного ввода / вывода

- •4.6 Разработка программного модуля инициализации

4 Разработка модуля дискретного ввода / вывода

4.1 Анализ технических характеристик сигналов

В таблице 4.1 указаны технические характеристики входных и выходных сигналов.

Таблица 4.1- Характеристики входных и выходных сигналов

|

1. |

Режим обмена |

ПДП |

|

2. |

Количество входов |

9 |

|

3. |

Количество выходов |

17 |

|

|

Характеристика дискретных входов |

DI2 |

|

1. |

Входной сигнал |

От 4 до 20 мА |

|

2. |

Частота сканирования |

40 кГц |

|

4. |

Напряжение изоляции |

1000 В |

|

|

Характеристика дискретных выходов |

DО1 |

|

1. |

Выходной сигнал |

ОК 5 – 40 В |

|

2. |

Полоса пропускания |

10 кГц |

|

3. |

Нагрузочная способность |

200 мА |

|

4. |

Напряжение изоляции |

500 В |

Где ОК – открытый коллектор

Общее количество каналов - 26, при вводе/выводе большого количества каналов используют БИС 8-разрядного микроконтроллера или БИС параллельного программируемого интерфейса. Использование последовательного интерфейса не имеет смысла, т.к. не обеспечит должной скорости передачи, но зато сэкономит затраты на аналоговых схемах сопряжения с датчиками и исполнительными механизмами. Для обеспечения ПДП передачи с режимом одновременного вводы и вывода необходимо использование двух каналов контроллера ПДП. Характеристики входного сигнала потребуют обеспечения гальванической развязки и защиты от перегрузок по току, выходной сигнал требует, кроме вышеперечисленных компонентов, еще и усилитель для обеспечения высокой нагрузочной способности.

4.2 Анализ режима обмена с модулем

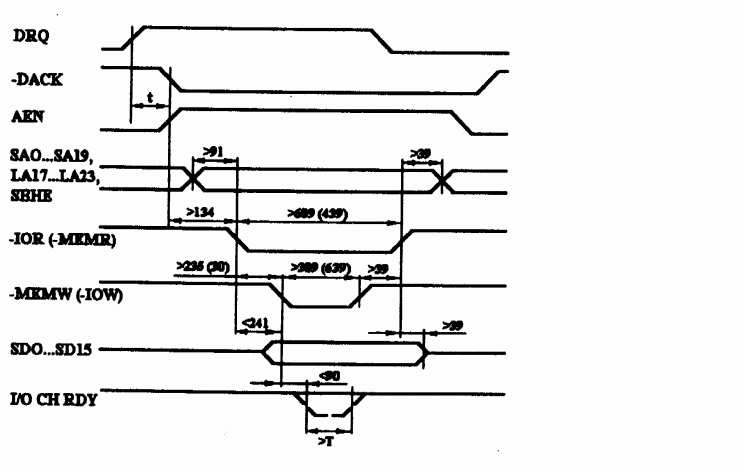

Режим обмена с устройством - прямой доступ к памяти. Временная диаграмма для этого случая показана на рис. 4.1.

Цикл

ПДП начинается с запроса ПДП от исполнителя

(УВВ), желающего произвести обмен, с

помощью одного из сигналов DRQ.

После освобождения системной шины

текущим

задатчиком

контроллер ПДП  формирует

соответствующий сигнал -DACK,

говорящий о предоставлении ПДП

запросившему его устройству. Затем

контроллер ПДП вырабатывает адрес

ячейки памяти, с которой будет производиться

обмен в текущем цикле, и сигнал AEN,

который говорит УВВ о том, что к нему

идет обращение в режиме ПДП. После

этого выставляется строб чтения ( -IOR

или -MEMR), в ответ на который источник

передаваемых данных выставляет свою

информацию на шину данных, и строб записи

(-MEMW

или -IOW), по которому данные записываются

в приемник данных.

формирует

соответствующий сигнал -DACK,

говорящий о предоставлении ПДП

запросившему его устройству. Затем

контроллер ПДП вырабатывает адрес

ячейки памяти, с которой будет производиться

обмен в текущем цикле, и сигнал AEN,

который говорит УВВ о том, что к нему

идет обращение в режиме ПДП. После

этого выставляется строб чтения ( -IOR

или -MEMR), в ответ на который источник

передаваемых данных выставляет свою

информацию на шину данных, и строб записи

(-MEMW

или -IOW), по которому данные записываются

в приемник данных.

|

|

|

Рисунок 4.1- Временная диаграмма работы шины в режиме ПДП |

4.3 Разработка структурной схемы

За

базовую основу модуля ввода / вывода

выберем 8-разрядный параллельный

программируемый порт ввода / вывода,

который легко подключается к шине PC-104

и обеспечивает обслуживание большого

количества каналов ввода / вывода. Но

существующие микросхемы параллельных

портов имеют не более 3-х 8-разрядных

портов ввода / вывода. Т.е. в схеме

необходимо обеспечить дополнительный

буфер ввода или регистр вывода.

Интерфейсная часть должна содержать

схемы формирования и обработки сигналов

ПДП: DRQ

и DACK

отдельно для  канала

ввода и вывода, которые должны отрабатывать

сигналDRQ

по с разной частотой. Канал ввода - 40кГц,

канал вывода - 20кГц, т.е. в два раза больше,

чем полоса пропускания канала. Интерфейсная

часть схемы также должна обеспечить

раздельное управление микросхемой и

дополнительным буфером. Структурная

схема модуля дискретного ввода / вывода

изображена на рис. 4.2.

канала

ввода и вывода, которые должны отрабатывать

сигналDRQ

по с разной частотой. Канал ввода - 40кГц,

канал вывода - 20кГц, т.е. в два раза больше,

чем полоса пропускания канала. Интерфейсная

часть схемы также должна обеспечить

раздельное управление микросхемой и

дополнительным буфером. Структурная

схема модуля дискретного ввода / вывода

изображена на рис. 4.2.

Рисунок 4.2- Структурная схема модуля

На

рисунке представлены следующие

компоненты: BD

- двунаправленный буфер данных, PPI

- параллельный порт, BDD

- дополнительный буфер для приема (или

отправки сигналов), СФ1 и СФ2 - схемы

формирования запроса ПДП, G

- генератор, УЛ -управляющая логика

(служит для разделения доступа к порту

и дополнительному буферу), ГР -

гальваническая развязка, У - усилитель,

ЗТ - защита от перегрузок по току. Работает

схема следующим образом: при поступлении

на вход СФ1 или СФ2 сигнала от генератора,

СФ формирует сигнал DRQ,

по приходу сигнала  DACK

включается двунаправленный буфер

данных, по этому же сигналу снимается

сигнал DRQ.

Контроллер ПДП выставляет на шину адреса

адрес первой ячейки передаваемых (или

принимаемых) данных. Нас интересует

только 2 младших разряда этого адреса,

т.к. модуль имеет максимум 4 программно

доступных элемента. Используя адрес и

управляющие сигналы шины логическая

схема распознает необходимый

модуль-приемник (или источник) и

активизирует его для передачи. После

обмена, диаграмма которого показана на

рис.5.1., сигнал DACK

снимается и тем самым переводит выходы

буфера данных в трехстабильное состояние.

DACK

включается двунаправленный буфер

данных, по этому же сигналу снимается

сигнал DRQ.

Контроллер ПДП выставляет на шину адреса

адрес первой ячейки передаваемых (или

принимаемых) данных. Нас интересует

только 2 младших разряда этого адреса,

т.к. модуль имеет максимум 4 программно

доступных элемента. Используя адрес и

управляющие сигналы шины логическая

схема распознает необходимый

модуль-приемник (или источник) и

активизирует его для передачи. После

обмена, диаграмма которого показана на

рис.5.1., сигнал DACK

снимается и тем самым переводит выходы

буфера данных в трехстабильное состояние.