- •1 Анализ технического задания

- •2.2 Арифметическо-логическое устройство

- •2.3 Память микроконтроллера

- •2.4 Управление работой микроконтроллера

- •2.5 Организация ввода-вывода информации в микроконтроллере

- •3.2 Постоянное запоминающее устройство

- •4.3 Контроллер прямого доступа к памяти (кпдп)

- •4.4 Программируемый интервальный таймер (пит)

- •5.2 Шинный формирователь к580ва86

Лист

Изм

Лист № докум. Подп.

Дата

ВВЕДЕНИЕ

С развитием технологии цифровых интегральных схем появилась возможность создавать сложные устройства обработки цифровой информации в виде компактных микросхем. Однако увеличение сложности реализуемого алгоритма обработки, как правило, сужает область его применения. Устранить противоречие между сложностью БИС и ее универсальностью удалось за счет программирования выполняемых микросхемой функций.

Широкую популярность микропроцессоры получили благодаря своим высоким функциональным возможностям и эксплуатационным характеристикам, придавшим средствам вычислительной техники и автоматики качественно новые свойства: появились и получили широкое распространение микрокалькуляторы, микроЭВМ, персональные ЭВМ, интеллектуальные роботы. Такие характеристики микропроцессоров как малые габариты, масса, потребляемая мощность позволили применять их в областях, в которых использование традиционных средств вычислительной техники было принципиально невозможным.

В настоящее время промышленностью освоено и серийно выпускается более пятнадцати микропроцессорных комплектов БИС различной, архитектуры. Развитие элементной базы микропроцессоров при этом идет по нескольким, взаимодополняющим направлениям, что обеспечивает возможность гибкой адаптации архитектуры систем управления требованиям конкретных применений и специфике условий их эксплуатации.

Целью данного курсового проекта является разработка микропроцессорной управляющей микроЭВМ, реализующей заданные взаимодействия с объектом управления и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

1 Анализ технического задания

Управляющая микроЭВМ проектируется на базе однокристального МП и включает в себя следующие основные устройства: процессорный модуль, память, состоящую из ОЗУ и ПЗУ, устройства параллельного ввода/вывода для связи с ОУ, блок последовательного канала для связи с ЭВМ верхнего уровня, программируемый системный таймер, контроллер прерываний, контроллер прямого доступа в память, пульт управления.

Все модули системы объединяются интерфейсом. Обмен данными по интерфейсу может осуществляться как в едином адресном пространстве, так и в разделенном с помощью управляющих сигналов обращения к ЗУ и ВУ.

Процессорный модуль включает в себя микропроцессор К1816ВЕ48 и, при необходимости, дополнительные БИС (СИС), обеспечивающие реализацию вспомогательных функций (тактовый генератор, шинные формирователи, регистры – защелки и др.).

Устройство ввода для связи с ОУ должны обеспечить ввод в ПМ значения х1, х2, х3, х4 двоичных датчиков, а также 8 – разрядных двоичных кодов NU1, NU2, NU3, принимаемых с выходов АЦП. Сигнал датчика аварийной ситуации ха воспринимается только подсистемой прерывания.

Устройства вывода на ОУ должны обеспечить выдачу двоичных управляющих воздействий у1, у2, у3 определенной длительности и кода управляющего напряжения Y4 – 8-разрядного двоичного вектора на вход ЦАП. В структуру ОУ входит устройство, принимающее массив данных из ПЗУ (ОЗУ) в режиме прямого доступа в память (ПДП). Запрос на ПДП возникает асинхронно по отношению к процедуре управления.

Пульт управления должен обеспечивать ввод в ПМ значения 8 – разрядной двоичной константы К, ввод двоичного значения сигнала «СТОП», формирование сигнала начальной установки системы, вывод на светодиодную индикацию значений х1, х2, х3, х4, у1, у2, у3, NU1, Y4.

Системный таймер должен обеспечить отсчет временных задержек, реализуемых при работе алгоритма управления.

Блок последовательного обмена предназначен для передачи на микроЭВМ верхнего уровня информации о состоянии процесса управления. По запросу микроЭВМ разрабатываемая управляющая микроЭВМ должна обеспечить выдачу по последовательному каналу кадра. Передача информации с верхнего уровня на нижний не предусмотрена.

Контроллер прерывания обеспечивает фиксацию запросов на прерывание от различных источников и дисциплину обслуживания запросов. В подсистеме векторного прерывания контроллер формирует код команды вызова, а при наличии в системе радиального входа запроса на прерывания – код состояния регистров запросов.

Алгоритм управления определяется функциями:

y1=X1&X2&X3, t1=20мкc,

где Х1, Х2, Х3 – значения двоичных датчиков;

y2=min(NU1, NU2), t2=120мкс, t3=90мкс,

где NU1, NU2 – 8-разрядные двоичные коды;

t1, t2, t3 – длительность управляющих сигналов.

Типы БИС, на которых должен быть реализован блок памяти:

БИС ОЗУ – К134РУ6;

БИС ПЗУ – К556РТ6.

2 РАЗРАБОТКА ПРОЦЕССОРНОГО МОДУЛЯ И ИНТЕРФЕЙСА

2.1 Анализ структуры МП К1816ВЕ48

Однокристальный 8-разрядный микроконтроллер K1816BE48, называемый для краткости МК 1816, представляет собой БИС, имеющую в своем составе все атрибуты небольшой микро-ЭВМ: арифметическо-логическое устройство, устройство управления, постоянное ЗУ программ, ОЗУ данных и интерфейсные схемы. Организация, система команд и средства ввода — вывода информации МК 1816 лучше всего приспособлены для решения задач управления и регулирования в сравнительно несложных объектах, приборах и технологических процессах.

В состав аппаратурных средств МК входят: стираемое перепрограммируемое ПЗУ (СППЗУ) программ емкостью 1 Кбайт; регистровое ОЗУ данных емкостью 64 байта; 8-разрядное арифметическо-логическое устройство; устройство управления; 8-битный программируемый таймер/счетчик событий; программно-управляемые схемы ввода — вывода (27 линий).

Организация МК и его система команд допускают в случае необходимости расширение функционально-логических возможностей контроллера. С использованием внешних дополнительных БИС адресное пространство ППЗУ программ может быть расширено до 4 Кбайт. Кроме того, архитектура МК обеспечивает возможность прямой адресации внешнего ОЗУ емкостью 256 байт. С использованием более сложных программно-реализуемых способов адресации емкость внешнего ОЗУ может быть увеличена до требуемого объема страницами по 256 байт в каждой. И, наконец, путем подключения интерфейсных БИС КР580ВВ55 число линий связи МК с объектом управления может быть увеличено практически без ограничений.

В МК 1816 реализована система векторного прерывания от двух источников: внутреннего таймера/счетчика событий и внешнего источника. Внутренний 8-уровневый стек обеспечивает автоматическое сохранение и восстановление основных параметров вычислительного процесса при запросах прерывания и при возврате после обслуживания прерывания.

Три 8-битных порта ввода — вывода информации, два входа тестирующих сигналов и один вход запроса прерывания обеспечивают связь МП с объектом управления по 27 линиям. Кроме того, имеются выводы для подключения осциллятора и для передачи таких сигналов, как начальная установка, строб адреса внешней памяти, чтение, запись. Вывод, через который МК в процессе работы выдает сигнал стробирования УВВ, на этапе заполнения СНИЗУ программ используется для подачи программирующего сигнала. Выводы, через которые подаются сигналы пошаговой работы и режима внешнего доступа, используются на этапе отладки МК при тестировании прикладной программы.

Основные параметры:

Источник питания, В 5±10%

Рассеиваемая мощность, Вт 1,5

Диапазон рабочих температур, °С от 0 до +70

Частота синхронизации, МГц от 1 до 6

Цикл однобайтной команды, мкс 2,5

двухбайтной команды, мкс 5

Емкость СППЗУ, Кбайт

Емкость ОЗУ, байт 64

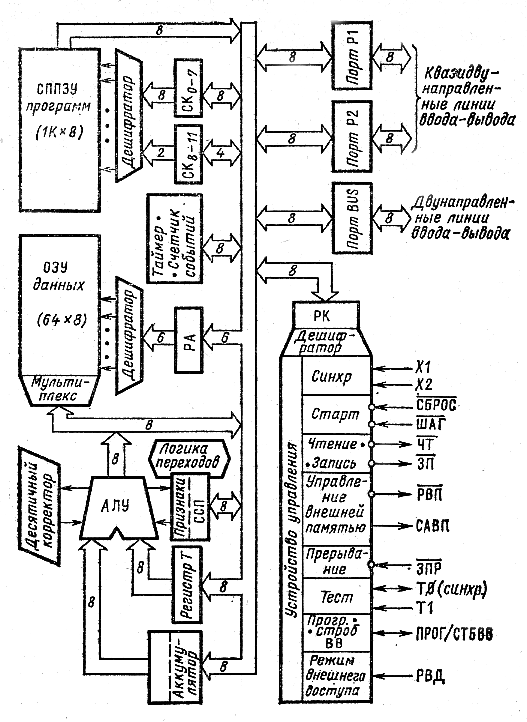

На рисунке 1 показана структура МК 1816. Основу структуры МК образует внутренняя двунаправленная разделяемая 8-битная шина, которая связывает между собой все устройства БИС: арифметическо-логическое устройство, устройство управления, память и порты ввода—вывода информации.

Рассмотрим последовательно основные элементы структуры и особенности организации МК.

Микроконтроллер 1816 конструктивно выполнен в корпусе БИС с 40 внешними выводами. Все выводы электрически совместимы с элементами ТТЛ, входы представляют собой единичную нагрузку, а выходы могут быть нагружены одной ТТЛ-нагрузкой. Ниже приводятся символические имена выводов (сигналов), в скобках указываются номера выводов корпуса и дается краткое пояснение назначения вывода.

Рисунок 1 – Структура микроконтроллера К1816

ЗЕМЛЯ (20)—потенциал земли.

Uосн (40)—основное напряжение питания +5В подается во время работы и при программировании СНИЗУ.

Uдоп (26)—дополнительное напряжение питания +5В во время работы МК обеспечивает электропитание только для СППЗУ; на этот вывод при программировании СППЗУ подается уровень +25 В.

ПРОГ/СТБВВ (25) —вход для подачи программирующего импульса +25В при загрузке СППЗУ; выход стробирующего сигнала УВВ во время работы.

XI (2) —вход для подключения вывода кварцевого осциллятора или вход для сигнала от внешнего источника синхронизации.

Х2 (3) — вход для подключения второго вывода осциллятора.

СБРОС (4) — вход сигнала общего сброса при запуске МК; сигнал 0 при программировании и проверке СППЗУ.

ШАГ (5)—сигнал, который совместно с сигналом САВП позволяет выполнять программу с остановом после исполнения очередной команды; используется на этапе отладки.

РВП (9) — разрешение внешней памяти; сигнал подается на вход разрешения буфера внешней памяти только тогда, когда происходит обращение к внешней памяти программ.

САВП (11)—строб адреса внешней памяти; сигнал используется для приема и фиксации адреса внешней памяти на внешнем регистре, сигнал является идентификатором машинного цикла, так как всегда выводится из МК с частотой, в 5 раз меньшей основной частоты синхронизации.

ЧТ (8) —стробирующий сигнал при чтении из внешней памяти или УВВ.

ЗП (10)—стробирующий сигнал при записи во внешнюю память данных или УВВ.

Т0 (1) —входной сигнал, опрашиваемый по командам условного перехода JTO и JNT0; используется при программировании СППЗУ; может быть использован для вывода сигнала синхронизации по команде ENTO CLK.

Т1 (39)—входной сигнал, опрашиваемый командами условного перехода JT1 и JNT1; кроме того, используется в качестве входа внутреннего счетчика внешних событий после исполнения команды STRT CNT.

ЗПР (6)—сигнал запроса прерывания от внешнего источника; вызывает подпрограмму обслуживания прерывания, если прерывание разрешено ранее по команде ENI; сигнал СБРОС запрещает прерывания.

РВД (7)—режим внешнего доступа; уровень 1 на этом входе заставляет МК выполнять выборку команд только из внешней памяти программ; используется при тестировании прикладной программы и отладке МК.

Порт Р10-7 (27 - 34) — 8-разрядный квазидвунаправленный порт ввода — вывода информации; каждый разряд порта может быть запрограммирован на ввод или на вывод.

ПортР20-7(21 - 24, 35 - 38) - 8-разрядный квазидвунаправленный порт ввода — вывода информации; каждый разряд порта может быть запрограммирован на ввод или вывод; биты Р2о-з во время чтения из внешней памяти программ содержат старшие четыре разряда счетчика команд СКв-п, во время ввода — вывода используются для схемы расширения ввода — вывода и адресуют внешние порты Р4—Р7.

Порт BUS0-7(12—19) — 8-разрядный двунаправленный порт ввода — вывода информации; может быть отключен от нагрузки; может выполнять прием и выдачу байтов синхронно с сигналами ЧТ и ЗП; при обращений к внешнему ППЗУ программ содержит 8 младших разрядов счетчика команд и затем по сигналу РВП принимает выбранную команду; при обращении к внешнему ОЗУ данных содержит младшие 8 разрядов адреса синхронно с сигналом САВП и байт данных синхронно с сигналами ЧТ или 3TL.