- •2.2 Архитектура и режимы работы мп к580вм80

- •3 Разработка подсистемы памяти

- •3.1 Оперативно запоминающее устройство к134ру6

- •4.1 Архитектура программируемого таймера кр580ви53

- •4.2 Архитектура бис параллельного интерфейса кр580вв55

- •4.5 Архитектура контроллера прямого доступа к памяти кр580вт57

- •5 Разработка алгоритма работы микропроцессорной системы

СОДЕРЖАНИЕ

Введение 4

1 Расшифровка и анализ технического задания 5

1.1 Сравнительный анализ восьмиразрядных микропроцессоров 8

2 Разработка процессорного модуля, интерфейса и упрощенной

структурной схемы 9

2.1 Основные параметры микросхемы К580ВМ80 9

2.2 Архитектура и режимы работы МП К580ВМ80 9

2.3 Архитектура вспомогательных интерфейсных микросхем

комплекта К580 13

2.4 Упрощенная структурная схема управляющей микро-ЭВМ 20

3 Разработка подсистемы памяти 23

3.1 Оперативно запоминающее устройство К134РУ6 23

3.2 Постоянно запоминающее устройство К541РТ2 25

3.3 Подключение памяти к системной шине 27

4 Разработка подсистем ввода/вывода, прерываний, прямого доступа

к памяти. Выбор таймера 29

4.1 Архитектура программируемого таймера КР580ВИ53 29

4.2 Архитектура БИС параллельного интерфейса КР580ВВ55 41

4.3 Архитектура БИС программируемого контроллера

прерываний КР580ВН59 34

4.4 Подбор подсистемы ввода/вывода. Архитектура БИС

программируемого контроллера клавиатуры и индикации

КР580ВВ79 37

4.5 Аналого-цифровой преобразователь К572ПВ3 42

4.6 Архитектура контроллера прямого доступа к памяти КР580ВТ57 43

4.7 Уточненная схема МПС на основе МП К580ВМ80 46

5 Разработка алгоритма работы микропроцессорной системы 49

6 Реализация микропроцессорной системы управления на базе МП

К580ВМ80 52

Заключение 57

Список использованных источников 58

Приложение А 59

ВВЕДЕНИЕ

В настоящее время практически невозможно указать какую-то отрасль науки и производства, в которой бы не использовались микропроцессоры (МП) и микро ЭВМ. Применение МП привело к замене физического схемного метода реализации заданных функций математическим программным методом, представляющим большие возможности, причем обеспечивается независимость характеристик от физических условий применения. Важным свойством микропроцессорной техники является её высокая гибкость, возможность быстрой перенастройки при изменении алгоритмов управления, перенастройка осуществляется программным способом. Микропроцессорная техника позволяет реализовать системы, функциональные возможности которых могут наращиваться по мере необходимости или по мере появления новых технических средств, тем самым обеспечивается соответствие технического уровня микропроцессорных систем управления самым современным требованиям в течение длительного времени.

Микропроцессорные средства позволяют создавать разнообразные по сложности выполняемых функций устройства управления – от простейших микроконтроллеров несложных приборов и механизмов до сложнейших специализированных и универсальных систем распределенного управления в реальном времени. Благодаря различию комплектаций, производительности и объема оборудования модулей они создают аппаратурную основу для разработки систем, ориентированных на различные области применения, и инструментальных комплексов для отладки их программ.

Целью курсового проекта является разработка управляющей микро-ЭВМ, реализующей заданный алгоритм управления (ОУ).

1 РАСШИФРОВКА И АНАЛИЗ ЗАДАНИЯ

Задание на курсовой проект включает в себя набор исходных данных и ограничений для проектирования управляющей микроЭВМ.

Задание определяет:

- базовый микропроцессор К580ВМ80, на основе которого требуется построить управляющую микроЭВМ.

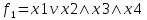

- алгоритм управления определяется в задании видом функций f1 и f2, длительностями управляющих сигналов t1, t2, t3; необходимо при срабатывании аварийного датчика (INT1) сформировать на пульте аварийную сигнализацию светодиодом (2Гц).

- типы БИС, на которых должны быть реализованы блоки ПЗУ и ОЗУ: К134РУ6, К541РТ2.

Управляющая микроЭВМ проектируется на базе однокристального МП и включает в себя следующие основные устройства:

- процессорный модуль;

- память, состоящую из ОЗУ и ПЗУ;

- устройства параллельного ввода/вывода для связи с ОУ;

- блок последовательного канала для связи с ЭВМ верхнего уровня;

- программируемый системный таймер;

- контроллер прерываний;

- контроллер прямого доступа к памяти;

- пульт управления.

Алгоритм управления состоит из следующих этапов:

- обработка информации от цифровых датчиков и выдача управляющего воздействия производится путем ввода значений х1, х2, х3 и вычисления значения булевой функции f1(х1, х2, х3) (при единичном значении f1 вырабатывается управляющий сигнал =1 длительностью t1);

- при обработке информации с аналоговых датчиков процессорный модуль принимает 8-разрядные двоичные коды NU1, NU2 с выводов АЦП и код константы К с регистра пульта управления; далее вычисляется значение функции NU=f2(NU1,NU2,K) и сравнивается с константой Q; в зависимости от результатов сравнения вырабатывается один из двух двоичных управляющих сигналов y2 или y3 длительностью t2 или t3 соответственно (если NU<Q, то выдается y2, иначе выдается y3);

- формируется управляющее воздействие Y4, для чего с АЦП вводится значение NU3, производится вычисление по формуле:

- значение Y4 в виде 8-разрядного кода выдается на вход ЦАП.

В системе необходимо предусмотреть следующие линии запроса на внешние прерывания:

INT0 – отказ источника питания;

INT1 – сигнал ха аварийного датчика ОУ;

INT2 – запрос от пульта управления;

INT3 – запрос от микроЭВМ верхнего уровня.

Программное обеспечение системы разрабатывается на языке Ассемблер соответствующего микропроцессора и включает следующие основные модули:

- модуль начальной инициализации системы;

- модуль управления;

- программы обслуживания прерываний, в том числе драйвер последовательного канала.

Представлена таблица истинности для заданной функции f1.

Таблица 1- Таблица истинности

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

0 |

1 |

0 |

|

0 |

0 |

1 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

0 |

|

0 |

1 |

1 |

1 |

1 |

|

1 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

1 |

1 |

1 |

|

1 |

1 |

0 |

0 |

0 |

|

1 |

1 |

0 |

1 |

0 |

|

1 |

1 |

1 |

0 |

0 |

|

1 |

1 |

1 |

1 |

1 |

При анализе таблицы истинности можно сказать, что управляющий сигнал f1 = 1 формируется в нескольких случаях единичного сигнала на входах датчиков. Сигнал формируется при подаче единичного сигнала на вход Х2, Х3, Х4, а также при единовременной подаче единичного сигнала на входы Х1, Х3, Х4; Х1,Х2, Х3, Х4.

1.1 Сравнение МП Z-80, К580ВМ80, Intel 8080

При построении управляющей микроЭВМ в качестве ЦП по техническому заданию используется К580ВМ80. Проведем сравнительный анализ среди 8-ми разрядных МП. Сравнительные характеристики данных МП в таблице 2.

Таблица 2 – Характеристики МП Z-80, К580ВМ80, Intel 8080

|

Параметр |

Z-80 |

К580ВМ80 |

Intel 8080 |

|

1 |

2 |

3 |

4 |

|

Тактовая частота, МГц |

2,5 |

2 |

2 |

|

Разрядность регистров, бит |

8 |

8 |

8 |

|

Разрядность ШД, бит |

8 |

8 |

8 |

|

Разрядность ША, бит |

16 |

16 |

16 |

|

Объём адресуемой памяти, Кбайт |

64 |

64 |

64 |

Данные восьмиразрядные МП различаются лишь по тактовой частоте, а по всем остальным параметрам схожи. В данной работе нет необходимости использовать МП большей тактовой частоты, поэтому К580ВМ80 удовлетворяет требованиям курсового проекта.

2 РАЗРАБОТКА ПРОЦЕССОРНОГО МОДУЛЯ, ИНТЕРФЕЙСА И

УПРОЩЕННОЙ СТРУКТУРНОЙ СХЕМЫ

2.1 Основные параметры микроЭВМ К580ВМ80

Микросхема К580ВМ80 – функционально законченный однокристальный параллельный 8-разрядный микропроцессор с фиксированной системой команд, - применяется в качестве центрального процессора в устройствах обработки данных и управления. Микропроцессор имеет раздельные 16-разрядный канал адреса и 8-разрядный канал данных.

Канал адреса обеспечивает прямую адресацию внешней памяти объемом до 65536 байт, 256 устройств ввода и 256 устройств вывода. Рассматриваемая БИС является однокристальным МП, выполненным на основе n-МОП-технологии. Предназначена для построения вычислительных устройств, контроллеров, микроЭВМ. Разрядность МП – 8 бит, тактовая частота 2 МГц, время выполнения команды 2-9 мкс, напряжения питания +12,+5 и – 5 В, потребляемая мощность 0,75 Вт.

Базовая архитектура содержит 8-разряднцй центральный процессор, программируемое ПЗУ, статическое ОЗУ.

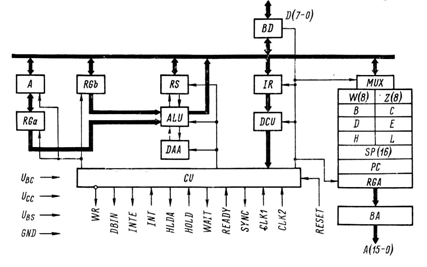

2.2 Архитектура и режимы работы мп к580вм80

Структурная схема МП представлена на рисунке 1. В состав БИС входят арифметико-логическое устройство (ALU); регистр признаков (RS),фиксирующий признаки, вырабатываемые ALU в процессе выполнения команд; аккумулятор (А); регистр аккумулятора (RGa); регистр временного хранения операндов (RGb); десятичный корректор (DAA), выполняющий перевод информации из двоичной в двоично-десятичную форму; регистр команд (IR), предназначенный для хранения первого байта команды, содержащего код операции; дешифратор команд (DCU); блок регистров для приема, выдачи и хранения информации в процессе выполнения программ, содержащий программный счетчик (PC), указатель стека (SP), регистр адреса (RGA), шесть регистров общего назначения (B, C, D, E, H, L) и вспомогательные регистры (W и Z); схема управления и синхронизации (CU), формирующая последовательности управляющих сигналов для работы ALU и блока регистров; 16-разрядный буферный регистр адреса (BA); 8-разрядный буферный регистр данных (BD), двунаправленный мультиплексор (MUX) для обмена операндами и результатами операций между ALU и блоком регистров по внутренней шине данных.

Рисунок 1 – Структура МП К580ВМ80

Цоколевка данного МП приведена на рисунке 2.

Рисунок 2 – Цоколевка МП К580ВМ80

В таблице 3 приведем описание выводов микросхемы.

Таблица 3 – Описание выводов микросхемы

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сост-ние |

||||

|

Англ. |

Рус. |

|||||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|||

|

25; 26; 27; 29; 30; 31; 32; 33; 34; 35; 1; 40; 37; 38; 39; 36 |

A(15-0) |

А(15-0) |

Трехстабильная 16-разрядная шина адреса |

выход |

0, 1, z |

|||

|

10; 9; 8; 7; 3; 4; 5; 6 |

D(7-0) |

Д(7-0) |

Двунаправленная трехстабильная 8-разрядная шина данных |

вход |

0, 1, z |

|||

|

18 |

WR (TR) |

ЗП |

Выход сигнала «выдача» - напряжение L-уровня указывает на выдачу байта информации на шину D(7-0) для записи в ЗУ или УВВ |

выход |

0 |

|||

|

17 |

DBIN (RC) |

П |

Выход сигнала «прием» - напряжение H-уровня указывает на прием с шины D(7-0) байта информации, выданного ЗУ или УВВ |

выход |

1 |

|||

Продолжение таблицы 3

|

1 |

2 |

3 |

4 |

5 |

6 |

|

16 |

INTE |

Р. ПР |

Выход сигнала «разрешение прерывания» |

выход |

1 |

|

14 |

INT |

З. ПР |

Вход сигнала «запрос на прерывание» |

вход |

1 |

|

21 |

HLDA |

П. ЗХ |

Выход сигнала «подтверждение захвата» - напряжение H-уровня указывает на перевод шин адреса и данных МП в высокоимпедансное состояние |

выход |

|

|

13 |

HOLD (HLD) |

ЗХ |

Вход сигнала «захват» - напряжение H-уровня указывает на запрос другими устройствами системы на управления шинами системы |

вход |

1 |

|

24 |

WAIT (WI) |

ОЖД |

Выход сигнала «ожидание» - напряжение H-уровня указывает на состояние ожидания МП |

выход |

1 |

|

23 |

READY (RDY) |

Г |

Вход сигнала «готовность» - напряжение Н-уровня указывает на готовность данных на шине D(7-0) к вводу в МП или на готовность внешних устройств к приему информации, служит для синхронизации МП с ЗУ или УВВ |

вход |

1 |

|

19 |

SYNC (SYN) |

СИНХР |

Выход сигнала «синхро» - напряжение Н-уровня идентифицирует начало каждого машинного цикла |

выход |

1 |

|

22 |

CLK1 (C1) |

Ф1 |

Вход фазы 1 |

вход |

1 |

|

15 |

CLK2 (C2) |

Ф2 |

Вход фазы 2 |

вход |

1 |

|

12 |

RESET (SR) |

СБР |

Вход установки 0 – установка счетчика команд в нуль, сброс триггеров разрешения прерывания и захвата шин |

вход |

1 |

|

28 |

UCC2 |

Uпит2 |

Напряжение питания (+12 В) |

вход |

- |

|

20 |

UCC1 |

Uпит1 |

Напряжение питания (+5 В) |

вход |

- |

|

11 |

UI0 |

Uпит |

Напряжение питания (-5 В) |

вход |

- |

|

2 |

GND |

ОБЩ |

Напряжение питания (0 В) |

выход |

- |

2.3 Архитектура вспомогательных интерфейсных микросхем комплекта К580

Для сопряжения ЦП К580ВМ80 необходимо использовать схемы системного контроллера и шинного формирователя, генератор тактовых импульсов.

2.3.1 Генератор тактовых импульсов КР580ГФ24. Генератор тактовых импульсов КР580ГФ24 предназначен для синхронизации микропроцессорных систем на основе комплекта К580. Генератор тактовых импульсов (ГТИ) формирует тактовые импульсы частотой до 2,5 МГц, амплитудой 12 В, тактовые импульсы амплитудой до 5 В для ТТЛ-схем, а также некоторые управляющие сигналы для микропроцессорной системы.

Структурная схема ГТИ представлена на рисунке 3, а, подключение ГТИ к МП показано на рисунке 3, б. ГТИ состоит из задающего генератора (SGN), генератора тактовых импульсов (GLG), порогового элемента, формирователей и логических схем. Для работы ГТИ необходимо подключение внешнего кварцевого резонатора с частотой колебаний в 9 раз большей, чем частота выходных тактовых импульсов ГТИ.

Рисунок 3 – а) Структурная схема ГТИ; б) подключение ГТИ к МП

Цоколевка ГТИ представлена на рисунке 4.

Рисунок 4 – Цоколевка ГТИ

Назначение входных и выходных сигналов ГТИ указано при описании выводов микросхемы в таблице 4.

Таблица 4 – Описание выводов ГТИ

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

15; 14 |

XTAL1 (CR1), XTAL2 (CR2) |

КВ. РЕЗ. |

Входы для подключения кварцевого резонатора |

вход |

1 |

|

13 |

TANK |

ППК |

Вход для подключения параллельного LC-контура |

вход |

1 |

|

5 |

SYNC |

СИНХ |

Вход синхронизации |

вход |

1 |

|

2 |

RESIN |

ВХ. СБР |

Входной сигнал «СБРОС» |

вход |

0 |

|

3 |

RDYIN |

ВХ. Г |

Вход сигнала «ГОТОВ» для подачи сигналов о готовности внешних устройств к работе с МП |

вход |

1 |

|

12 |

OSC |

ВЫХ. ТАКТ |

Выход генератора, используемый для тактирования периферийных устройств |

выход |

1 |

|

11; 10 |

CLK1, CLK2 |

ВЫХ. ТИ |

Выходы тактовых импульсов |

выход |

1 |

|

6 |

CLK2 (TTL) |

ВЫХ. ТИ (ТТЛ) |

Выход тактовых импульсов для ТТЛ-схем |

выход |

1 |

|

7 |

STSTB |

СТРС |

Строб состояния – сигнал L-уровня, используемый для фиксации слова-состояния МП |

выход |

0 |

|

1 |

RESET |

ВЫХ. СБР |

Выходной сигнал «СБРОС» |

выход |

1 |

|

4 |

READY |

ВЫХ. Г |

Выходной сигнал «ГОТОВ» |

выход |

1 |

|

16 |

UCC |

Uпит |

Напряжение питания (+5 В) |

вход |

|

Продолжение таблицы 4

|

1 |

2 |

3 |

4 |

5 |

6 |

|

9 |

UDD |

UDD |

Напряжение питания (+12 В) |

вход |

- |

|

8 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход |

- |

2.3.2 Системный контроллер и шинный формирователь КР580ВК28. Системный контроллер и шинный формирователь КР580ВК28 предназначен для фиксации слова-состояния МП, выработки системных управляющих сигналов, буферизации шины данных МП и управления направлением передачи данных.

Структурная схема системного контроллера и шинного формирователя (СКФ) приведена на рисунке 5, а, подключение СКФ к МП – на рисунке 5, б. В состав СКФ входят: шинный формирователь-усилитель (BF), обеспечивающий увеличение нагрузочной способности системной информационной шины; регистр (RG) для записи и хранения слова-состояния МП; комбинационная схема (PLA) для формирования выходных управляющих сигналов.

Рисунок 5 – а) Структурная схема СКФ; б) подключение СКФ к МП

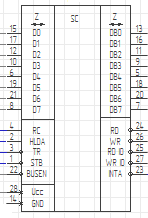

Цоколевка СКФ представлена на рисунке 6.

Рисунок 6 – Цоколевка СКФ

Назначения входных, выходных и управляющих сигналов СКФ приведены в таблице 5.

Таблица 5 – Описание выводов СКФ

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

8; 21; 19; 6; 10; 12; 17; 15 |

D(7-0) |

Д(7-0) |

Входы/выходы данных (со стороны МП) |

вход/ выход |

0, 1, z |

|

1 |

STSTB |

СТРС |

Строб состояния (от ГТИ) |

вход |

0 |

|

4 |

DBIN |

ВХ. ПР |

Вход сигнала «ПРИЕМ» от МП |

вход |

1 |

|

3 |

WR |

ВХ. ВЫД |

Вход сигнала «ВЫДАЧА» от МП |

вход |

0 |

|

2 |

HLDA |

ВХ.П. ЗХ |

Вход сигнала «ПОДТВЕРЖДЕНИЕ ЗАХВАТА» от МП |

вход |

1 |

|

7; 20; 18; 5; 9; 11; 16; 13 |

DB(7—0) |

Д(7-0) |

Входы/выходы информационной системной шины |

вход/ выход |

0, 1, z |

|

24 |

MEMR |

ЧТ. ПАМ |

Чтение памяти |

выход |

0 |

|

26 |

MEMW |

ЗП. ПАМ |

Запись в память |

выход |

0 |

|

25 |

I/OR |

ЧТ. ВУ |

Чтение с ВУ |

выход |

0 |

|

27 |

I/OW |

ЗП ВУ |

Запись в ВУ |

вход |

0 |

|

22 |

BUSEN |

РАЗ. Р Ш |

Разрешение работы шин – сигнал Н-уровня, устанавливающий все выходы в высокоимпедансное состояние |

вход |

0 |

|

23 |

INTA |

ПОД. ПР |

Подтверждение прерывания - сигнал L-уровня, используемый для стробирования ввода адреса подпрограммы обслуживания прерывания |

выход |

0 |

|

28 |

UCC |

Uпит |

Напряжение питания (+5 В) |

вход |

1 |

|

14 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход |

1 |

По сигналу STSTB, который вырабатывается ГТИ, происходит запись слова-состояния в регистр хранения, а затем выдача его на комбинационную схему, формирующую управляющие сигналы.

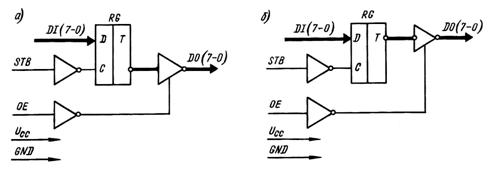

Запись входных данных в буферный регистр производится при переходе сигнала STB с Н-уровня в L-уровень. При Н- уровне сигнал ОЕ выходы буферных регистров находятся в высокоимпедансном состоянии.

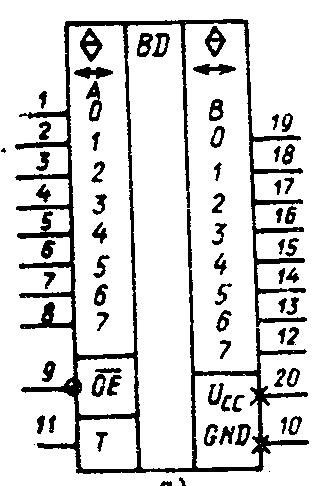

2.3.3 Буферный регистр КР580ИР82. Буферный регистр КР580ИР82 представляет собой 8-разрядный параллельный регистр с тристабильным выходом. Они используются для реализации схем фиксации, буферизации и мультиплексирования в МПС. На выходах микросхемы КР580ИР82 генерируются неинвертированные входные данные.

Структурная схема буферного регистра модели 82 приведена на рисунке 7.

Рисунок 7 – Структурная схема буферного регистра КР580ИР82

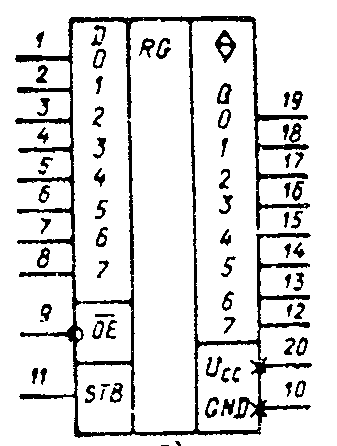

Цоколевка буферного регистра представлена на рисунке 8.

Рисунок 8 - Цоколевка буферного регистра КР580ИР82

Назначение входных и выходных сигналов указано в таблице 6.

Таблица 6 – Описание выводов буферных регистров КР580ИР82

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

8; 7; 6; 5; 4; 3; 2; 1 |

D (7-0) |

Д(7-0) |

Входы данных |

вход |

0, 1, z |

|

11 |

STB |

СТРОБ |

Вход сигнала стробирования |

вход |

1 |

|

9 |

OE |

РАЗ. В |

Вход сигнала разрешения ввода |

вход |

0 |

|

12; 13; 14; 15; 16; 17; 18; 19 |

B (7-0) |

Б(7-0) |

Выходы данных |

вход |

0, 1, z |

|

20 |

UCC |

Uпит |

Напряжение питания (+5 В) |

вход |

- |

|

10 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход/ выход |

- |

Запись входных данных в буферный регистр производится при переходе сигнала STB с Н-уровня в L-уровень. При Н- уровне сигнал ОЕ выходы буферных регистров находятся в высокоимпедансном состоянии.

2.3.4 Шинный формирователь КР580ВА86. Шинный формирователь КР580ВА86 представляет 8-разрядный параллельный приемопередатчик с тристабильным выходом. Он используются для реализации различных буферных схем в МПС. На выходах микросхемы КР580ВА86 генерируются неинвертированные выходные данные.

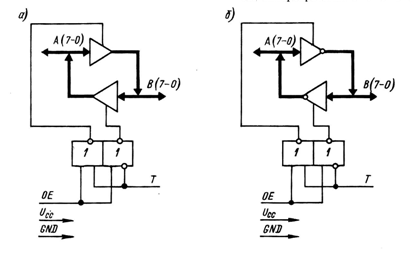

Структурная схема шинного формирователя модели 86 представлена на рисунке 9.

Рисунок 9 – Структурная схема КР580ВА86

Цоколевка шинного формирователя модели КР580ВА86 представлена на рисунке 10.

Рисунок 10 – Цоколевка шинного формирователя КР580ВА86

Назначение входных и выходных сигналов указано в таблице 7.

Таблица 7 – Описание выводов шинного формирователя КР580ВА86

|

Номера выводов |

Обозначение |

Назначение выводов |

Тип сигн. |

Сос-тояние |

|

|

Англ. |

Рус. |

||||

|

1 |

2 |

3 |

4 |

5 |

6 |

|

8; 7; 6; 5; 4; 3; 2; 1 |

А(7-0) |

А(7-0) |

Выводы данных для локальной шины МП |

вход/ выход |

0, 1, z |

|

12; 13; 14; 15; 16; 17; 18; 19 |

В(7-0) |

Д(7-0) |

Выводы данных для системной шины |

вход/ выход |

0, 1, z |

|

11 |

Т |

Т |

Вход управления направлением передачи |

вход |

1 |

|

9 |

ОЕ |

ОЕ |

Вход разрешения передачи |

вход |

0 |

|

20 |

UCC |

Uпит |

Напряжение питания (+5 В) |

вход |

- |

|

10 |

GND |

ОБЩ |

Напряжение питания (0 В) |

вход |

- |

При Н-уровня сигнала на входе Т и L-уровне с выводов А(7-0) передается на вывод В(7-0). При L-уровне сигнала на входе и L-уровне сигнала на входе ОЕ информация с выводов В(7-0) передается на выводы А(7-0). При Н-уровне сигнала на входе ОЕ шинные формирователи переходят в высокоимпедансное состояние.

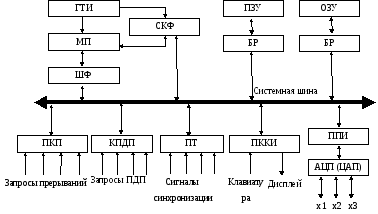

2.7 Упрощенная структурная схема микро-ЭВМ

На рисунке 11 представлена упрощенная структурная схема управляющей микро-ЭВМ. В состав микро-ЭВМ входят: микропроцессор, память, включающая ОЗУ и ПЗУ, которая служит для хранения данных и программ, устройств ввода/вывода, служащих для связи микроЭВМ с внешними устройствами, система прерываний, таймер.

Системная шина – канал, предназначенный для объединения всех блоков микро-ЭВМ и обеспечения обмена данными в виде двоичных чисел.

Устройства ввода/вывода (клавиатура и дисплей) подключаются к системной шине через интерфейсы ввода/вывода (программируемый контроллер клавиатуры и индикации).

ГТИ – генератор тактовых импульсов; ПЗУ – постоянно запоминающее устройство; ОЗУ – оперативно запоминающее устройство; СКФ – системный контроллер и шинный формирователь; МП – микропроцессор; БР – буферный регистр; ШФ – шинный формирователь; ПКП – программируемый контроллер прерываний; ПТ – программируемый таймер; КПДП – контролер прямого доступа к памяти; ПККИ – программируемый контроллер клавиатуры и индикации; ППИ – программируемый параллельный интерфейс; АЦП (ЦАП) – аналого-цифровой преобразователь (цифро-аналоговый преобразователь).

Рисунок 11 - Упрощенная структурная схема микро-ЭВМ

ПЗУ и ОЗУ образуют систему памяти, предназначенную для хранения программ управления, констант. Для подключения памяти к системной шине используются буферные регистры. ОЗУ используется для хранения данных, поступивших из внешнего устройства или подготовленных для выдачи во внешнее устройство, а также для хранения промежуточных результатов вычислений и адресной информации.

Микропроцессор осуществляет обработку данных и управляет всеми модулями системы. Для синхронизации микропроцессора с системной шиной используются системный контроллер и шинные формирователи. Блок генератора тактовых импульсов предназначен для выработки серии тактовых импульсов и некоторых вспомогательных сигналов, а также для синхронизации других блоков микро-ЭВМ.

Программируемый контроллер прерываний предназначен для обслуживания прерываний: упрощения работы процессора с внешними запросами прерываний. Данный контроллер программно управляется процессором по системной шине, в обмене информацией не участвует.