курсовой проект / НА БАЗЕ МИКРОПРОЦЕССОРА К1810ВМ86 / Введение

.docВведение

Развитие микроэлектронной технологии, обеспечившее появление больших и сверхбольших интегральных схем (СБИС), создало предпосылки для резкого снижения стоимости систем управления (СУ). Но практическая реализация достижения технологии БИС и СБИС стало возможным после создания МП. МП – универсальный компонент, который стал связующим звеном для нового поколения изделий микроэлектроники, и обеспечил их функциональную полноту.

Существенным отличие МП од других элементов радиоэлектроники является замена физического, схемного метода реализации заданных функций, математическим программным методом.

Этот метод предоставляет проектировщику большие возможности, т.е. снимает ряд физических ограничений при реализации различных функций, обеспечивает независимость характеристик от физических условий применения. Важным свойством МП является высокая гибкость, возможность быстрой перенастройки при необходимости даже значительных изменение в алгоритмах управления.

Целью курсового проектирования по дисциплине «Микропроцессорные устройства систем управления» является обобщение, закрепление и углубление знаний по дисциплинам: «Электроника и микросхемотехника», «Вычислительные машины и системы», «Микропроцессорные устройства систем управления», формирование навыков разработки и оформления текстовой и графической документации; развитие навыков устных сообщений по содержанию курсового проекта. Содержанием курсового проекта является разработка микропроцессорной управляющей микроЭВМ, реализующей заданные взаимодействия с объектом управления (ОУ) и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

-

Расшифровка и анализ задания

Задание на курсовой проект включают в себя набор исходных данных и ограничений для проектирования управляющей микроЭВМ. Задание определяет:

- базовый микропроцессор (микроЭВМ), на основе которого требуется построить управляющую микроЭВМ.

- типы БИС, на которых должны быть реализованы блоки ПЗУ и ОЗУ

- алгоритм управления определяется в задании видом функции f1, f2, t1, t2, t3. Необходимо при срабатывании аварийного датчика (INT1) сформировать на пульте аварийную сигнализацию светодиодом (2 Гц)

Вариант № 11.

БИС МП (микроЭВМ) К1810ВМ86

БИС ОЗУ К565РУ6

БИС ПЗУ К541РЕ1

Функция y1=f(x1, x2, x3, x4) x1&x2&x3 x4

Функция NU=f(NU1,NU2,K) NU1 - NU2 – K

Время t1 80мкс

Время t2 75мкс

Время t3 75мкс

-

Разработка процессорного модуля, интерфейса и уточненной структурной схемы

-

Архитектура и режимы работы микропроцессора К1810ВМ86

БИС К1810ВМ86 представляет собой однокристальный высокопроизводительный 16 - разрядный микропроцессор, выполненный по усовершенствованной n-канальной МОП-технологии, позволившей получить среднее время задержки распространения сигналов на вентиль 2 не и обеспечить высокую функциональную плотность.

Основными архитектурными особенностями микросхемы К1810ВМ86, позволяющими больше чем на порядок повысить производительность систем, являются:

1) более мощная система команд с расширенными возможностями адресации памяти, включающая команды умножения. деления и обработки последовательностей байтов или слов:

2) аппаратная реализация процесса совмещения операции выполнения и выборки команд;

3) более гибкая и мощная организация системы прерываний:

4) аппаратная реализация некоторых механизмов взаимодействия нескольких процессоров, упрощающая построение сложных мультипроцессорных систем.

Основные системные характеристики микропроцессора К1810ВМ86

Тактовая частота. МГц 5

Объем адресуемой памяти. Mбайт 1

Разрядность адресной шины 20

Разрядность шины данных 16

Число адресуемых устройств:

ввода/вывода 216/216

основных команд 133

Максимальная потребляемая мощность, Вт 1,75

Тип корпуса 2123.40-6(7)

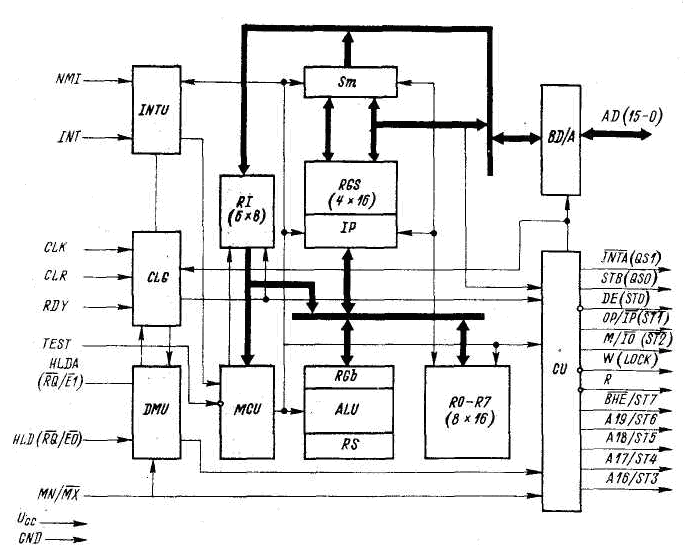

Рисунок 1 – Структурная схема микропроцессора К1810ВМ86

Структурная схема микропроцессора К1810ВМ86 представлена на рисунке 1 , она включает следующие устройства арифметико-логическое устройство (ALU) с тремя регистрами временного хранения операндов (RGB) и регистром признаков (RS); группу регистров общего назначения (R0 - R7); микропрограммное устройство управления (MCU) для управления выполнением команд; схему управления доступом к магистрали (DMU); схему внутренней синхронизации (CLG), преобразующую внешние тактовые импульсы во внутренние последовательности синхроимпульсов и обеспечивающую синхронизацию МП с медленными ЗУ и УВВ; схему обработки запросов прерываний (INTU); схему управления циклами обмена (СU), осуществляющую управление работой 16-разрядного канала адреса/данных; буферы канала адреса/ данных (BD/A); указатель команд (IP), выполняющий функции программного счетчика; сегментные регистры (RGS), содержащие базовые адреса программ, данных и стека; сумматор адреса (Sm), служащий для вычисления 20-разрядного физического адреса; регистры очереди команд (RI), предназначенные для формирования шестибайтной очереди команд, готовых к исполнению.

Отличительной особенностью архитектуры микропроцессора К181ОВМ86 является наличие двух основных асинхронно работающих устройств: устройства обработки (УО) и устройства сопряжения канала (УСК). Упрощенная структурная схема, представляющая МП в виде двух независимых устройств, изображена на рисунок 2. УО декодирует и выполняет команды, а УСК осуществляет связь с внешними устройствами, обеспечивает выборку команд и данных из памяти, формирует очередь команд. Организация параллельной работы УО и УСК и уменьшение конфликтных ситуаций при обращении к памяти за счет применения очереди команд позволяет существенно повысить производительность систем на основе микропроцессора К181ОВМ86.

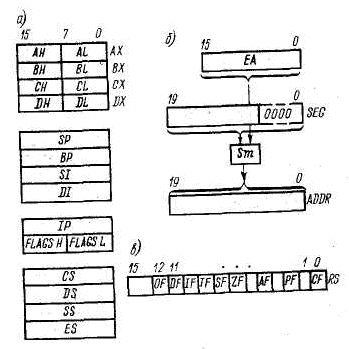

Регистровая модель микропроцессора К181ОВМ86 приведена на рисунке 3. Регистры CS, DS, SS и ES называются сегментными регистрами и используются при обращении к памяти для вычисления физических адресов ячеек.

Рисунок 3 – Регистровая модель микропроцессора К181ОВМ86

Основное назначение этих регистров следующее: регистр программного или кодового сегмента (CS) определяет текущий программный сегмент; содержимое регистра CS вместе с содержимым указателя команд (IP) задает адрес очередной команды выполняемой программы; регистр сегмента данных, или информационного сегмента (DS), используется в командах при обращении к данным; регистр стекового сегмента (SS) определяет текущий стековый сегмент и используется в командах обращения к стеку, при обработке подпрограмм и прерывании; регистр дополнительного сегмента (ES) обычно применяется как вспомогательный сегмент данных.

Регистры общего назначения АХ, ВХ, СХ и DX, называемые также регистрами данных, используются при выполнении арифметических и логических операций. Эти же регистры могут выполнять некоторые специальные функции, что и нашло отражение в их мнемонических обозначениях: АХ - аккумулятор, ВХ - базовый регистр, СХ – счетчик, DX - регистр данных. Эти регистры общего назначения допускают раздельную адресацию старшим (H) и младшим (L) половинам и могут использоваться в виде набора 8-разрядных регистров.

Регистры общего назначения SP, ВР, SI и DI называются адресными регистрами, так как в них хранятся относительные адреса, используемые для определения адресов операндов в пределах одного из сегментов памяти. В указателе стека (SP) и в указателе базы (ВР) содержатся относительные адреса в пределах стекового сегмента памяти, а в регистре индекса источника (SI) и. регистре индекса приемника {DI) хранятся относительные адреса в пределах сегмента данных.

В пределах любого из сегментов емкостью в 64К байт обращение к операндам происходит с помощью 16-разрядного адреса смещения в сегменте. Этот адрес определяется способом адресации и называется также исполнительным адресом (ЕЛ). 20-разрядный физический адрес памяти (ADDR) формируется в сумматоре адреса (Sm) посредством сложения 16-разрядного адреса смещения в сегменте с 16-разрядным адресом в сегментном регистре, сдвинутым на четыре разряда влево (рис. 3,б).

Рассмотренные функции регистров микропроцессора К181ОВМ86 являются основными и реализуются в командах по умолчанию. Дополнительные возможности использования регистров указываются при описании конкретных видов команд.

Регистр признаков или флагов (RS) состоит из одноразрядных регистров, фиксирующих состояние процессора и применяемых для управления его функционированием (рис. 3, в). Флаги CF, PF, AF, SF и ZF аналогичны флагам микропроцессора КР580ИК80А и характеризуют результат выполнения последней арифметической или логической операции. Флаг переполнения OF устанавливается в состояние 1 при переполнении, возникающем в результате арифметических операций над величинами со знаком. Флаги DF, IF и TF применяются для управления микропроцессором. Флаг направления DF служит для автоматического увеличения или уменьшения адреса при обработке последовательностей символов (имитация режимов автоинкрементной и автодекрементной адресации). Установка флага разрешения прерывания IF разрешает МП-прием запроса прерывания на входе INT. Установка флага трассировки TF переводит МП в состояние прерывания после выполнения каждой команды, т. е. организует режим пошагового выполнения программ.

Микропроцессор К1810ВМ86 предназначен для использования как в простых однопроцессорных, так и в сложных мультипроцессорных системах управления и обработки информации. В связи с этим МП имеет специальный вывод MN/MX (рис.1) для задания минимального или максимального режимов функционирования. Каждый режим характеризуется некоторым набором управляющих сигналов, соответствующим сложности проектируемой системы. При подключении вывода MN/MX к выводу Uее микропроцессор настраивается на работу в минимальном режиме, в котором все сигналы управления периферийными устройствами вырабатываются самим МП. При подключении вывода MNIMX к выводу GND происходит изменение функций ряда управляющих сигналов и МП перенастраивается на работу в максимальном режиме. В этом режиме МП используется обычно с системным контроллером, генерирующим сигналы управления системой. Управляющие сигналы максимального режима работы на рисунке 1 заключены в круглые скобки.

Назначения выводов МП и соответствующих им сигналов, общих как для максимального, так и для минимального режимов, приведены в таблице 1. Назначения выводов, относящиеся только к минимальному режиму, даны в таблице 2, а только к максимальному — в таблице 3. В максимальном режиме, как это видно из таблицы 3, МП использует лишь три вывода ST0 — ST2 для управления периферией и ЗУ через контроллер, а на остальных пяти выводах генерируются сигналы, необходимые для организации работы МП в мультипроцессорных системах.

Микропроцессор К1810ВМ86 осуществляет обмен информацией с ЗУ и ВУ через 16-разрядный канал адреса/данных с помощью временного мультиплексирования. Цикл функционирования канала включает обычно выдачу адресов ЗУ или УВВ. данных, а также сигналов, сопровождающих процесс обмена, и состоит из четырех машинных тактов (T1, Т2, Т3, Т4). В такте T1 в канал выдается адрес ЗУ или

УВВ.

Таблица 1– Описание выводов МП, общих для максимального и

минимального режимов

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

AD(15-0)

|

39; 2-16

|

Тристабильные входы/выходы канала, образующие адресную шину в такте обращения к памяти Т1 и шину данных в последующих тактах (Т2, Т3, Тw, Т4)

|

|

A19/ST6; A18/ST5; A17/ST4; A16/ST3

|

35-38

|

Тристабильные выходы, образующие четыре старших разряда адреса памяти в такте Т1 и сигналы состояния в последующих тактах: ST5 – состояние триггера разрешения прерывания: ST4 и ST3 служат для указания используемого в цикле обмена сегментного регистра.ST6 – сигнал L – уровня

|

|

BHE/ST7

|

34

|

Тристабильные выход, используемый для разрешения передачи данных по старшей половине шины AD(15-8) в такте Т1 по L – уровню сигнала BHE и как сигнал состояния ST7 в тактах Т2, Т3, Т4

|

продолжение таблицы 1

|

1 |

2 |

3 |

|

R

|

32

|

Тристабильные выход сигнала чтения L – уровня, используемого для считывания информации из устройств, подключенных к каналу МП, и выдаваемого в тактах Т2, Т3, Т4 каждого цикла чтения

|

|

RDY

|

22

|

Вход сигнала готовности H – уровня, поступающего от внешних устройств и подтверждающего их готовность к обмену |

|

INT

|

18

|

Вход маскируемого запроса прерывания H – уровня |

|

NMI

|

17

|

Вход немаскируемого запроса прерывания (по положительному перепаду на входе) |

|

TEST

|

23

|

Вход сигнала проверки, анализируемый специальной командой ожидания WAIT |

|

CLR |

21

|

Вход сигнала установки внутренних схем МП

|

|

CLK

|

19

|

Вход тактовых сигналов синхронизации

|

|

MN/

|

33

|

Вход сигнала управления режимом работы МП |

продолжение таблицы 1

|

1 |

2 |

3 |

|

UCC

|

40

|

Напряжение питания (+5 В)

|

|

GND |

1; 20 |

Напряжение питания (0 В) |

Таблица 2 – Описание выводов МП, используемых для минимального

режима

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

W

|

29

|

Тристабильны выход сигнала записи L

– уровня, используемого для записи

информации в ЗУ или УВВ в зависимости

от состояния сигнала M/

|

|

M/

|

28

|

Тристабильный выход сигнала обращения к ЗУ или УВВ вырабатываемого в такте предшествующего цикла и поддерживаемого до завершения такта Т4 текущего цикла L – уровня сигнала соответствует обращению к УВВ, а H – уровень – обращению к ЗУ |

|

OP/

|

27

|

Тристабильный выход передачи или приема данных, предназначенный для управления направлением обмена информацией через шинные формирователи |

продолжение таблицы 2

|

1 |

2 |

3 |

|

DE

|

26

|

Тристабильный выход сигнала разрешения передачи данных L – уровня, выдаваемый в каждом цикле обращения к ЗУ или УВВ и в циклах подтверждения прерывания |

|

STB

|

25

|

Выход строба адреса – сигнала H – уровня, используемого для записи адреса во внешний буферный регистр адреса и генерируемого в такте Т1 любого цикла канала |

|

INTA

|

24

|

Выход сигнала подтверждения прерывания L – уровня, генерируемого в тактах Т2, Т3 и Тw каждого цикла подтверждения прерывания |

|

HLD

|

31

|

Выход сигнала захвата, указывающего на запрос канала другим процессором |

|

HLDA |

30 |

Выход сигнала подтверждения захвата, сопровождающегося переводом канала и шин управления в высокоимпедансное состояние |

Таблица 3 – Описание выводов МП, используемых для максимального

режима

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

ST0 - ST2

|

26; 27; 28

|

Тристабильные выходы сигналов состояния цикла канала, генерируемых в тактах Т4, Т1 и Т2 и используемых контроллером канала для выработки сигналов управления обменом информации с ЗУ и УВВ |

продолжение таблицы 3

|

1 |

2 |

3 |

|

RQ/E1 RQ/EO |

30; 31

|

Двунаправленные выводы сигналов запроса/разрешения доступа к магистрали, используемых другими устройствами, чтобы отключить МП от канала в конце текущего цикла канала; приоритет вывода RQ/EO выше, чем вывода RQ/E1 |

|

LOCK

|

29

|

Тристабильный выход сигнала блокировки системного канала, указывающего другим устройствам на запрет использования системного канала, пока сигнал LOCK имеет L – уровень

|

|

QS1, QS0 |

24; 25 |

Выходы сигналов состояния очереди команд |

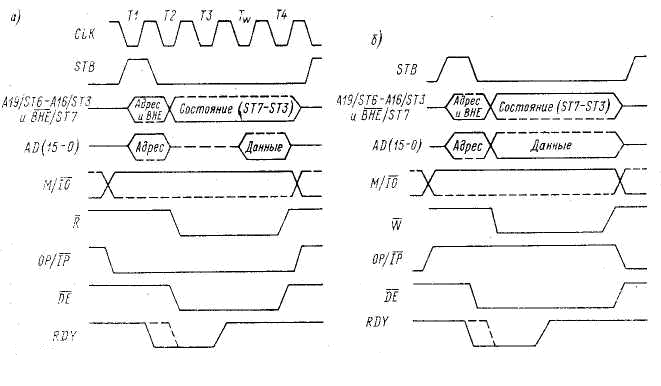

Рисунок 4 – Временные диаграммы циклов чтения и записи для

минимального режима

Обмен данными для цикла записи происходит в тактах Т2, Т3,Т4 а для цикла чтения — в тактах Т3, Т4. Такт Т2 в цикле чтения используется тля переключения МП из режима записи в режим чтения, а канал переводится в высокоимпедансное состояние. Для согласования с медленными УВВ или ЗУ с помощью сигнала RDY между тактами Т3 и Т4 могут включаться дополнительные такты ожидания (Тw), в течение которых данные в канале остаются неизменными. Наконец, в ряде случаев между отдельными циклами канала могут вводиться холостые такты (Т5).

Временные диаграммы циклов чтения и записи для минимального режима приставлены на рисунке 4. В цикле чтения (рис. 4, а) выдается сигнал чтения R, а также сигналы управления направлением обмена РО / IР и разрешением передачи данных DE. Сигнал DE разрешает шинным формирователям передать длимые в МП. В цикле записи (рис. 4, б) сигнал DE выдается раньше, чем в цикле чтения, а выдача данных и сигнала записи W производится по переднему фронту в такте Т2. Для многих ЗУ и УВВ требуется постоянство адреса в течение всего цикла канала, поэтому в такте Т1, каждого цикла выдается стробирующий сигнал STB, позволяющий зафиксировать адрес по заднему фронту сигнала STB. Сигналы состояния ST3, ST4 указывают сегментный регистр, используемый в текущем цикле канала для вычисления физического адреса ячейки памяти.

Три 16-разрядных регистра очереди команд (RI) микропроцессора обеспечивают временное хранение 6 байт очереди команд (рис. 1). УО микропроцессора при выполнении команды извлекает из очереди байт кода команды, не требуя доступа к каналу. УСК микропроцессора следит за состоянием очереди команд, пополняя ее, когда другие системные элементы не занимают память. При выполнении команд передачи управления очередь сбрасывается и после завершения перехода в место передачи управления начинает заполняться вновь. В максимальном режиме МП передает информацию о состоянии очереди на выходы QS0 и QSI.

-

БИС ОЗУ К565РУ6

ОЗУ динамического типа серии К565. Микросхемы серии К565 представляют собой оперативные запоминающие устройства с произвольной выборкой динамического типа, изготавливаются по n-канальной МОП-технологии с кремниевыми затворами и двумя типами транзисторов (с индуцированным и встроенным каналом) и предназначены для построения накопителей ОЗУ большой емкости.

В состав серии входят: К565РУ5 (Б, В, Г, Д) емкостью 65 536 бит с организацией 65536x1 бит; К565РУ5 (Д1, Д2) емкостью 32 763 бит с организацией 32 768 х I бит; К565РУ5 (ДЗ, Д4) емкостью 16 384 бит с организацией 16 384 х 1 бит; КР565РУ6 (Б, В, Г, Д) емкостью 16 384 бит с организацией 16384 х 1 бит. Внешние сигналы: RAS — сигнал выбора адреса строк, С AS — сигнал выбора адреса столбцов, WE — сигнал записи/считывания, а также сигналы, вырабатываемые схемой управления, обеспечивают работу ОЗУ в режимах считывания, записи, постраничного считывания или постраничной записи, считывания-модификации-записи, регенерации по сигналу RAS.

Временные диаграммы работы микросхем в режимах считывания, записи. считывание — модификация — запись, регенерации приведены на рисунке 5 г - ж. Это позволяет при работе в страничном режиме получить значительный выигрыш в быстродействии. Внутри страничного режима возможна любая комбинация режимов записи, считывания и считывание — модификация — запись.

Регенерация информации в динамических ячейках памяти осуществляется за 128 циклов путем обращения к каждой из 128 строк не ранее, чем через каждые 2 мс перебором адресов /1(0 — 6). Регенерация может быть осуществлена в любом из режимов ОЗУ, однако наиболее просто ее выполнить в режиме регенерации по сигналу RAS. когда сигнал CAS находится в неактивном высоком логическом состоянии (регенерация сигналом RAS). При регенерации в этом режиме имеет место минимальная потребляемая мощность. При эксплуатации микросхем необходимо помнить, что после подачи напряжения питания БИС ОЗУ переходит в нормальный режим функционирования через 2,0 мс и требует проведения затем 16 рабочих циклов регенерации.