Содержание

Введение 4

1 Расшифровка и анализ задания 5

2 Разработка процессорного модуля, интерфейса и упрощенной

структурной схемы микропроцессорной системы 7

2.1 Архитектура и режимы работы микропроцессора К1810ВМ86 7

2.2 Генератор тактовых импульсов 15

2.3 Буферный регистр КР580ИР82 18

2.4 Шинные формирователь КР580ВА86 20

2.5 Контроллер шин К1810ВГ88 23

2.6 Арбитр шин К1810ВБ89 26

2.7 АЦП К589ПВ2 30

2.8 Программируемый таймер КР580ВИ53 31

2.9 Разработка уточненной структурной схемы 33

3 Разработка систем памяти 37

3.1 Оперативное запоминающее устройство К565РУ6 37

3.2 Постоянное запоминающее устройство К541РТ2 39

4 Разработка подсистем ввода/вывода, прерывания и прямого

доступа к памяти 42

4.1 Программируемый параллельный интерфейс подсистемы ввода/

вывода КР580ВВ55 42

4.2 Подсистема прерываний 44

4.3 Разработка контроллера прямого доступа к памяти 49

4.4 Уточненная структурная схема микропроцессорной системы 53

4.5 Функциональная схема микропроцессорной системы 54

5 Разработка алгоритма управляющей программы 55

6 Реализация ЕС1834 – ППЭВМ комбината "Роботрон" на базе МП

К1810ВМ86 57

Заключение 60

Список используемых источников 61

Приложение А 62

Введение

Развитие микроэлектронной технологии, обеспечившее появление больших и сверхбольших интегральных схем (СБИС), создало предпосылки для резкого снижения стоимости систем управления (СУ). Но практическая реализация достижения технологии БИС и СБИС стало возможным после создания МП. МП – универсальный компонент, который стал связующим звеном для нового поколения изделий микроэлектроники, и обеспечил их функциональную полноту.

Существенным отличие МП од других элементов радиоэлектроники является замена физического, схемного метода реализации заданных функций, математическим программным методом.

Этот метод предоставляет проектировщику большие возможности, т.е. снимает ряд физических ограничений при реализации различных функций, обеспечивает независимость характеристик от физических условий применения. Важным свойством МП является высокая гибкость, возможность быстрой перенастройки при необходимости даже значительных изменение в алгоритмах управления.

Целью курсового проектирования по дисциплине «Микропроцессорные устройства систем управления» является обобщение, закрепление и углубление знаний по дисциплинам: «Электроника и микросхемотехника», «Вычислительные машины и системы», «Микропроцессорные устройства систем управления», формирование навыков разработки и оформления текстовой и графической документации; развитие навыков устных сообщений по содержанию курсового проекта. Целью курсового проекта является разработка микропроцессорной управляющей микроЭВМ, реализующей заданные взаимодействия с объектом управления (ОУ) и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

1 Расшифровка и анализ задания

Содержанием курсового проекта является разработка микропроцессорной управляющей микроЭВМ, реализующие заданные взаимодействия с объектом управления (ОУ) и разработка программных средств системы, обеспечивающих выполнение заданного алгоритма управления.

Заданием на курсовой проект определено, что базовым микропроцессором, на основе которого требуется построить управляющую микроЭВМ, является МП К1810ВМ86.

Тип БИС ОЗУ: К565РУ6, тип БИС ПЗУ: К541РЕ1.

Алгоритм

управления определяется функцией:

![]() ,

с длительностью импульса

,

с длительностью импульса![]() ,

и функцией

,

и функцией![]() ,

с длительностью импульсов

,

с длительностью импульсов![]() ;

;![]() .

.

Обработка

информации от цифровых датчиков и выдача

управляющего воздействия

![]() производиться

путем ввода значений

производиться

путем ввода значений![]() и

вычисления значения булевой функции

и

вычисления значения булевой функции![]() .

.

При

единичном значении

![]() вырабатывается управляющий сигнал

вырабатывается управляющий сигнал![]() ,

длительность

,

длительность![]() .

Это значит, что через

.

Это значит, что через![]() после выдачи

после выдачи![]() необходимо выработать

необходимо выработать![]() .

.

При

обработке информации с аналоговых

датчиков МП принимает коды

![]() с выходов АЦП и код константы К с регистра

пульта управления. Далее вычисляется

значение функции

с выходов АЦП и код константы К с регистра

пульта управления. Далее вычисляется

значение функции![]() и сравнивается с константойQ,

хранящейся в ПЗУ. В зависимости от

результатов сравнения вырабатывается

(аналогично

и сравнивается с константойQ,

хранящейся в ПЗУ. В зависимости от

результатов сравнения вырабатывается

(аналогично

![]() )

один из двух двоичных управляющих

сигналов

)

один из двух двоичных управляющих

сигналов![]() или

или![]() заданной длительности по следующему

правилу: если

заданной длительности по следующему

правилу: если![]() ,

то выдать

,

то выдать![]() ,

длительностью

,

длительностью![]() ,

иначе выдать

,

иначе выдать![]() ,

длительностью

,

длительностью![]() .

.

Далее

формируется управляющее воздействие

![]() ,

для чего с АЦП вводится значение

,

для чего с АЦП вводится значение![]() и производиться вычисление по формуле:

и производиться вычисление по формуле:

![]()

Значение

![]() в виде 8 - разрядного кода выдается на

вход АЦП.

в виде 8 - разрядного кода выдается на

вход АЦП.

После выдачи всех управляющих воздействий проверяется состояние тумблера «СТОП».

В системе необходимо предусмотреть следующие линии запроса на внешние прерывания:

![]() -

отказ источника питания;

-

отказ источника питания;

![]() -

сигнал

-

сигнал

![]() аварийного датчика ОУ;

аварийного датчика ОУ;

![]() -

запрос от пульта управления(прерывание

оператора);

-

запрос от пульта управления(прерывание

оператора);

![]() -

запрос от микро ЭВМ верхнего уровня.

-

запрос от микро ЭВМ верхнего уровня.

Управляющая микро ЭВМ проектируется на базе однокристального МП и включает в себя следующие основные устройства:

- процессорный модуль;

- генератор тактовых импульсов;

- память, состоящую из ОЗУ и ПЗУ;

- программируемы системный таймер;

- блок последовательного ввода/вывода для связи с ОУ;

- контроллер прерываний.

Все модули системы объединяются интерфейсом(магистралью), требования к которому определяются заданным типом микропроцессора (микро-ЭВМ).

Процессорный модуль включает в себя микропроцессор (микроЭВМ) и, при необходимости, дополнительные БИС (СИС), обеспечивающие реализацию вспомогательных функций (тактовый генератор, шинные формирователи, регистры-защелки и др.).

Устройства ввода для связи с ОУ должны обеспечить ввод в ПМ значений x1, x2, x3, x4 двоичных датчиков, а так же 8-разрядных двоичных кодов NU1, NU2, NU3, принимаемых с выходов АЦП. Сигнал датчика аварийной ситуации xa воспринимается только подсистемой прерываний.

Устройства вывода на ОУ должны обеспечить выдачу двоичных управляющих воздействий y1, y2, y3 определенной длительности и кода управляющего напряжения Y4 - 8-разрядного двоичного вектора на вход ЦАП.

Пульт управления должен обеспечивать ввод в ПМ значения 8-разрядной двоичной константы К, ввод двоичного значения сигнала "СТОП", формирование сигнала начальной установки системы, вывод на светодиодную индикацию значений x1, x2, x3, x4, y1, y2, y3, NU1, Y4.

Системный таймер должен обеспечить отсчет временных задержек, реализуемых при работе алгоритма управления.

Контроллер прерываний обеспечивает фиксацию запросов на прерывания от различных источников и дисциплину обслуживания запросов.

2 Разработка процессорного модуля, интерфейса и

уПРОЩЕнной структурной схемы

2.1 Архитектура и режимы работы микропроцессора К1810ВМ86

БИС К1810ВМ86 представляет собой однокристальный высокопроизводительный 16-разрядный микропроцессор, выполненный по усовершенствованной n-канальной МОП-технологии, позволившей получить среднее время задержки распространения сигналов на вентиль 2 не и обеспечить высокую функциональную плотность (29 тыс. транзисторов на кристалл).

Основными архитектурными особенностями микросхемы К1810ВМ86, позволяющими больше чем на порядок повысить производительность систем, являются:

1) более мощная система команд с расширенными возможностями адресации памяти, включающая команды умножения, деления и обработки последовательностей байтов или слов;

2) аппаратная реализация процесса совмещения операции выполнения и выборки команд;

3) более гибкая и мощная организация системы прерываний;

4) аппаратная реализация некоторых механизмов взаимодействия нескольких процессоров, упрощающая построение сложных мультипроцессорных систем.

Основные системные характеристики микропроцессора К1810ВМ86.

Тактовая частота, МГц 5.

Объем адресуемой памяти, Mбайт 1.

Разрядность адресной шины 20.

Разрядность шины данных 16.

Число адресуемых устройств:

ввода/вывода 216/216;

основных команд 133.

Максимальная потребляемая мощность, Вт 1,75.

Тип корпуса 2123.40-6(7).

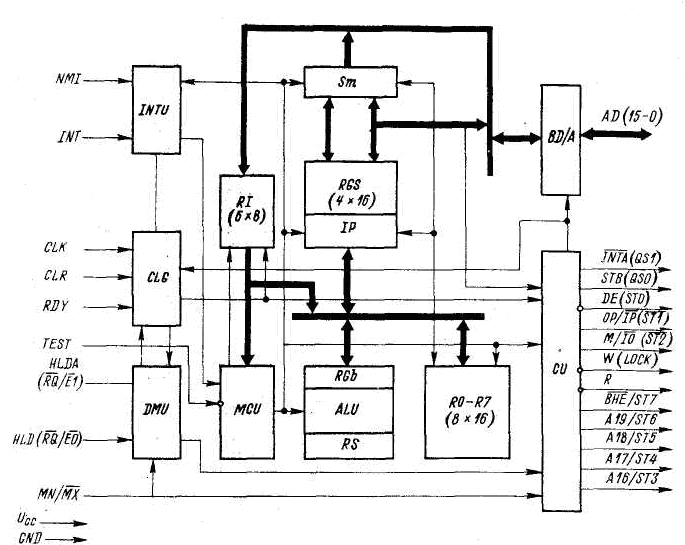

Рисунок 1 – Структурная схема микропроцессора К1810ВМ86

Структурная схема микропроцессора К1810ВМ86 представлена на рисунке 1, она включает следующие устройств арифметико-логическое устройство (ALU) с тремя регистрами временного хранения операндов (RGB) и регистром признаков (RS); группу регистров общего назначения (R0 - R7); микропрограммное устройство управления (MCU) для управления выполнением команд; схему управления доступом к магистрали (DMU); схему внутренней синхронизации (CLG), преобразующую внешние тактовые импульсы во внутренние последовательности синхроимпульсов и обеспечивающую синхронизацию МП с медленными ЗУ и УВВ; схему обработки запросов прерываний (INTU); схему управления циклами обмена (СU), осуществляющую управление работой 16-разрядного канала адреса/данных; буферы канала адреса/ данных (BD/A); указатель команд (IP), выполняющий функции программного счетчика; сегментные регистры (RGS), содержащие базовые адреса программ, данных и стека; сумматор адреса (Sm), служащий для вычисления 20-разрядного физического адреса; регистры очереди команд (RI), предназначенные для формирования шестибайтной очереди команд, готовых к исполнению.

Отличительно особенностью архитектуры микропроцессора К1810ВМ86 является наличие двух основных асинхронно работающих устройств: устройства обработки (УО) и устройства сопряжения канала (УСК). Упрощенная структурная схема, представляющая МП в виде двух независимых устройств. УО декодирует и выполняет команды, а УСК осуществляет связь с внешними устройствами, обеспечивает выборку команд и данных из памяти, формирует очередь команд. Организация параллельной работы УО и УСК и уменьшение конфликтных ситуаций при обращении к памяти за счет применения очереди команд позволяет существенно повысить производительность систем на основе микропроцессора К1810ВМ86.

Регистровая модель микропроцессора К1810ВМ86 приведена на рисунке 2. Регистры CS, DS, SS и ES называются сегментными регистрами и используются при обращении к памяти для вычисления физических адресов ячеек.

Рисунок 2 – Регистровая модель микропроцессора К1810ВМ86

Основное назначение этих регистров следующее: регистр программного или кодового сегмента (CS) определяет текущий программный сегмент; содержимое регистра CS вместе с содержимым указателя команд (IP) задает адрес очередной команды выполняемой программы; регистр сегмента данных, или информационного сегмента (DS), используется в командах при обращении к данным; регистр стекового сегмента (SS) определяет текущий стековый сегмент и используется в командах обращения к стеку, при обработке подпрограмм и прерывании; регистр дополнительного сегмента (ES) обычно применяется как вспомогательный сегмент данных.

Регистры общего назначения АХ, ВХ, СХ и DX, называемые также регистрами данных, используются при выполнении арифметических и логических операций. Эти же регистры могут выполнять некоторые специальные функции, что и нашло отражение в их мнемонических обозначениях: АХ - аккумулятор, ВХ - базовый регистр, СХ - счетчик, DX - регистр данных. Эти регистры общего назначения допускают раздельную адресацию старшим (H) и младшим (L) половинам и могут использоваться в виде набора 8-разрядных регистров.

Регистры общего назначения SP, ВР, SI и DI называются адресными регистрами, так как в них хранятся относительные адреса, используемые для определения адресов операндов в пределах одного из сегментов памяти. В указателе стека (SP) и в указателе базы (ВР) содержатся относительные адреса в пределах стекового сегмента памяти, а в регистре индекса источника (SI) и. регистре индекса приемника (DI) хранятся относительные адреса в пределах сегмента данных.

В пределах любого из сегментов емкостью в 64К байт обращение к операндам происходит с помощью 16-разрядного адреса смещения в сегменте. Этот адрес определяется способом адресации и называется также исполнительным адресом (ЕЛ). 20-разрядный физический адрес памяти (ADDR) формируется в сумматоре адреса (Sm) посредством сложения 16-разрядного адреса смещения в сегменте с 16-разрядным адресом в сегментном регистре, сдвинутым на четыре разряда влево.

Рассмотренные функции регистров микропроцессора К1810ВМ86 являются основными и реализуются в командах по умолчанию. Дополнительные возможности использования регистров указываются при описании конкретных видов команд.

Регистр признаков или флагов (RS) состоит из одноразрядных регистров, фиксирующих состояние процессора и применяемых для управления его функционированием. Флаги CF, PF, AF, SF и ZF аналогичны флагам микропроцессора КР580ИК80А и характеризуют результат выполнения последней арифметической или логической операции. Флаг переполнения OF устанавливается в состояние 1 при переполнении, возникающем в результате арифметических операций над величинами со знаком. Флаги DF, IF и TF применяются для управления микропроцессором. Флаг направления DF служит для автоматического увеличения или уменьшения адреса при обработке последовательностей символов (имитация режимов автоинкрементной и автодекрементной адресации). Установка флага разрешения прерывания IF разрешает МП-прием запроса прерывания на входе INT. Установка флага трассировки TF переводит МП в состояние прерывания после выполнения каждой команды, т. е. организует режим пошагового выполнения программ.

Микропроцессор К1810ВМ86 предназначен для использования как в простых однопроцессорных, так и в сложных мультипроцессорных системах управления и обработки информации. В связи с этим МП имеет специальный вывод MN/MX рисунок 1 для задания минимального или максимального режимов функционирования. Каждый режим характеризуется некоторым набором управляющих сигналов, соответствующим сложности проектируемой системы. При подключении вывода MN/MX к выводу Uее микропроцессор настраивается на работу в минимальном режиме, в котором все сигналы управления периферийными устройствами вырабатываются самим МП. При подключении вывода MNIMX к выводу GND происходит изменение функций ряда управляющих сигналов и МП перенастраивается на работу в максимальном режиме. В этом режиме МП используется обычно с системным контроллером, генерирующим сигналы управления системой. Управляющие сигналы максимального режима работы на рисунке 1 заключены в круглые скобки.

Назначения выводов МП и соответствующих им сигналов, общих как для максимального, так и для минимального режимов, приведены в таблице 1. Назначения выводов, относящиеся только к минимальному режиму, даны в таблице 2, а только к максимальному — в таблице 3. В максимальном режиме, как это видно из таблицы 3, МП использует лишь три вывода ST0 — ST2 для управления периферией и ЗУ через контроллер, а на остальных пяти выводах генерируются сигналы, необходимые для организации работы МП в мультипроцессорных системах.

Микропроцессор К1810ВМ86 осуществляет обмен информацией с ЗУ и ВУ через 16-разрядный канал адреса/данных с помощью временного мультиплексирования. Цикл функционирования канала включает обычно выдачу адресов ЗУ или УВВ. данных, а также сигналов, сопровождающих процесс обмена, и состоит из четырех машинных тактов (T1, Т2, Т3, Т4). В такте T1 в канал выдается адрес ЗУ или УВВ.

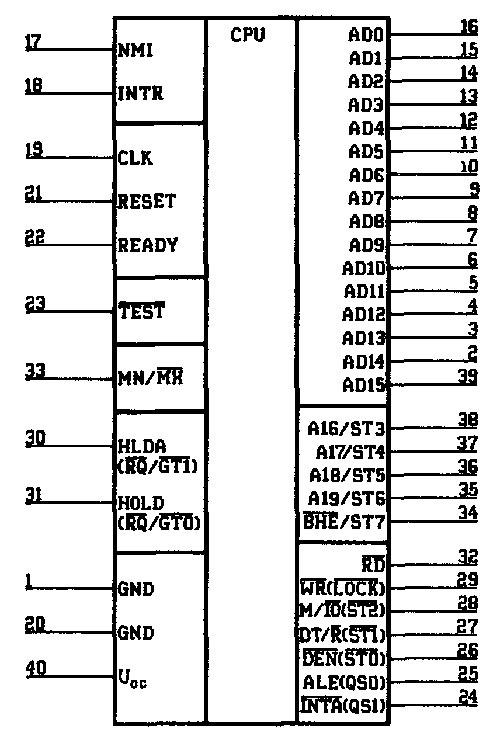

Рисунок 3 – Условно-графическое обозначение МП К1810ВМ6

Таблица 1– Описание выводов МП, общих для максимального и

минимального режимов

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

AD(15-0)

|

39; 2-16

|

Тристабильные входы/выходы канала, образующие адресную шину в такте обращения к памяти Т1 и шину данных в последующих тактах (Т2, Т3, Тw, Т4) |

|

A19/ST6; A18/ST5; A17/ST4; A16/ST3

|

35-38

|

Тристабильные выходы, образующие четыре старших разряда адреса памяти в такте Т1 и сигналы состояния в последующих тактах: ST5 – состояние триггера разрешения прерывания: ST4 и ST3 служат для указания используемого в цикле обмена сегментного регистра. ST6 – сигнал L – уровня |

|

RD

|

32

|

Тристабильные выход сигнала чтения L – уровня, используемого для считывания информации из устройств, подключенных к каналу МП, и выдаваемого в тактах Т2, Т3, Т4 каждого цикла чтения |

|

BHE/ST7

|

34

|

Тристабильные выход, используемый для разрешения передачи данных по старшей половине шины AD (15-8) в такте Т1 по L – уровню сигнала BHE и как сигнал состояния ST7 в тактах Т2, Т3, Т4 |

Продолжение таблицы 1

|

1 |

2 |

3 |

|

READY

|

22

|

Вход сигнала готовности H – уровня, поступающего от внешних устройств и подтверждающего их готовность к обмену |

|

INTR

|

18

|

Вход маскируемого запроса прерывания H – уровня |

|

NMI

|

17

|

Вход немаскируемого запроса прерывания (по положительному перепаду на входе) |

|

TEST

|

23

|

Вход сигнала проверки, анализируемый специальной командой ожидания WAIT |

|

RESET

|

21

|

Вход сигнала установки внутренних схем МП |

|

CLK

|

19

|

Вход тактовых сигналов синхронизации

|

|

MN/

|

33

|

Вход сигнала управления режимом работы МП |

|

UCC

|

40

|

Напряжение питания (+5 В) |

|

GND |

1; 20 |

Напряжение питания (0 В) |

Таблица 2 – Описание выводов МП, используемых для минимального

режима

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

WR

|

29

|

Тристабильны

выход сигнала записи L

– уровня, используемого для записи

информации в ЗУ или УВВ в зависимости

от состояния сигнала M/ |

|

M/

|

28

|

Тристабильный выход сигнала обращения к ЗУ или УВВ вырабатываемого в такте предшествующего цикла и поддерживаемого до завершения такта Т4 текущего цикла L – уровня сигнала соответствует обращению к УВВ, а H – уровень – обращению к ЗУ |

|

OP/R

|

27

|

Тристабильный выход передачи или приема данных, предназначенный для управления направлением обмена информацией через шинные формирователи |

|

DEN

|

26

|

Тристабильный выход сигнала разрешения передачи данных L – уровня, выдаваемый в каждом цикле обращения к ЗУ или УВВ и в циклах подтверждения прерывания |

|

ALE

|

25

|

Выход строба адреса – сигнала H – уровня, используемого для записи адреса во внешний буферный регистр адреса и генерируемого в такте Т1 любого цикла канала |

Продолжение таблицы 2

|

1 |

2 |

3 |

|

INTA

|

24

|

Выход сигнала подтверждения прерывания L – уровня, генерируемого в тактах Т2, Т3 и Тw каждого цикла подтверждения прерывания |

|

HOLD

|

31

|

Выход сигнала захвата, указывающего на запрос канала другим процессором |

|

HLDA

|

30 |

Выход сигнала подтверждения захвата, сопровождающегося переводом канала и шин управления в высокоимпедансное состояние |

Таблица 3 – Описание выводов МП, используемых для максимального

режима

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

ST0 - ST2

|

26; 27; 28

|

Тристабильные выходы сигналов состояния цикла канала, генерируемых в тактах Т4, Т1 и Т2 и используемых контроллером канала для выработки сигналов управления обменом информации с ЗУ и УВВ |

|

RQ/GT1 RQ/GT0

|

30; 31

|

Двунаправленные выводы сигналов запроса/разрешения доступа к магистрали, используемых другими устройствами, чтобы отключить МП от канала в конце текущего цикла канала; приоритет вывода RQ/GT0 выше, чем вывода RQ/GT1 |

Продолжение таблицы 3

|

1 |

2 |

3 |

|

LOCK

|

29

|

Тристабильный выход сигнала блокировки системного канала, указывающего другим устройствам на запрет использования системного канала, пока сигнал LOCK имеет L – уровень |

|

QS1, QS0 |

24; 25 |

Выходы сигналов состояния очереди команд |

Обмен данными для цикла записи происходит в тактах Т2, Т3,Т4 а для цикла чтения — в тактах Т3, Т4. Такт Т2 в цикле чтения используется тля переключения МП из режима записи в режим чтения, а канал переводится в высокоимпедансное состояние. Для согласования с медленными УВВ или ЗУ с помощью сигнала RDY между тактами Т3 и Т4 могут включаться дополнительные такты ожидания (Тw), в течение которых данные в канале остаются неизменными. Наконец, в ряде случаев между отдельными циклами канала могут вводиться холостые такты (Т5).

В цикле чтения выдается сигнал чтения R, а также сигналы управления направлением обмена Р0 / IР и разрешением передачи данных DE. Сигнал DE разрешает шинным формирователям передать длимые в МП. В цикле записи сигнал DEN выдается раньше, чем в цикле чтения, а выдача данных и сигнала записи WR производится по переднему фронту в такте Т2. Для многих ЗУ и УВВ требуется постоянство адреса в течение всего цикла канала, поэтому в такте Т1, каждого цикла выдается стробирующий сигнал STB, позволяющий зафиксировать адрес по заднему фронту сигнала STB. Сигналы состояния ST3, ST4 указывают сегментный регистр, используемый в текущем цикле канала для вычисления физического адреса ячейки памяти.

Три 16-разрядных регистра очереди команд (RI) микропроцессора обеспечивают временное хранение 6 байт очереди команд УО микропроцессора при выполнении команды извлекает из очереди байт кода команды, не требуя доступа к каналу. УСК микропроцессора следит за состоянием очереди команд, пополняя ее, когда другие системные элементы не занимают память. При выполнении команд передачи управления очередь сбрасывается и после завершения перехода в место передачи управления начинает заполняться вновь. В максимальном режиме МП передает информацию о состоянии очереди на выходы QS0 и QSI.

2.2 Буферные регистры КР580ИР82

При разработке функциональной схемы модуля центрального процессора возникает потребность в демультиплексировании шины адреса/данных, буферизации адреса и шин данных. Демультиплексирование осуществляется с помощью двух БИС К580ИР82, которые выполняют функции защелки адреса и буфера шины адреса. Он используется для реализации схем фиксации, буферизации и мультиплексирования в микропроцессорных системах на базе микропроцессоров серий К580ИК80А и К1810ВМ86. На выходах микросхемы КР580ИР82 генерируются неинвертированные входные данные.

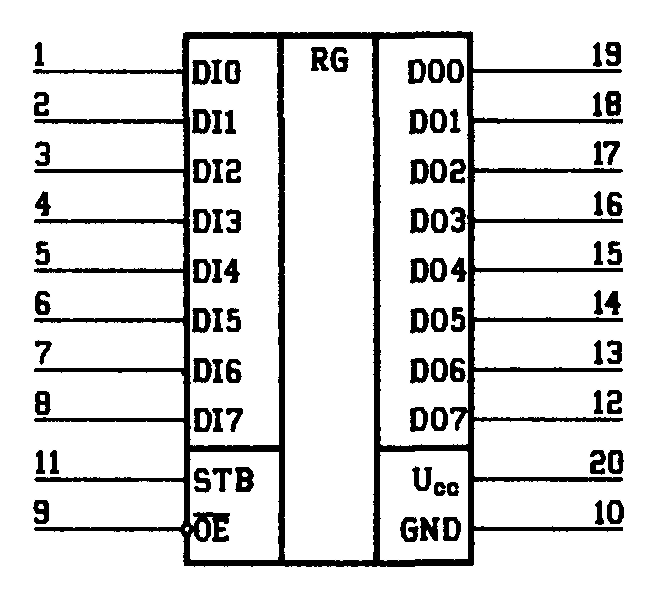

Структурная схема буферного регистра приведена на рисунке 4.

D

T

C RG DI

(7-0)

STB D0

(7-0)

0E

UCC

GND

Рисунок 4 – Структурная схема буферного регистра КР580ИР82

Запись входных данных в буферные регистры производится при переходе сигнала STB c H - уровня в L - уровень. При H - уровне сигнала 0Е, выходы буферных регистров находятся в высокоимпедансном состоянии.

Рисунок 5 – Условно-графическое обозначение К580ИР82

D17-D10 – линии входных данных;

D07-D00 – линии выходных данных;

STB – стробирующий сигнал;

![]() –разрешение

выдачи данных.

–разрешение

выдачи данных.

Буферные регистры К580ИР82 состоят из восьми информационных триггеров (Т) с выходными схемами (SW) с тремя состояниями, общими сигналами записи информации STB и управления выходными схемами ОЕ. К выходным схемам буферных регистров подключены прямые выходы информационных триггеров.

При

сигнале высокого уровня на входе STB

состояние входных линий D17-D10

передается на выходные линии D07-D00.

Запоминание (защелкивание) в

информационных триггерах осуществляется

при переходе сигнала STB

от высокого уровня к низкому (по срезу

сигнала STB).

Сигнал

![]() управляет выходными буферами: при

управляет выходными буферами: при![]() =0

буфер отпирается, при

=0

буфер отпирается, при![]() =1

он

устанавливается в z-состояние.

Сигнал

=1

он

устанавливается в z-состояние.

Сигнал

![]() не влияет ни на состояния информационных

триггеров, ни на функцию записи.

не влияет ни на состояния информационных

триггеров, ни на функцию записи.

Основные электрические параметры микросхемы КР580ИР82:

- выходное напряжение логического нуля UOL, В менее 0,5;

- выходное напряжение логической единицы UOH, В более 2,4;

- входное напряжение логического нуля UIL, В менее 0,8;

- входное напряжение логической единицы UIH, В более 2;

- ток потребления от источника питания IСС, мА менее 160;

- выходной ток утечки IOZ, мкА менее 50;

- время задержки tIO, с:

- с инвертированием менее 40;

- без инвертирования менее 45.

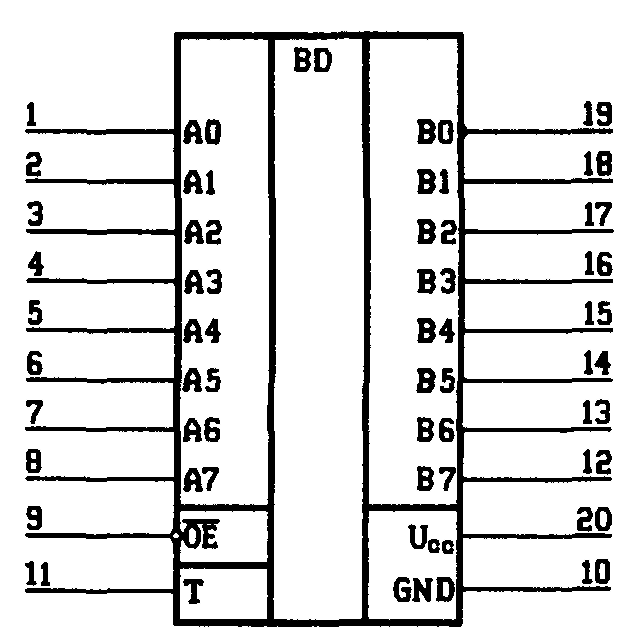

2.3 Шинный формирователь КР580ВА86

Восьмиразрядные шинные формирователи КР580ВА86 применяют как буферные устройства шины данных в микропроцессорных системах. Большая выходная мощность и простота управления позволяют использовать их для построения двунаправленных согласующих буферов межмодульной связи либо как простые усилительные каскады. Полная конструктивная совместимость с БР ИР82/83 допускает взаимозаменяемость при однонаправленной передаче.

Структурная схема шинного формирователя представлена на рисунке 6.

A

(7-0)

B

(7-0)

1 1

T

0E

UCC GND

Рисунок 6 – Структурная схема шинного формирователя КР580ВА86

Формирователь состоит из восьми одинаковых функциональных блоков с общими сигналами управления Т и ОЕ. Функциональные блоки состоят из двух усилителей-формирователей с z-состояниями на выходах, схема включения которых обеспечивает разнонаправленную передачу. Формирователь К580ВА86 не инвертирует данные (рисунок 6, 7).

Рисунок 7 – Условно-графическое обозначение К580ВА86

А7-А0 – вход/выход линий данных. В зависимости от состояния входа Т они могут быть входными, если на Т – сигнал высокого уровня, и выходными, если на Т – сигнал низкого уровня.

В7-В0 – вход/выход линий данных. Они являются входными, если на Т – сигнал низкого уровня, и выходными, если на Т – сигнал высокого уровня.

Т – входной сигнал управления направлением передачи. При Т=0 осуществляется передача от В к А (режим В→А), при Т=1 – от А к В. Сигнал Т выбирает верхний или нижний усилитель-формирователь, разрешая соответствующую передачу.

Основные достоинства шинных формирователей: большой выходной ток при малом входном токе и отсутствие шума на выходе при переключениях.

Основные электрические параметры микросхемы КР58ОВА86:

- выходное напряжение логического нуля UOL, В:

для А-выводов менее 0,5;

для В-выводов менее 0,5;

- выходное напряжение логической единицы UOH, В:

для А-выводов более 2,4;

для В-выводов более 2,4;

- ток потребления от источника питания IСС, мА менее 135;

- время задержки tIO, мс:

с инвертированием менее 30;

без инвертирования менее 35.

2.4 Системный контроллер и шинный формирователь КР580ВК28

Системный контроллер и шинный формирователь КР580ВК28 предназначен для фиксации слова - состояния микропроцессора, выработки системных управляющих сигналов буферизации шины данных микропроцессора и управления направлением передачи данных.

С

D

(7-0) DB

(7-0)

BF

STSTB

RG MEMR

DBIN MEMW

WR I/OR I/OW PLA

HLDA INTA

UCC

BUSEN GND

Рисунок 8 – Структурная схема шинного формирователя КР580ВК28

В состав шинного формирователя входят: шинный формирователь BF, обеспечивающий увеличение нагрузочной способности системной информационной шины; регистр RG для записи и хранения слова - состояния микропроцессора; комбинационная схема PLA для формирования выходных управляющих сигналов.

По сигналу STSTB, который вырабатывается генератором тактовых импульсов, происходит запись слова - состояния в регистр хранения, а затем выдача его на комбинационную схему, формирующие управляющие сигналы.

Основные электрические параметры микросхемы КР580ВК28:

- выходное напряжение L - уровня UOL, В:

на шине D(7- 0) не менее 0,45;

на всех других выходах не менее 0,45;

- выходное напряжение H - уровня UOH, В:

на шине D(7- 0) не менее 3,6;

на всех других выходах не менее 2,4;

- ток потребления от источника питания IСС, мА не менее 190;

- прямой входной ток Ib мкА:

на входе STSTB не менее 500;

на других выходах не менее 250;

- обратный входной ток Ii мкА:

на входе STSTB не менее 100;

на других выходах не менее 100.

Таблица 4 — Описание выводов шинного формирователя КР580ВК28

|

Обозначение вывода |

Номер контакта |

Назначение вывода |

|

1 |

2 |

3 |

|

D(7-0) |

8; 21; 19;6; 10; 12; 17; 15 |

Выводы /выходы данных со стороны МП |

|

STSTB |

1 |

Строб состояния (от ГТИ) |

|

DBIN |

4 |

Вход сигнала «ПРИЕМ» от МП |

|

WR |

3 |

Вход сигнала «ВЫДАЧА» от МП |

|

HLDA |

2 |

Вход сигнала «ПОТВЕРЖДЕНИЕ ЗАХВАТА» от МП |

|

DB(7-0) |

7;20;18;5; 9;11;16 |

Входы/выходы информационной системной шины |

Продолжение таблицы 4

|

1 |

2 |

3 |

|

MEMR |

24 |

Чтение памяти |

|

MEMW |

26 |

Запись в память |

|

I/OR |

25 |

Чтение с ВУ |

|

I/OW |

27 |

Запись в ВУ |

|

BUSEN |

22 |

Разрешение работы шин - сигнал H - уровня, устанавливающий все входы в высокоимпедансное состояние |

|

INTA |

23 |

Подтверждение прерывания - сигнал L - уровня, используемый для стробирования ввода адреса подпрограммы обслуживания прерывания |

|

Ucc |

28 |

Напряжение питания ( + 5 В) |

|

GND |

14 |

Напряжение питания (0 В) |

2.5 Генератор тактовых импульсов К1810ГФ84

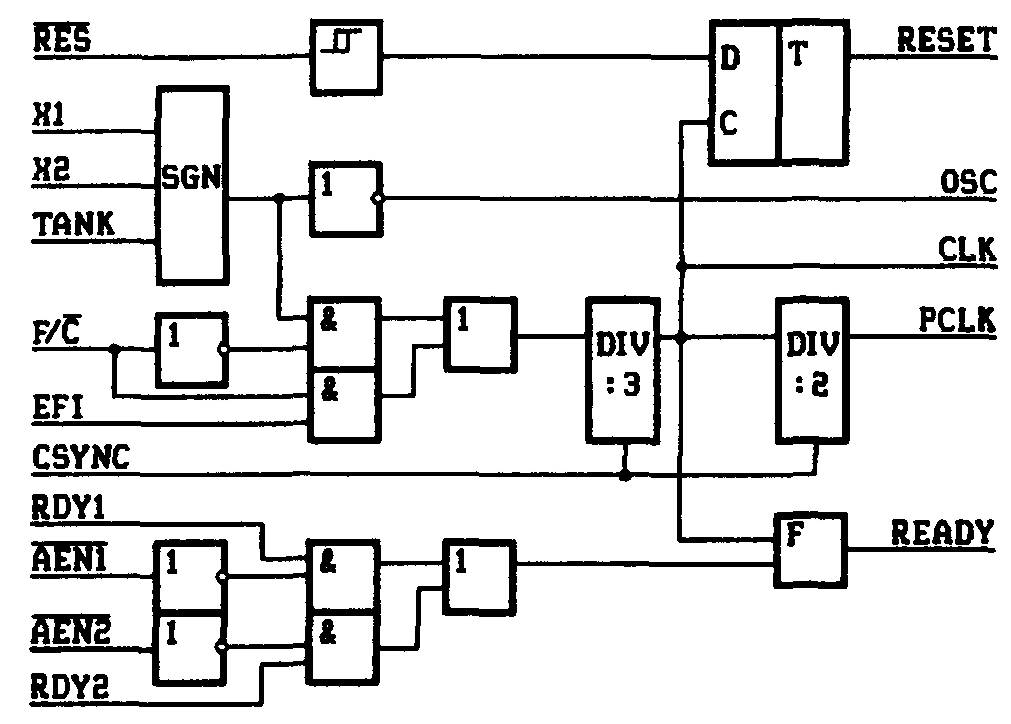

Генератор тактовых импульсов (ГТИ) К1810ГФ84 предназначен для управления ЦП К1810ВМ86 и периферийными устройствами, а также для синхронизации сигналов READY с тактовыми сигналами ЦП и сигналов интерфейсной шины Multibus. Генератор тактовых импульсов включает схемы формирования тактовых импульсов (OSC, CLK, PCLK), сигнала сброса (RESET) и сигнала готовности (READY).

Схема формирования тактовых импульсов вырабатывает сигналы: CLK – тактовой частоты для ЦП К1810ВМ86, PCLK – тактовой частоты для управления периферийными БИС, OSC – тактовой частоты задающего генератора, необходимые для управления устройствами, входящими в систему, и для синхронизации. Сигналы синхронны, их частоты связаны соотношением: FOSC=3Fclk=6Fpclk режиме внутреннего генератора и FEFI=3Fclk=6Fpclk в режиме внешнего генератора.

Сигналы могут формироваться из колебаний основной частоты кварцевого резонатора, подключаемого к входам X1, Х2, или третьей гармоники кварцевого резонатора, выделяемой LC-фильтром или от внешнего генератора, подключаемого к входу EFI.

Рисунок 9 – Структурная схема ГТИ К1810ГФ84

Схема подключения генератора тактовых импульсов к микропроцессору приведена на рисунке 10.

CLK

1

READY

RESET

SYNC

STSTB

CLK

1

READY RESET SYNC

К

контроллеру

КР580ВК28

Рисунок 10 – Подключение генератора тактовых импульсов к

микропроцессору

Выбор режима функционирования определяется потенциалом на входе F/C. Если этот вход подключен к «земле», то ГТИ работает в режиме формирования сигналов от внутреннего генератора (SGN), если на F/C подается высокий потенциал – то в режиме формирования сигналов от внешнего генератора. Схема формирования сигнала сброса RESET имеет на входе триггер Шмидта, а на выходе – триггер, формирующий фронт сигнала RESET по срезу CLK. Обычно ко входу RES подключается RC-цепь, обеспечивающая автоматическое формирование сигнала при включении источника питания.

Входной сигнал READY ЦП К1810ВМ86 используется для подтверждения готовности к обмену. Высокий уровень напряжения на входе указывает на наличие данных на ШД. Схема формирования этого сигнала в ГТИ построена так, чтобы упростить включение системы в интерфейсную шину стандарта Multibus, и имеет две пары идентичных сигналов RDY1, AEN1 и RDY2, AEN2, объединенных схемой ИЛИ. Сигналы RDY формируются элементами, входящими в систему, и свидетельствуют об их готовности к обмену. Сигналы AEN разрешают формирование сигнала READY по сигналам RDY, подтверждая адресацию к адресуемому элементу. Выходной элемент (F) схемы формирует фронт сигнала READY по срезу CLK, чем осуществляется привязка сигнала READY к тактам ЦП.

2.6 Упрощенная структурная схема микропроцессорной системы

Упрощенная структурная схема микропроцессорной системы представлена следующими устройствами: микропроцессор К1810ВМ86, БИС ОЗУ К565РУ6 и БИС ПЗУ К541РЕ1, генератор тактовых импульсов К1810ГФ84, буферный регистр КР580ИР82, шинные формирователи КР580ВА86 и КР580ВК28, программируемый параллельный интерфейс КР580ВВ79, программируемый таймер К1810ВИ54, контроллер прямого доступа к памяти КР580ВТ57, программируемый контроллер прерываний К1810ВН59А, программируемый контроллер клавиатуры и индикации КР580ВВ79.

Основная

память

ГТИ

МП

ОЗУ

ПЗУ

АЦП

Системная

шина

Система

прерываний

Интерфейс

ввода

КПДП

Таймер

Интерфейс

вывода

Импульсы

синхронизации

Устройство

ввода

Устройство

вывода

Запросы

прерываний

Рисунок 11 – Упрощенная схема микропроцессорной системы

3. РАЗРАБОТКА ПОДСИСТЕМЫ ПАМЯТИ

3.1 Оперативное запоминающее устройство К565РУ6

Микросхема КP565PУ6 - микросхема динамического типа. В таких микросхемах функции элемента памяти выполняет электрический конденсатор, образованный внутри МДП - структуры. В таком элементе памяти информация (один бит) представляется в виде заряда (напряжения), наличие заряда в запоминающем конденсаторе соответствует нулю, его отсутствие единице.

В микросхемах динамических ОЗУ для записи и считывания информации используются процессы перезарядки емкостей запоминающих конденсаторов и разрядных шин кратковременными токами через транзисторные усилители запаси считывания. В режиме хранения эти токи не протекают по тому, что, во-первых, емкостные цепи находятся в установившемся режиме и, во-вторых, снимается питание усилителей.

Поэтому для микросхем динамических ОЗУ характерно существенное снижение потребляемой мощности в режиме хранения по сравнению с активным режимом.

В структурную схему входят выполненные в одном кремневом кристалле матрица накопителя, содержащая 16384 элементов памяти, расположенных на пересечениях 128 строк и 128 столбцов, 128 усилителей считывания и регенерации, дешифраторы строк и столбцов, устройство управления, устройство ввода-вывода, мультиплексный регистр адреса.

Матрица накопителя разделена на две части 64 на 64 ЭП в каждой. Между ними размещены усилители, так что каждый столбец состоит из двух секций, подключенных к разным плечам усилителя.

Также матрица имеет опорные элементы. Эти элементы в каждой половине матрицы составляют опорную строку. При каждом обращении к матрице для считывания информации автоматически осуществляется регенерация информации во всех ЭП, принадлежащих выбранной строке. Для адресации 16К элементов памяти необходим 14-разрядный код, а у рассматриваемой микросхемы только семь адресных входов. С целью уменьшения числа необходимых выводов корпуса в динамических ОЗУ код адреса вводят по частям: в начале семя младших разрядов А0 - А6 , сопровождая их стробирующим сигналом RAS, затем семь старших разрядов А7 - А13 , со стробирующим сигналом CAS. В нутрии микросхемы коды адреса строк и столбцов фиксируются на адресном регистре, затем дешифрируются и осуществляют выборку адресуемого ЭП.

Матрица

ЭП

64х64

Опорная

строка 1

Усилители

считывания

Опорная

строка 2

Матрица

ЭП

64х64

Y0

Y127

Ключи

выбора

столбцов

Дешифратор

адреса столбцов Y

X0-X63 1

A6 2

3

F2 4

5 1

A0 6 2

A6

A1

X64-X127

A2 7 3

A3 D0 4

5

A4 6

A5 DI 7

A6

1

2 3 4 5 6 7

F1

F2

F3

F4

F5

Устройство

управления

RAS CAS W/R

Рисунок 12 - Структурная схема микросхемы оперативного запоминающего

устройства КP565PУ6

Для формирования внутренних сигналов F1 и F4, управляющих включением и выключением в определенной последовательности функциональных узлов микросхем, в ее структуре предусмотрено устройство управления, для которого входными являются сигналы RAS ,CAS и W/R.

У

стройство

ввода/вывода обеспечивает вывод одного

бита информацииD0

в режиме считывания и ввод одного бита

информации DI

с ее фиксацией с помощью триггера-защелки

в режиме записи.

стройство

ввода/вывода обеспечивает вывод одного

бита информацииD0

в режиме считывания и ввод одного бита

информации DI

с ее фиксацией с помощью триггера-защелки

в режиме записи.

М икросхема

работает в следующих режимах: записи,

считывания, считывания - модификации -

записиRWM,

слоговой и страничной записи, слогового

и страничного считывания регенерация,

хранение с регенерацией.

икросхема

работает в следующих режимах: записи,

считывания, считывания - модификации -

записиRWM,

слоговой и страничной записи, слогового

и страничного считывания регенерация,

хранение с регенерацией.

В

нешние

сигналы:RAS

-сигнал

выбора адреса строк, СAS

—

сигнал выбора

адреса столбцов, WE

— сигнал

записи/считывания,

а также сигналы, вырабатываемые

схемой управления, обеспечивают

работу ОЗУ в режимах считывания,

записи, постраничного считывания или

постраничной записи, считывания-

модификации-записи, регенерации по

сигналу

RAS.

нешние

сигналы:RAS

-сигнал

выбора адреса строк, СAS

—

сигнал выбора

адреса столбцов, WE

— сигнал

записи/считывания,

а также сигналы, вырабатываемые

схемой управления, обеспечивают

работу ОЗУ в режимах считывания,

записи, постраничного считывания или

постраничной записи, считывания-

модификации-записи, регенерации по

сигналу

RAS.

Рассмотрим названные режимы и условия их реализации.

П

ри

обращении к микросхеме для записи

информации необходимо подать код адреса

строк и одновременно с ним или с некоторой

задержкой сигналRAS,

затем с задержкой на время удержания

адреса строк относительно сигнала RAS

tн(RAS-A)

на эти же выводы поступает код адресов

столбцов и с задержкой на время tн(A-CAS)

подается сигнал CAS.

К моменту подачи кода адреса столбцов

на вход DI

подается записываемый байт информации,

который сигналом WR/RD

при наличии CAS=0

фиксируется на входном триггере -

защелке. Сигнал может быть подан уровнем

или длительностью tw(WR).

Если этот сигнал подан уровнем, то

фиксацию входных данных триггер-защелка

производит по отрицательному перепаду

сигнала CAS

при наличии сигнала RAS

в активном состоянии. По окончании

записи должна быть выдержана пауза

между сигналами RAS

для восстановления состояния внутренних

цепей микросхемы. В режиме считывания

порядок следования адресных и управляющих

сигналов аналогичен рассмотренному,

но при наличии сигнала считывания

WR/RD=1

ри

обращении к микросхеме для записи

информации необходимо подать код адреса

строк и одновременно с ним или с некоторой

задержкой сигналRAS,

затем с задержкой на время удержания

адреса строк относительно сигнала RAS

tн(RAS-A)

на эти же выводы поступает код адресов

столбцов и с задержкой на время tн(A-CAS)

подается сигнал CAS.

К моменту подачи кода адреса столбцов

на вход DI

подается записываемый байт информации,

который сигналом WR/RD

при наличии CAS=0

фиксируется на входном триггере -

защелке. Сигнал может быть подан уровнем

или длительностью tw(WR).

Если этот сигнал подан уровнем, то

фиксацию входных данных триггер-защелка

производит по отрицательному перепаду

сигнала CAS

при наличии сигнала RAS

в активном состоянии. По окончании

записи должна быть выдержана пауза

между сигналами RAS

для восстановления состояния внутренних

цепей микросхемы. В режиме считывания

порядок следования адресных и управляющих

сигналов аналогичен рассмотренному,

но при наличии сигнала считывания

WR/RD=1

Д ля

оценки быстродействия микросхемы

памяти в расчет необходимо принимать

время цикла записи (считывания). Микросхемы

динамического ОЗУ характеризуются

набором временных параметров,

регламентирующих длительности импульсных

сигналов, интервалы между ними. Взаимный

сдвиг во времени. Для обеспечения

надежного сохранения записанной в

накопителе информации предусмотрен

режим принудительной регенерации,

которой подвергается каждый элемент

памяти в интервале времени. Регенерация

выполняется автоматически для всех

элементов памяти выбранной строки при

каждом обращении к накопителю для записи

или считывания информации.

ля

оценки быстродействия микросхемы

памяти в расчет необходимо принимать

время цикла записи (считывания). Микросхемы

динамического ОЗУ характеризуются

набором временных параметров,

регламентирующих длительности импульсных

сигналов, интервалы между ними. Взаимный

сдвиг во времени. Для обеспечения

надежного сохранения записанной в

накопителе информации предусмотрен

режим принудительной регенерации,

которой подвергается каждый элемент

памяти в интервале времени. Регенерация

выполняется автоматически для всех

элементов памяти выбранной строки при

каждом обращении к накопителю для записи

или считывания информации.

Микросхема КP565PУ6 отличается от других микросхем тем, что обладает более высокое быстродействие, требует для работы один источник питания напряжением 5В. При эксплуатации микросхем необходимо помнить, что после подачи напряжения питания БИС ОЗУ переходит в нормальный режим функционирования через 2,0 мс и требует проведения затем 16 рабочих циклов регенерации.

А

RAM

0

16K 1 2 3

D0 4 5 6 DI

RAS

UCC CAS WE

GND

5

7

6 12 14

11

10 13

2

4 15 8

3 16

Рисунок 13 – Условное графическое обозначение выводов микросхемы

К565РУ6

Основные электрические и временные параметры БИС КР565РУ6 при температуре 25±100С :

- напряжение питания, В от 4,5 до 5,5;

- ток потребления, мА:

динамический менее 45(27);

хранения менее 3,2;

- входное напряжение, В:

высокого уровня от 2,4 до 6,0;

низкого уровня от минус 1,0 до плюс 0,8;

- ток утечки на входах А0 – А7, WE, RAS, GAS, мкА менее 5;

- ток утечки на информационном входе, мкА менее 5;

- выходное напряжение, В:

высокого уровня более 2,4;

низкого уровня менее 0,4.

3.2 Постоянное запоминающее устройство К541РЕ1

Масочные ПЗУ серии К541. Микросхема ПЗУ типа К541РЕ1 представляет собой постоянное ЗУ с емкостью 16 384 бит для хранения и считывания информации в объеме 2048 8-разрядных слов.

Входные и выходные уровни напряжений совместимы с ТТЛ ИС. Микросхема К541РЕ1 имеет выходы с открытым коллектором. Программирование ПЗУ осуществляется с помощью фотошаблона технологического слоя «диэлектрик». Накопитель представляет собой набор диэлектрических окон с развязывающими элементами. Наличие и отсутствие этих окон определяют хранимую информацию в накопителе.

Условное обозначение и назначение выводов приведены на рисунке 14.

Микросхемы серии имеют напряжение питания 5 В, ТТЛ входные и выходные уровни, выход на три состояния, характеризуются сравнительно высоким уровнем энергопотребления, по сравнению с микросхемами серии К132, причем не обладают свойством снижать уровень потребляемой мощности и режиме хранения.

Основные электрические параметры БИС К541РЕ1 в диапазоне температур от -10 до +70°С при Uсс = (5±0,5) В:

Ток потребления в статическом режиме Icc, мА не более 100.

Выходное напряжение низкого уровня UOL при IOL= 8 мА, В не более 0.45.

Ток утечки на выходе IOH, мкА не более 40.

Входное напряжение низкого уровня UIL при IIL = 0.4 мА, В не более 0,5.

Входное напряжение высокого уровня UIH при IIH = 40 мкА, В не менее 2,4.

Время выбора адреса tAA, не не более 100;

выборки разрешения tCS, не не менее 70;

восстановления tOFF, не не более 70;

цикла tC, не не менее 150.

Входная емкость С1, пФ не более 3.

Выходная емкость Со, пФ не более 6.

Емкость нагрузки CL, пФ не более 200.

A

PROM

0

16k

D0

1

1 2

2 3

3 4

4 5

5 6

6 7

7

8

8

9

10

UCC

CS1 CS2

GND CS3

8

7 9

6 10

5 4 11 13

3 2 14 15

1 16

23

22 17

21 24

20

19 12

18

Рисунок 14 - Условное графическое обозначение выводов микросхемы

К541РЕ1

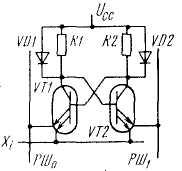

Структура микросхем содержит все функциональные узлы типичного варианта ее построения рисунок 15. В качестве элемента памяти использован статический триггер на четырех транзисторах, два из которых, VT3 и VТ4, являются инжекторами транзисторов VT2 и VT1 соответственно. Двухэмиттерными транзисторами управляют сигналы адресной шины Xi и разрядных шин РШ0, РШ1. При Хi=0 триггер находится в режиме хранения, так как при этом фиксируется состояние плеч триггера. При Xi = 1 оба эмиттерных перехода, подключенных к адресной шине, закрываются, и состояние триггера зависит от потенциалов разрядных шин: при низком потенциале шин в режиме считывания в одну из них потечет ток, а именно в ту, со стороны которой транзистор открыт; в другой тока не будет.

Рисунок 15 – Функциональные элементы микросхем статических ОЗУ на

биполярных транзисторах, элемент памяти ТТЛ

При записи но шинам в форме парафазного сигнала РШ1=D, РШ0=D к плечам триггера подводится информации. Асимметрия и потенциалах шин вызовет переключение триггер в состояние, определяемое потенциалами шин: например, при РШ1=O, РШ0=1 (запись 0) откроется VT2, через него в шипу потечет ток инжектора VT4, а транзистор VT1 закроется. При записи 1 состояния транзисторов изменятся па обратные.

Схема подключения ОЗУ и ПЗУ к магистралям показана на рисунке 16.