Лекция 3

.pdfСложные программируемые логические устройства

Структура сложных программируемых логических устройств или CPLD

CPLD (Complex Programmable Logic Devices) – микросхемы высокого уровня ин-

теграции, основными частями которых являются:

PAL (GAL) — подобные функциональные блоки;

система коммутации, выполненная в виде матрицы соединений, по-

зволяющая объединять функциональные блоки в единое устройство;

блоки ввода/вывода.

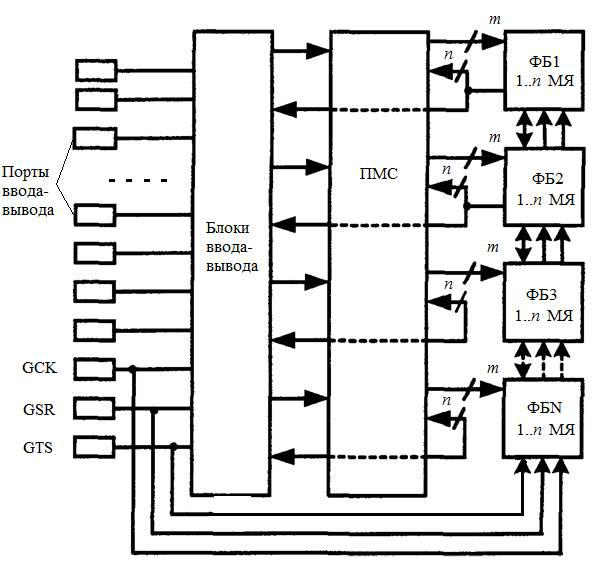

Все составные части CPLD программируются. Обобщенная структура CPLD

показана на рис. 1. В структурной схеме приняты следующие обозначения. Через ФБ (FB) обозначены функциональные блоки, число которых N зависит от уровня интеграции микросхемы и изменяется в довольно широких пределах. В каждом ФБ имеется n макроячеек МЯ (МС, Macro Cells). Функциональные блоки полу-

чают входные сигналы от программируемой матрицы соединений ПМС (PIA, Programmable Interconnect Array). Число таких сигналов m. Выходные сигналы ФБ поступают как в ПМС, так и в блоки ввода/вывода CPLD (IOBs, Input/Output Blocks). ПМС обеспечивает полную коммутируемость функциональных блоков,

т. е. возможность подавать сигналы с любого их выхода на любой вход.

Блоки ввода/вывода связаны с внешними двунаправленными портами ввода-вывода, которые, в зависимости от задания при программировании, могут быть использованы как входы или как выходы. Три нижних вывода могут ис-

пользоваться как для подачи на матрицу функциональных блоков сигналов GCK (Global Clocks) глобального тактирования, сигналов GSR (Global Set/Reset) об-

щего для всей схемы сигнала установки/сброса и сигналов GTS (Global Threestate Control) управления третьим состоянием выходных буферов, так и для обычного ввода/вывода. Число портов ввода/вывода может совпадать с числом выходов всех ФБ, но чаще всего, меньшим. В последнем случае часть макрояче-

ек может быть использована только для выработки внутренних сигналов устрой-

ства (например, сигналов обратной связи).

1

Рис.1 – Обобщенная структура CPLD

Структура на рис. 1 несколько упрощена. Кроме показанных блоков в

CPLD могут присутствовать контроллеры для управления операциями програм-

мирования непосредственно в системе (ISP, In System Programmability), контрол-

леры для работы с интерфейсом JTAG и др.

Программируемая матрица соединений

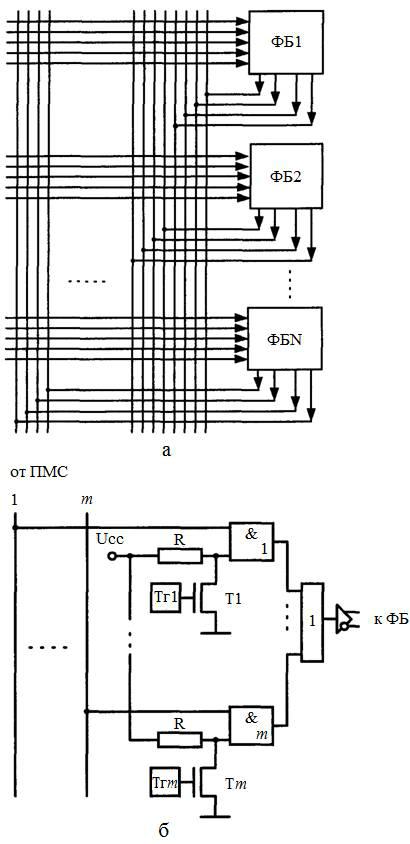

В программируемой матрице соединений ПМС (рис. 2, а) выходы функ-

циональных блоков ФБ подключаются к вертикальным непрерывным (несегмен-

тированным) линиям, причем каждому выходу соответствует своя линия. Входы ФБ связаны с горизонтальными линиями, пересекающими все вертикальные ли-

нии. На пересечениях горизонтальных и вертикальных линий имеются програм-

мируемые точки связи, так что любой вход ФБ может быть подключен к любому

2

выходу. Достоинством ПМС рассмотренного типа является малая и предсказуе-

мая задержка коммутируемых сигналов. Если передача сигналов из ПМС в ФБ организована так, как показано на рис. 2 б, то для каждого соединения образует-

ся идентичный всем другим канал связи с малым числом программируемых ключей или даже их отсутствием.

Таким образом, задавая i-ому триггеру состояние логического нуля, а ос-

тальным триггерам состояние логической единицы, можно обеспечить закрытое состояние транзистора Тi, и открытое состояние всех других транзисторов, что означает подключение выхода ФБ к i-ой вертикальной линии ПМС с образова-

нием так называемого непрерывного соединения. Замкнутые транзисторные ключи имеют, в первом приближении, схему замещения в виде инерционной RC -цепи и вносят основные задержки в процесс распространения сигнала. Про-

граммируемые матрицы соединений, такие, как показаны на рис. 2 а, эффектив-

ны в схемах с относительно небольшим числом коммутируемых блоков. При большом их числе, характерном, например, для FPGA, подобные ПМС были бы чрезмерно сложны, поскольку любое соединение образуется с помощью линий связи, проходящих по всей длине и ширине схемы, тогда как очень многие связи локальны и соединяют близлежащие блоки. Поэтому, например, в ПЛИС типа

FPGA системы коммутации строятся иначе — с помощью сегментированных линий связи.

3

Рис. 2 – Схема программируемой матрицы соединений CPLD (а) и схема переда-

чи сигналов из этой матрицы в функциональный блок (б)

4

Функциональные блоки CPLD

Функциональные блоки CPLD различных фирм-изготовителей и разной сложно-

сти принципиально мало отличаются друг от друга по своей архитектуре и со-

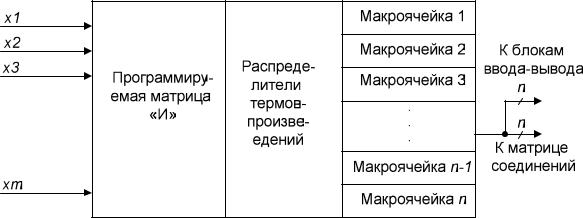

ставу элементов. Обобщенная структура функционального блока CPLD пред-

ставлена на рисунке 3[3].

Рис. 3 – Структура функционального блока CPLD

Основными частями функциональных блоков являются программируемая матрица элементов «И», матрица распределителей термов и группа из n макро-

ячеек. По существу, каждый ФБ представляет собой PAL-подобную структуру с несколькими отличиями от простых PLD. Как и в классических PLD в блоке имеется многовходовая программируемая матрица «И», вырабатывающая конъ-

юнктивные термы для использования их в последующих частях блока. Термы жестко распределяются между конъюнкторами, формирующими выходные функции в форме ДНФ. Совокупность дизъюнкторов образует жёсткую (не про-

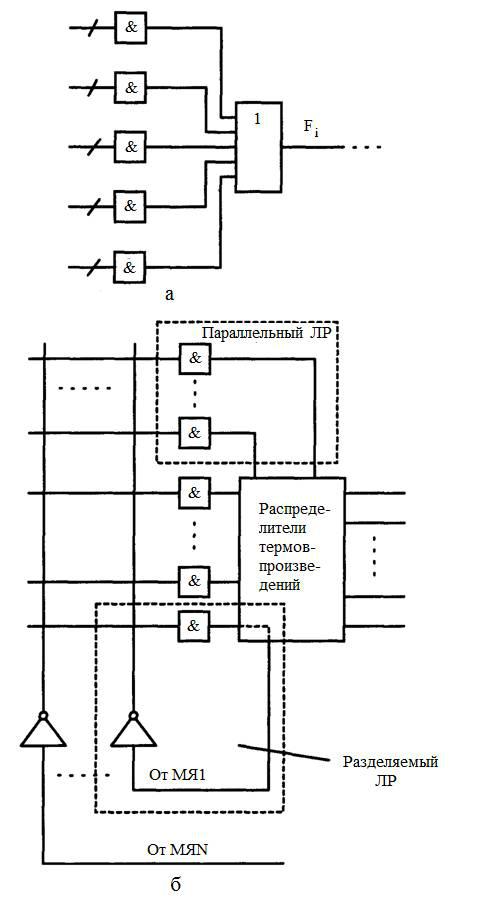

граммируемую) матрицу элементов «ИЛИ». На рис. 4,а показан один из дизъ-

юнкторов (для канала i), вырабатывающий функцию, в которую может входить не более 5 термов. В CPLD матрица элементов «ИЛИ» чаще всего не является полностью фиксированной, и благодаря введению в схему распределения тер-

мов, возможно варьирование числа термов в вырабатываемой функции Fi. При этом термы заимствуются у других каналов выработки функций или отдаются им. Проще всего организовать коммутацию термов между соседними каналами.

Через соседние каналы путем образования цепочечных связей можно собирать в одном канале много термов (в пределах одного функционального блока).

5

Рис.4 – Схема выработки ДНФ логической функции в простейшем варианте

CPLD (а),логические расширители параллельного и последовательного типов (б)

6

Схемотехнически в операциях распределения термов по каналам ФБ за-

действованы как непосредственно цепи коммутации между входами и выходами распределителей термов, так и логические расширители (ЛР) последовательного и параллельного типов. Последовательные (разделяемые, общие) ЛР создаются подачей инвертированного значения терма из распределителя термов данного канала обратно на один из входов программируемой матрицы «И» (рис. 4, б).

Переданный в программируемую матрицу «И» терм становится доступным для использования во всех каналах данного ФБ. Если, например, этот терм запро-

граммирован как q = x1!x2x5!x10, т. е. его инверсия есть !q = !(xl!x2x5!x10) = !xlvx2v!x5vx10, то в том канале, где он будет использован вместе с входными термами канала, например, q1, q2, q3, будет получена функция:

F= qlvq2vq3v!xlvx2v!x3vx10 = q1vq2vq3v!(xl!x2x5!x10).

Параллельный расширитель позволяет передавать термы одного канала другому.

Способность принимать в свой канал термы от соседнего канала обычно означа-

ет и возможность приема через него термов и более далеких каналов с образова-

нием цепочки для сбора термов от нескольких каналов (например, в пределах целого функционального блока). Можно, естественно, и отдавать собственные термы или их часть другим каналам (в частности, соседним, а через них и более далеким). Термы от распределителей термов поступают далее на часть ФБ, на-

зываемую макроячейкой (МЯ). Макроячейка содержит в качестве основы про-

граммируемые мультиплексоры, триггер (или несколько) и формирует группу выходных сигналов ФБ в нескольких их вариантах. На рис. 5 раскрыта схема од-

ной из идентичных макроячеек ФБ. Прообразом показанной схемы является макроячейка CPLD XC9500 фирмы Xilinx, не имеющая разделяемого (общего)

логического расширителя[1].

7

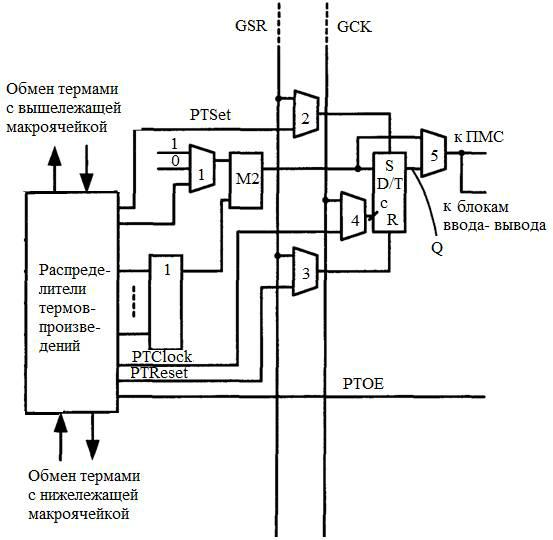

Рис.5 – Пример схемы макроячейки функционального блока CPLD

Программируемость мультиплексоров в этой схеме и всех дальнейших не отображается, т. к. она присуща всем имеющимся в схеме мультиплексорам, ес-

ли не оговорено противоположное. В зависимости от программирования каждый мультиплексор передает на выход сигнал с того или иного входа. Триггер может программироваться на режимы работы триггера типа D или Т. Заметим, кстати,

что при описании микросхем программируемой логики триггеры в иностранной литературе чаще всего называют регистрами. Триггеры тактируются положи-

тельными фронтами синхросигналов и имеют входы установки S и сброса R.

Выходные сигналы ФБ передаются в ПМС и в блоки ввода/вывода БВВ.

Аргументы х1,.., хm реализуемой макроячейкой функции поступают на матрицу «И» из ПМС. Аргументами для МЯ могут быть как входные сигналы,

поступающие извне через БВВ, так и сигналы обратных связей, подаваемые в

матрицу «И» с выходов макроячеек. На рис. 5 входные сигналы матрицы незави- 8

симо от их характера обозначены через x1, ..., хm. Входные буферы преобразуют сигналы в парафазные, представляя каждый сигнал его прямым и инверсным значениями, так что в матрице имеется 2m вертикальных линий и образующие ее конъюнкторы имеют по m входов. Пять термов из матрицы «И» поступают на элемент «ИЛИ» для образования логической функции. Для управления тригге-

ром и буферами блока ввода/вывода вырабатываются также термы PTSet, PTClock, PTReset, которые могут быть использованы как сигналы установки,

синхронизации и сброса триггера. Терм РТОЕ — программируемый терм управ-

ления третьим состоянием буфера БВВ (ОЕ, Output Enable). Всего в матрице «И» на рис. 5 программируются 9n термов.

На выходе элемента «ИЛИ» вырабатывается логическая функция в форме ДНФ ранга не более m. Ее значение передается дальше через элемент сложения по мо-

дулю 2, на второй вход которого, в зависимости от программирования мультип-

лексора 1, может быть подан логический нуль, логическая единица или терм РТ1. В первом случае функция передается без изменений (F= F*), во втором ин-

вертируется (F= !F*), в третьем передается в прямом виде во всех ситуациях за исключением такой, в которой РТ1 = 1.

Мультиплексор MUX5 программируется для передачи на выход МЯ либо непо-

средственно значения функции F (комбинационный выход), либо состояния триггера (регистровый выход). Характер тактирования триггера определяется программированием мультиплексора MUX4, при этом возможно использование глобального синхросигнала (GCK, Global Clock) или сигнала, порождаемого термом PTClock. Асинхронные установка и сброс триггера производятся либо глобальным сигналом (GSR, Global Set/Reset), либо термами PTSet и PTReset,

что определяется программированием мультиплексоров MUX2 и MUX3. Сам триггер программируется на режимы D-триггера-защелки или Т-триггера -

счетного. Основной выходной сигнал макроячейки поступает как в ПМС, кото-

рая может направлять его по любому требуемому маршруту, так и в блоки вво-

да/вывода.

9

Блоки ввода/вывода CPLD

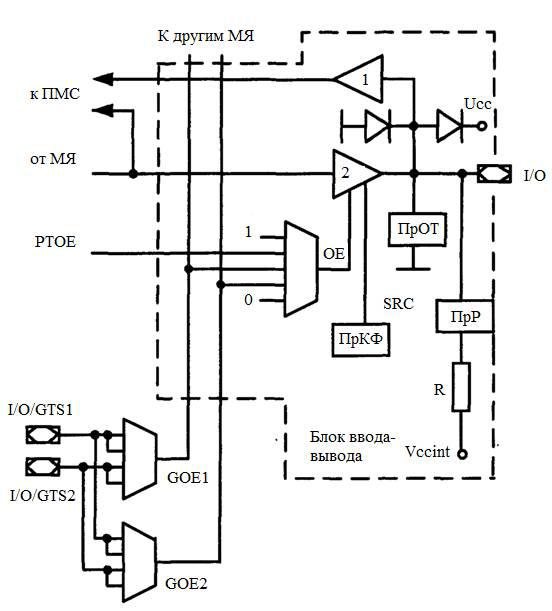

Блоки ввода/вывода соединяют внешние контакты микросхемы с ее внут-

ренними цепями. Характерным примером такого блока может служить БВВ

CPLD типа ХС9500 фирмы Xilinx, показанный на рис. 6. Основой БВВ служат два буфера — входной (1) и выходной (2). Чтобы обеспечить постоянство уров-

ней напряжения, поступающих на входной буфер, и их независимость от ампли-

туды входных сигналов, в схеме вырабатывается внутреннее напряжение пита-

ния Vccint. Схема программируемой общей точки ПрОТ позволяет пользователю при необходимости получать дополнительный «заземленный» вывод, что позво-

ляет снизить уровень помех в микросхеме[2].

Рис. 6 – Пример схемы блока ввода/вывода CPLD

10