Metod_B1.V.DV.05.02_09.03.01_04.06.2016_pr

.PDF

D |

TT |

D |

TT |

C |

1 |

C |

2 |

С «Сдвиг»

Рис.5.1

С целью устранения гонок и неустойчивых состояний используются двухступенчатые D-триггера (рис. 5.2):

D |

T |

S |

T |

C |

|

C |

|

|

R |

|

С |

1 |

|

Рис. 5.2

Q Q

Аналогично строится и n-разрядный регистр сдвига, который содержит n последовательно соединенных D-триггеров, причем вход первого триггера является входом регистра.

По приведенной методике можно построить регистр сдвига информации влево или вправо и на другой элементной базе, например на RS

или JK триггерах. Заметим, что в случае сдвига информации, хранящейся в регистре, и отсутствии входного сигнала, в освобождающиеся разряды регистра вводятся нули. Например, регистр сдвига вправо на один разряд на синхронных JK триггерах имеет вид (рис. 5.3). Если в такой регистр занести число в параллельном коде, а потом осуществлять сдвиг этого числа вправо

на один разряд, то число, первоначально представленное в параллельном коде, будет преобразовано в последовательный код.

1 С

J |

TT |

J |

TT |

J |

TT |

& |

C |

|

C |

|

C |

|

|

K |

1 |

K |

2 |

K |

n |

|

«Сдвиг»

Рис. 5.3

После n сдвигов в регистр будет находиться код нуля. Если схему регистра дополнить схемой ввода информации, то такой регистр может осуществить преобразования числа из последовательного кода в параллельный (рис.5.4):

|

J |

TT |

J |

TT |

J |

|

C |

|

C |

|

C |

1 |

K |

1 |

K |

2 |

K |

С «Сдвиг»

TT |

& |

n |

Разряды |

|

|

|

выводимого |

|

числа |

Рис. 5.4

Заполнение регистра в этом случае будет происходить в течение n

тактов, после чего число, находящееся в регистре, может быть прочитано в параллельном коде. Цепи ввода и вывода числа в такой регистр в параллельном коде, такие же, как и у параллельного регистра. Регистр сдвига на функциональных схемах обозначается следующим образом (рис. 5.5):

C |

RG |

V |

|

D1 |

1 |

D2 |

2 |

D4 |

4 |

D8 |

8 |

Рис. 5.5

Для указания направления сдвига используется стрелка: сдвиг в сторону старших разрядов, сдвиг в сторону младших разрядов.

Синтез счетчиков

Синтезировать 3-х разрядный счетчик с коэффициентом пересчета Кст = 2n = 8. Синтез такого счетчика можно провести на основании кодированной таблицы переходов трехразрядного счетчика и таблицы функций возбуждения:

На основании этой таблицы построим диаграммы Вейча для сигналов возбуждения триггеров, рассматривая их как функции состояний триггеров

Q1(t), Q2(t), Q3(t). При =1. Имеем:

Из диаграмм получаем следующие выражения для сигналов возбуждения триггеров T1= ; T2=Q1 ; T3= Q1Q2 . Если бы мы синтезировали n-

разрядный счетчик, то получили бы следующие выражения для сигналов возбуждения триггеров:

T1= ; T2=Q1 ; T3=Q1Q2 ; T4=Q1Q2Q3 ; … Tn=Q1Q2Q3…Qn-1

Счетчик, построенный в соответствии с этими уравнениями носит название счетчика с одновременным или параллельным переносом.

Т.к. во всех функциях возбуждения присутствует входной сигнал , то такой счетчик целесообразно строить на синхронных Т-триггерах, подавая счетные сигналы на входы синхронизации всех триггеров. В результате получаем следующую схему (рис. 5.6):

|

|

Q |

|

|

Q |

|

|

|

Q |

|

|

|

Q |

T |

TT |

1 |

T |

TT |

2 |

|

T |

TT |

3 |

T |

TT |

4 |

|

|

|

|

|

|

|||||||||

C |

|

|

C |

|

|

|

C |

|

|

C |

|

|

|

α |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

& |

Q |

Q |

|

& |

Q |

Q Q |

|

|

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

1 |

2 |

|

|

|

|||

|

|

|

|

|

|

|

|

|

|

1 |

2 |

3 |

|

Рис. 5.6

Синтез счетчиков с коэффициентом пересчета k 2n.

Для многих устройств ЭВМ необходимы счетчики с k 2n. Такие счетчики называют еще пересчетными схемами.

Синтезируем счетчик с коэффициентом пересчета равным 5 (на Т-

триггерах). Такой счетчик имеет пять состояний (от 0 до 4). Количество триггеров определяется согласно формуле  , где k=5 – число состояний. Отсюда

, где k=5 – число состояний. Отсюда  . Выходной сигнал Z=1 должен формироваться на каждый пятый входной сигнал. В результате получается кодированная таблица переходов, выходов и сигналов возбуждения.

. Выходной сигнал Z=1 должен формироваться на каждый пятый входной сигнал. В результате получается кодированная таблица переходов, выходов и сигналов возбуждения.

При =1 строим следующие диаграммы Вейча

Из диаграмм Вейча получаем следующие выражения для трех функций возбуждения и функции выходов:

Это синхронный пятеричный счетчик (рис. 5.7):

|

Q1 |

|

|

Q |

2 |

& |

1 |

|

Q3 |

& |

Z = α Q3 |

T |

TT |

T |

TT |

|

|

T |

TT |

|

|||

|

|

|

|

|

|||||||

C |

1 |

C |

2 |

|

|

|

|

C |

3 |

|

|

α

Рис. 5.7

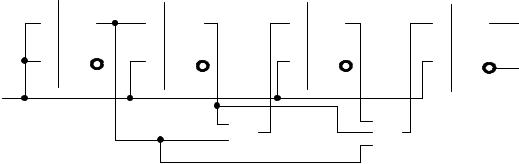

Занятие 6. Синтез сумматоров. Синтез одноразрядного

двоичного сумматора.

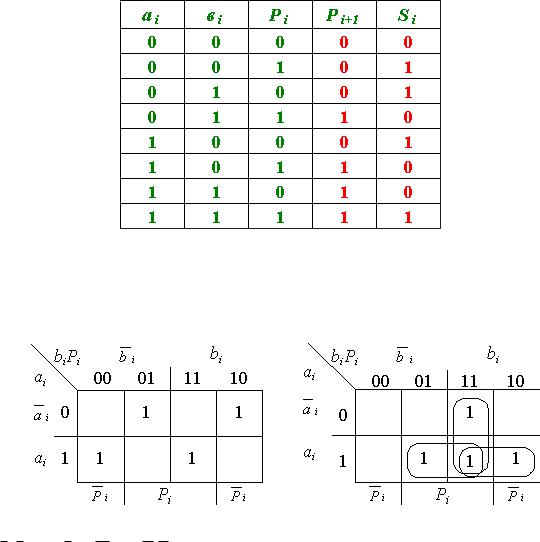

Закон функционирования такого сумматора при сложении трех цифр определяется следующей таблицей.

На основании таблицы строятся диаграммы Вейча и получаются минимальные ДНФ функций Si и Pi+1

si ai bi pi ai bi pi ai bi pi ai bi рi ,

pi 1

aibi

a |

p |

i |

i |

|

b p |

i |

i |

.

По полученным уравнениям можно построить двухуровневую схему одноразрядного комбинационного сумматора (рис. 6.1).

ai

bi & p i

ai

bi & p i

ai & bi

p i

ai

bi & p i

1 |

|

Si |

|

|

|

|

|

|

|

|

|

b |

i |

& |

|

|

|

|

|

||

pi |

|

|

|

|

a |

i |

& |

1 |

P |

|

||||

pi |

|

|

i+1 |

|

|

|

|

||

a |

i |

& |

|

|

|

|

|

||

bi |

|

|

|

|

Рис. 6.1

Полученную схему можно упростить, если рассматривать Si как функцию 4-х переменных Si=Si(аi,вi,Pi,Pi+1).

Отсюда имеем:

s |

(a |

|

||

|

i |

|

i |

|

p |

i 1 |

а |

i |

|

|

|

|||

bi bi

(a

p )р |

||

|

i |

i 1 |

i |

b ) р |

|

|

i |

|

a b p |

||

i |

i |

i |

i . |

|

|

Схема сумматора:

& |

1 |

||

|

|

|

|

|

|

|

|

1 |

|

& |

|

) |

|

||||

|

|

|

||

|

|

1 |

|

|

|

|

|

&

1

&

1

Рис. 6.2

Одноразрядный накапливающий сумматор

Одноразрядным сумматором накапливающего типа является схема,

суммирующая поочередно поступающие на ее вход цифры слагаемого и переноса с запоминанием результата суммирования. Для запоминания результата сложения на выходе рассмотренных комбинационных сумматоров можно установить триггеры (триггера R-S и D-типов). Совместно с триггером комбинационный сумматор будет выполнять функции накапливающего сумматора. Роль накапливающего сумматора может выполнять и счетный триггер со схемой формирования переноса, на счетный вход которого все слагаемые должны подаваться последовательно во времени. В этом случае суммирование трех слагаемых будет проходить за 3 такта (рис. 6.3):

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

S |

i |

(t |

3 |

) |

||

|

|

|

|

|

|

|

|

Уст «0» |

|

|

|

|

|

|

|

|

|

|||||

|

|

|

|

|

|

|

|

|

R |

T |

|

1 |

P |

|

(t |

|

|

) |

||||

|

|

|

|

|

|

|

|

|

|

|

|

& |

i |

3 |

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||

a |

i |

(t |

|

|

) |

|

|

|

|

|

|

2 |

2 |

|

|

|

|

|||||

1 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

b |

(t |

) |

|

1 |

|

|

|

|

|

|

|

|

|

|

|

|

||||||

i |

2 |

|

|

T |

|

|

|

|

|

|

|

|

|

|

||||||||

|

1 |

|

|

& |

|

|

|

|

|

|

|

|

||||||||||

P |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||||||||

|

(t |

3 |

) |

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

||||

i |

|

|

|

|

b |

i |

(t |

|

) |

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

||

Рис. 6.3

Рассмотрим работу устройства. В первый момент времени t1 через схему ИЛИ1 на вход Т-триггера, который был предварительно установлен в нулевое состояние, поступает цифра ai и запоминается. После завершения переходных процессов в триггере в момент времени t2 через схему ИЛИ1

поступает |

цифра |

вi |

|

второго слагаемого. При этом Т-триггер реализует |

||||

функцию |

f |

à b a b a |

i |

b |

через |

|||

1 |

i |

i |

i |

i |

i . Наконец в следующий момент времени t3 |

|||

схему ИЛИ1 подается цифра переноса из более младшего разряда рi и триггер реализует функцию:

f |

2 |

|

|

|

f |

p (a b a |

i |

b )p |

a bi aib p |

|||

1 |

i |

i i |

i |

i |

i |

i i |

|

a bi p |

i |

i |

aib p |

i |

i |

ai bi pi

aibi pi

,

которая совпадает с функцией si, полученной ранее по таблице истинности одноразрядного сумматора. Таким образом по истечении трех тактов в триггере будет находится значение i-го разряда суммы слагаемых А и В, т.е. si. Сигнал переноса pi+1 формируется комбинационной схемой, стоящей на выходе триггера. В момент времени t3, когда триггер еще находится в состоянии f1, приходит сигнал рi. На выходе И1 имеем:

f |

3 |

f |

p a bi p aib p . |

||||

|

1 |

i |

i |

i |

i |

i |

|

Если |

теперь |

к |

f3 |

добавить через дизъюнкцию aibi, то получится рi+1. |

|||

Непосредственно aibi получить с помощью конъюнктора нельзя, т.к. они

поступают в |

различные дискретные |

моменты |

времени. Поэтому aibi |

формируются |

с помощью элемента |

И2, |

реализующего функцию |

f4 f 1bi ai bi aibibi aibi .

Окончательно сигнал переноса pi+1 на выходе ИЛИ2 равен:

f |

3 |

f p a b p a b p ab ab a p b p |

||||||

|

1 i |

i i i |

i i i |

i i |

i i |

i i |

i i . |

|

Этот сигнал совпадает с переносом, формируемом в комбинационном сумматоре на выходе рi+1 .

Недостаток рассмотренного сумматора заключается в том, что он имеет малое быстродействие, поскольку в каждом цикле суммирования число

срабатываний триггера может равняться четырем: Уст «0», ai(t1), bi(t2) и

рi(t3).

Достоинство накапливающего сумматора по сравнению с комбинационным состоит в более простой организации суммирования с накоплением результата. Полученная сумма сохраняется в сумматоре и после снятия входных сигналов.

Многоразрядные сумматоры

В зависимости от того, каким образом в ЭВМ передаются числа, может быть два способа сложения: последовательный и параллельный. При последовательном способе сложения при передаче каждого слагаемого используется один канал, по которому код числа передается в виде временной последовательности цифр разряд за разрядом. Если для передачи каждого разряда числа предусмотрен отдельный канал, то применяется параллельный способ сложения.

Последовательный сумматор

Последовательный сумматор должен преобразовывать последовательные коды слагаемых в последовательный код суммы этих слагаемых. Такие сумматоры обычно строятся на основе одноразрядного комбинационного сумматора, в котором для запоминания сигнала переноса используется D-триггер (рис. 6.4).

При последовательном суммировании разряды ai и bi слагаемых А и В,

начиная с младших, поступают на входы одноразрядного комбинационного сумматора SM с выходов сдвигающих регистров. Значения разрядов суммы Si

заносятся в освобождающиеся разряды одного из сдвигающих регистров. На вход pi сумматора SM поступает сигнал переноса, который был получен в предыдущем такте при суммировании ai-1, bi-1 и Pi-1. Для запоминания сигнала переноса используется D-триггер. Очевидно, для сложения m разрядных чисел А и В используется m+1 такт (в последнем (m+1)-ом такте перенос из