лаба3узлы6вар

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №3

по дисциплине «Узлы и устройства средств вычислительной техники»

Тема: ПРОЕКТИРОВАНИЕ ТИПОВОГО КОМБИНАЦИОННОГО УЗЛА

Вариант 6

|

Студенты гр. |

|

|

|

|

|

|

|

|

|

|

|

Преподаватель |

|

|

Санкт-Петербург

2019

-

Подготовка к работе

Составим схему одноразрядного сумматора и на его основе каскадно соберем двухразрядный сумматор

Pi-1 – входной бит переноса младшего разряда

ai, bi – слагаемые

Si – бит суммы

Pi – выходной бит переноса в старший разряд

|

Pi-1 |

ai |

bi |

Si |

Pi |

|

0 |

0 |

0 |

0 |

0 |

|

0 |

0 |

1 |

1 |

0 |

|

0 |

1 |

0 |

1 |

0 |

|

0 |

1 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

0 |

|

1 |

0 |

1 |

0 |

1 |

|

1 |

1 |

0 |

0 |

1 |

|

1 |

1 |

1 |

1 |

1 |

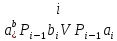

Получим логические функции выходов для бита суммы и бита переноса

|

aibi |

00 |

01 |

11 |

10 |

|||

|

Pi-1 |

0 |

0 |

1 |

0 |

1 |

||

|

1 |

1 |

0 |

1 |

0 |

|||

Si

=

– бит суммы

– бит суммы

|

aibi |

00 |

01 |

11 |

10 |

|||

|

Pi-1 |

0 |

0 |

0 |

1 |

0 |

||

|

1 |

0 |

1 |

1 |

1 |

|||

Pi

=

– бит переноса

– бит переноса

-

Реализация функциональной схемы в Quartus II

Рис.1 Входные сигналы

a0, b0 – младший и старший разряды первого слагаемого

a1, b1 – младший и старший разряды второго слагаемого

P0 – бит переноса из младших разрядов

Рис. 2 Младший каскад сумматора

S0 – младший бит выхода

P1 – бит переноса в старший каскад сумматора

Рис.3 Старший каскад сумматора

S1 – старший бит выхода

P2 – выходной бит переноса

-

Функциональное и временное моделирование проекта

Рис.4 Функциональное моделирование

Рис.5 Временное моделирование

-

Список и назначение внешних контактов, описание процесса макетирования

Рис.6. Распиновка

Для входных сигналов использовались контакты движковых переключателей с номерами 170,169,168,161,162

Для выходных сигналов использовались диоды светодиодной линейки с номерами контактов 171, 173 и 175.

Рис.5. Окно “Programmer” после завершения программирования микросхемы

Выводы по работе

В ходе выполнения лабораторной работы была реализована функция полного двух разрядного комбинационного сумматора на базе каскадного подключения схем одноразрядного сумматора.