лаба5узлы6вар

.docxМИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра Вычислительной техники

отчет

по лабораторной работе №5

по дисциплине «Узлы и устройства средств вычислительной техники»

Тема: "ИССЛЕДОВАНИЕ РЕГИСТРОВ"

|

Студент гр. |

|

|

Преподаватель |

|

Санкт-Петербург

2019

-

Часть

-

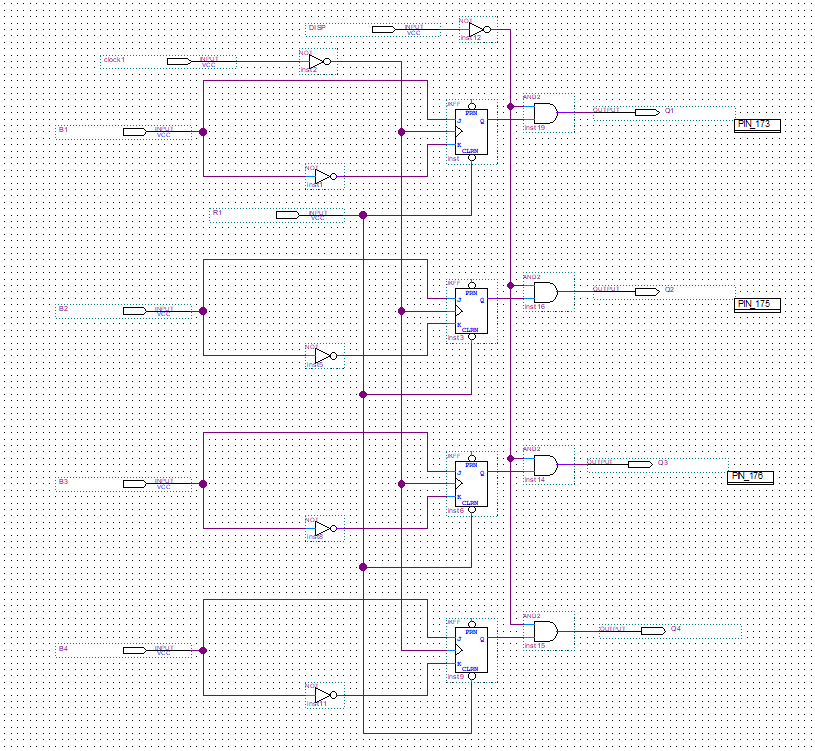

Реализация функциональной схемы в Quartus II

Рис.1 Функциональная схема регистра

Задание:

![]()

-

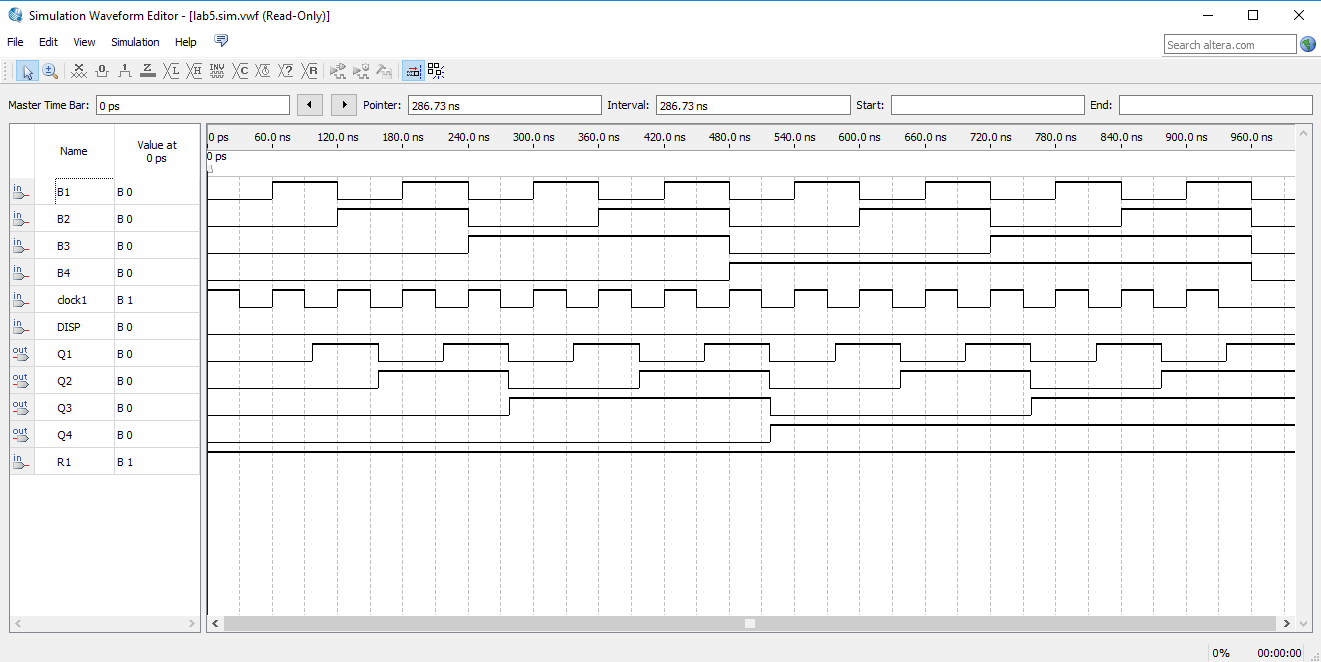

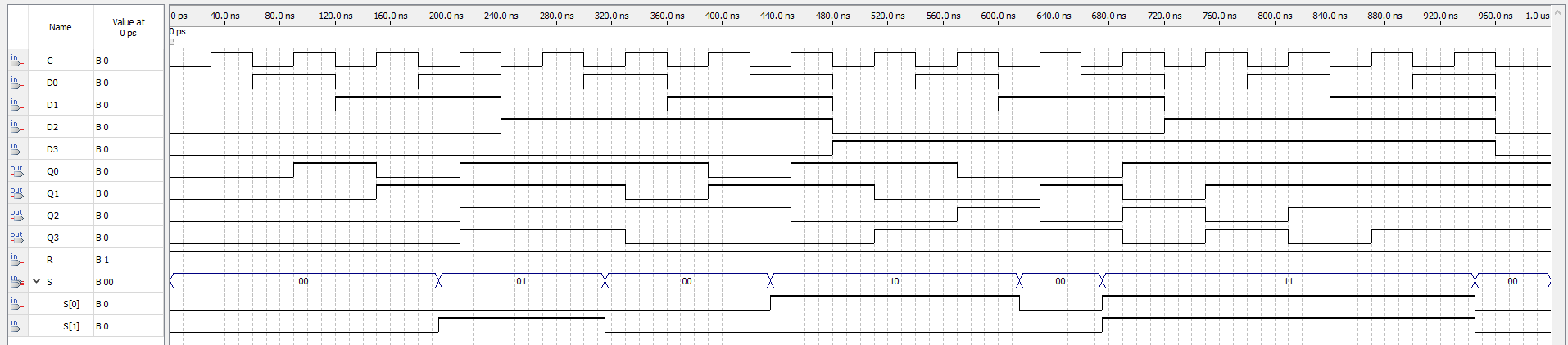

Функциональное и временное моделирование проекта

Рис. 2. Функциональное моделирование

Рис. 3. Временное моделирование

2 Часть

-

Описание процесса проектирования схемы

Задание:

![]()

![]()

![]()

![]()

Работа идет по фронту C.

Таблица истинности D триггера на базе которого строится многофункциональный регистр.

|

D |

Q(t) |

Q(t+1) |

|

0 |

0 |

0 |

|

0 |

1 |

0 |

|

1 |

0 |

1 |

|

1 |

1 |

1 |

Составим функцию возбуждения fi для i-ого D триггера

|

S0 |

S1 |

Qi-1(t) |

Qi+1(t) |

Di(t) |

fi |

|

0 |

0 |

* |

* |

0 |

0 |

|

0 |

0 |

* |

* |

1 |

0 |

|

0 |

1 |

* |

* |

* |

1 |

|

1 |

0 |

* |

0 |

* |

0 |

|

1 |

0 |

* |

1 |

* |

1 |

|

1 |

1 |

0 |

* |

* |

0 |

|

1 |

1 |

1 |

* |

* |

1 |

Di – пользовательский вход на D i-ый триггер

fi = notS0*notS1*Di V notS0*S1*1 V S0*notS1*Qi+1 V S0*S1*Qi-1

Счетик i берется по модулю 4 для сдвига влево. Для сдвига вправо надо учитывать, что Q0-1 = 1;

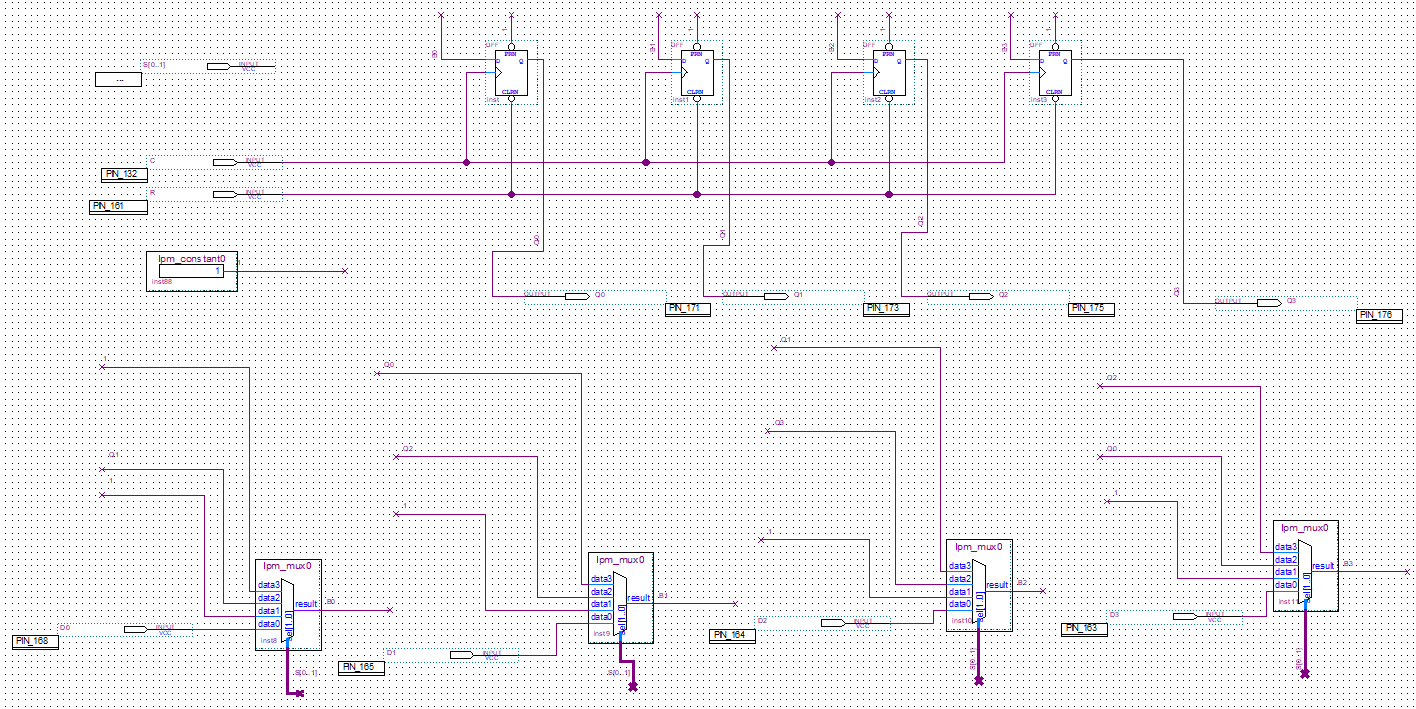

Рис.

4. Функциональная схема многофункционального

регистра

Для компактности схемы удобно воспользоваться мультиплексорами

-

Функциональное и временное моделирование проекта

Рис. 5. Функциональное моделирование

Рис.

6. Временное моделирование

-

Список и назначение внешних контактов, описание процесса макетирования

Рис. 7. Распиновка