- •1. Задание на проектирование узла 3

- •Задание на проектирование узла

- •Описание предлагаемых вариантов реализации узла

- •Описание основных элементов библиотеки сапр Quartus II необходимых для реализации вариантов узла.

- •Описание процесса синтеза и моделирования работы предложенных вариантов средствами сапр Quartus II

- •Синтез и моделирование узла на основе параллельно-последовательного регистра

- •Синтез и моделирование узла на основе мультиплексора

- •Разработка интерфейса сопряжения схемы узла с процессорной системой

- •Подробное описание функционирования узла

- •Определение частоты генератора тактовых импульсов

- •Заключение по проделанной работе

- •Список использованной литературы

МИНОБРНАУКИ РОССИИ

Санкт-Петербургский государственный

электротехнический университет

«ЛЭТИ» им. В.И. Ульянова (Ленина)

Кафедра ВТ

Пояснительная записка к курсовому проекту

по дисциплине «Узлы и устройства ЭВМ»

«Преобразователь параллельного кода в последовательный для асинхронного протокола передач»

|

Студент гр |

|

|

|

Преподаватель |

|

|

Санкт-Петербург

2019

Оглавлени

1.Задание на проектирование узла 5

2.Описание предлагаемых вариантов реализации узла 6

2.1. Схема на основе параллельно-последовательного регистра 6

2.2. Схема на основе параллельного регистра и мультиплексора 9

3.Описание основных элементов библиотеки САПР Quartus II необходимых для реализации вариантов узла. 10

4.Описание процесса синтеза и моделирования работы предложенных вариантов средствами САПР Quartus II 12

4.1. Синтез и моделирование узла на основе параллельно-последовательного регистра 12

4.2.Синтез и моделирование узла на основе мультиплексора 15

5.Разработка интерфейса сопряжения схемы узла с процессорной системой 20

6.Подробное описание функционирования узла 22

7.Определение частоты генератора тактовых импульсов 23

8.ЗАКЛЮЧЕНИЕ ПО ПРОДЕЛАННОЙ РАБОТЕ 24

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ 26

1. Задание на проектирование узла 3

2. Описание предлагаемых вариантов реализации узла 4

2.1. Схема на основе параллельно-последовательного регистра 4

2.2. Схема на основе параллельного регистра и мультиплексора 6

3. Описание основных элементов библиотеки САПР Quartus II необходимых для реализации вариантов узла. 7

4. Описание процесса синтеза и моделирования работы предложенных вариантов средствами САПР Quartus II 9

4.1. Синтез и моделирование узла на основе параллельно-последовательного регистра 9

4.2. Синтез и моделирование узла на основе параллельного регистра и мультиплексора 13

5. Разработка интерфейса сопряжения схемы узла с процессорной системой 17

6. Подробное описание функционирования узла 19

7. Определение частоты генератора тактовых импульсов 21

8. ЗАКЛЮЧЕНИЕ ПО ПРОДЕЛАННОЙ РАБОТЕ 22

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ 23

-

Задание на проектирование узла

Вариант 7.2.

Разработать узел преобразующий параллельный код в последовательный с добавлением к нему старт-бита, стоп-бита и бита паритета.

Предусмотреть возможность передачи последовательного кода со скоростями, указанными в вариантах задания. Входной параллельный код, код выбора скорости передачи и сигнал пуска передаются из управляющего устройства(процессора). Критерий выбора варианта реализации схемы – минимум аппаратных затрат.

Таблица 1.1. Вариант задания.

|

Вариант |

Разрядность входного кода, бит |

Скорость передачи, Кбит/c |

Область АП |

|

7.2 |

8 |

4,8; 9,6; 19,2 |

80h |

Возможные варианты реализации: на основе параллельно-последовательного регистра, на основе мультиплексора.

-

Описание предлагаемых вариантов реализации узла

-

Схема на основе параллельно-последовательного регистра

-

На вход узла подается сигнал load, происходит загрузка. Далее на входа узла подается сигнал start и выбор режима, схема начинает тактироваться, начинает выполняться пересылка последовательного кода, полученного из параллельного. Сигнал Stop запускает остановку передачи. Сигнал Reset приводит к принудительному сбросу устройства в начальное состояние. Сигнал C приходит от генератора тактовых импульсов. Загружаемый параллельный код выходит из шины данных. Код выбора скорости выходит из шины данных. Сигнал старт, стоп также находится на шине данных.

Выходной сигнал out представляет выходной последовательный код. Выходной сигнал ready устанавливается в высокий логический уровень после того как разрабатываемый узел передаст все входящие параллельные разряды в последовательном коде из выхода регистра. Всего использовано 3 адреса:

80h – адрес регистра загрузки

81h – адрес регистра служебных кодов

82h – отдельный адреc, пропускающий сигналы стоп и reset

Служебные биты:

x[3] – старт

x[4] - стоп

|

x[1] |

x[0] |

Режим работы узла |

|

0 |

0 |

4.8 Кбит/c |

|

0 |

1 |

9.6 Кбит/c |

|

1 |

0 |

19.2 Кбит/c |

Режим

работы узла при функциональном

моделировании был заменен, так как

квартус не дает выполнять моделирование

длиннее чем 100 микросекунд. Для того,

чтобы узел передавал биты со скоростью

19.2 Кбит/с необходимо, чтобы период

синхросигнала C составлял

,

соответственно полупериод будет равен

,

соответственно полупериод будет равен

= 38,4 КГц

= 38,4 КГц

Чтобы

уменьшить скорость передачи будем

подключать последовательно триггеры

ко входу синхросигнала C.

последовательно подключенные 2 T

триггера на выходе период

екунд

в 4 раза, сделав его

екунд

в 4 раза, сделав его

секунд. Аналогично с 1 T

триггером.

секунд. Аналогично с 1 T

триггером.

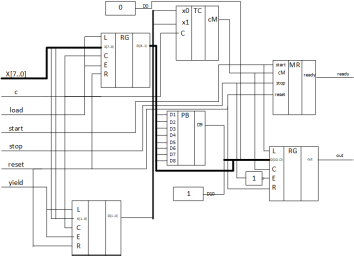

Функциональная схема данного узла приведена на рисунке 2.1.

Рисунок 2.1. Схема узла на основе параллельно-последовательного регистра.

-

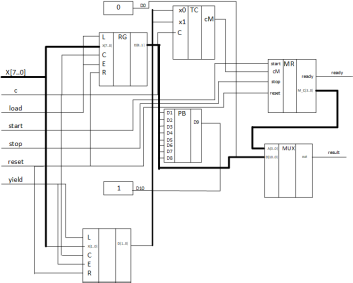

Схема на основе параллельного регистра и мультиплексора

В данном варианте реализации выходной сигнал поступает с выхода мультиплексора.

Рисунок 2.2. Схема узла на основе мультиплексора.