МИНОБРНАУКИ РОССИИ

САНКТ-ПЕТЕРБУРГСКИЙ ГОСУДАРСТВЕННЫЙ

ЭЛЕКТРОТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ

«ЛЭТИ» ИМ. В.И. УЛЬЯНОВА (ЛЕНИНА)

Кафедра ВТ

Пояснительная записка

к курсовой работе по дисциплине:

«Конструкционно-техническое обеспечение производства ЭВМ»

Вариант №12

|

Студент гр. |

|

Преподаватель: __________________ Зуев И.С.

Санкт-Петербург

2019

ЗАДАНИЕ

|

Фрагмент |

№ рис. схем |

Внешние условия включения |

Целевая функция минимизации |

S0, мкм |

|||||||

|

на входе |

на выходе |

||||||||||

|

t = 0 |

t = -∞ |

ЭИ |

ОФ |

Cf |

max

{ |

102 |

|||||

|

ИЛИ |

8; 9; 10 |

|

|

|

- |

|

|||||

-

Техническое задание

Блок схема внешних условий включения фрагмента в БИС приведена на рис. 1.1, временная диаграмма его функционирования на рис. 1.2.

Рис. 1.1. Блок-схема внешних условий включения фрагмента в БИС

Рис. 1.2. Временная диаграмма работы фрагмента БИС

Фрагмент реализует следующие логические функции:

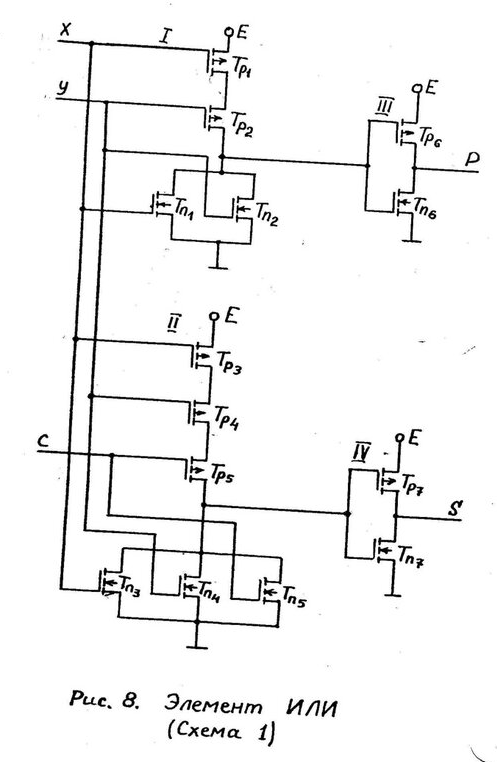

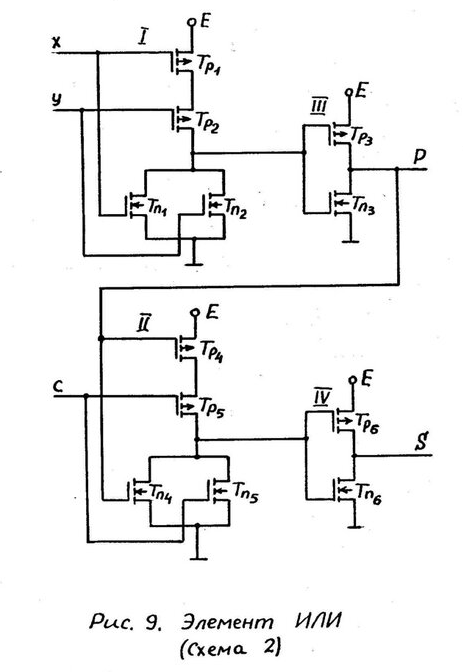

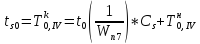

Три варианта схемы изображены на рис. 8, 9 и 10.

Временные задержки фрагмента рассчитываются для набора входных сигналов, исходя из следующих внешних условий включения:

1.

Входной сигнал

является предварительно установленным,

т.е. все переходные процессы под

воздействием этого сигнала в схеме

фрагмента уже произошли к моменту

прихода остальных сигналов.

является предварительно установленным,

т.е. все переходные процессы под

воздействием этого сигнала в схеме

фрагмента уже произошли к моменту

прихода остальных сигналов.

2.

Входные сигналы

поступают на схему фрагмента в момент

времени t

= 0, они имеют ступенчатую форму.

поступают на схему фрагмента в момент

времени t

= 0, они имеют ступенчатую форму.

3. Выходы схемы

и

и

подключены соответственно к емкости

нагрузки

подключены соответственно к емкости

нагрузки

и

и

.

.

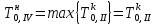

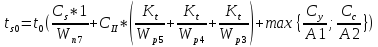

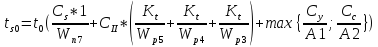

Целевой функцией условной задачи минимизации является следующая функция:

max

{ }

}

Максимальное же значение суммы ширин каналов транзисторов схемы равняется 102 мкм.

Необходимо выбрать конфигурацию схемы фрагмента и значения ширин каналов её транзисторов, минимизирующие целевую функцию при ограничении площади схемы на кристалле в заданных внешних условиях включения фрагмента в БИС, разработать топологический чертеж оптимальной схемы.

-

Расчет и оптимизация

2.1. Вывод формул и времен задержек

Для вывода формул времен задержки схем составлены их таблицы переключений – Таблица 1., Таблица 2., Таблица 3. для схем 1, 2 и 3 соответственно, в которых представлены для каждого варианта переключения и для каждого каскада фрагмента – транзисторы, образующие путь тока перезаряда нагрузочной емкости каскада и перечислены транзисторы, образующие эту емкость.

Таблица 1. Переключение фрагмента БИС (схема 1)

|

№ |

Сигнал |

Пути тока перезаряда нагрузочной емкости каскада |

||||||

|

x |

y |

c |

I |

II |

III |

IV |

||

|

0 |

0 |

0 |

0 |

Tp1, Tp2 |

Tp3, Tp4, Tp5 |

Tn6 |

Tn7 |

|

|

1 |

0 |

0 |

1 |

Tp1, Tp2 |

Tn5 |

Tn6 |

Tp7 |

|

|

2 |

0 |

1 |

0 |

Tn2 |

Tn4 |

Tp6 |

Tp7 |

|

|

3 |

0 |

1 |

1 |

Tn2 |

Tn4 || Tn5 |

Tp6 |

Tp7 |

|

|

4 |

1 |

0 |

0 |

Tn1 |

Tn3 |

Tp6 |

Tp7 |

|

|

5 |

1 |

0 |

1 |

Tn1 |

Tn3 || Tn5 |

Tp6 |

Tp7 |

|

|

6 |

1 |

1 |

0 |

Tn1 || Tn2 |

Tn3 || Tn4 |

Tp6 |

Tp7 |

|

|

7 |

1 |

1 |

1 |

Tn1 || Tn2 |

Tn3 || Tn4 || Tn5 |

Tp6 |

Tp7 |

|

Транзисторы образующие нагрузочную емкость:

=

=

+

+

=

=

+

+

=

=

+

+

+

+

=

=

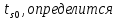

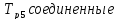

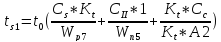

1. Вывод времен задержек формирования выходного сигнала для схемы №1

Времена

задержек выводятся, начиная с выходного

каскада.

– время конца переключения j-ого

каскада для i-ого

варианта сигнала,

– время конца переключения j-ого

каскада для i-ого

варианта сигнала,

– время начала переключения j-ого

каскада для i-ого

варианта сигнала, выведем подобную

итерационную формулу времени задержки

для первого варианта сигнала для выхода

S.

– время начала переключения j-ого

каскада для i-ого

варианта сигнала, выведем подобную

итерационную формулу времени задержки

для первого варианта сигнала для выхода

S.

Для

первого варианта сигнала схемы 1 каскад

IV

переключается через транзистор

.

Время конца его переключения, равное

времени задержки на выходе S

.

Время конца его переключения, равное

времени задержки на выходе S

Сигнал

на затворе транзистора

формируется на выходе каскада II.

Поэтому

формируется на выходе каскада II.

Поэтому

Каскад

II

переключается через транзисторы

,

,

,

,

последовательно, под воздействием

входных сигналов X,

Y,

C

(по условию X

пришел

последовательно, под воздействием

входных сигналов X,

Y,

C

(по условию X

пришел

,

переходные процессы связанные с ним

завершились). Поэтому:

,

переходные процессы связанные с ним

завершились). Поэтому:

Объединяя

полученные итерационные формулы, запишем

формулу времени задержки:

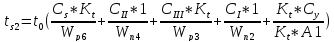

;

;

;

;

;

;

,

,

- некритические

- некритические

,

,

,

,

- некритические

- некритические

Таблица 2. Переключение фрагмента БИС (схема 2)

|

№ |

Сигнал |

Пути тока перезаряда нагрузочной емкости каскада |

||||||

|

x |

y |

c |

I |

II |

III |

IV |

||

|

0 |

0 |

0 |

0 |

Tp1, Tp2 |

Tp4, Tp5 |

Tn3 |

Tn6 |

|

|

1 |

0 |

0 |

1 |

Tp1, Tp2 |

Tn5 |

Tn3 |

Tp6 |

|

|

2 |

0 |

1 |

0 |

Tn2 |

Tn4 |

Tp3 |

Tp6 |

|

|

3 |

0 |

1 |

1 |

Tn2 |

Tn4 || Tn5 |

Tp3 |

Tp6 |

|

|

4 |

1 |

0 |

0 |

Tn1 |

Tn4 |

Tp3 |

Tp6 |

|

|

5 |

1 |

0 |

1 |

Tn1 |

Tn4 || Tn5 |

Tp3 |

Tp6 |

|

|

6 |

1 |

1 |

0 |

Tn1 || Tn2 |

Tn4 |

Tp3 |

Tp6 |

|

|

7 |

1 |

1 |

1 |

Tn1 || Tn2 |

Tn4 || Tn5 |

Tp3 |

Tp6 |

|

Транзисторы образующие нагрузочную емкость:

=

=

+

+

=

=

+

+

=

=

+

+

+

+

=

=

+

+

=

=

+

+

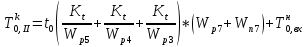

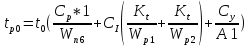

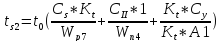

2. Вывод времен задержек формирования выходного сигнала для схемы №2

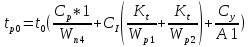

;

;

;

;

;

;

,

,

- некритические

- некритические

,

,

,

,

- некритические

- некритические

Таблица 3. Переключение фрагмента БИС (схема 3)

|

№ |

Сигнал |

Пути тока перезаряда нагрузочной емкости каскада |

||||||

|

x |

y |

c |

I |

II |

III |

IV |

||

|

0 |

0 |

0 |

0 |

Tp1, Tp2 |

Tp3 |

Tn4 |

Tn5, Tn6 |

|

|

1 |

0 |

0 |

1 |

Tp1, Tp2 |

Tn3 |

Tn4 |

Tp6 |

|

|

2 |

0 |

1 |

0 |

Tn2 |

Tp3 |

Tp4 |

Tp5 |

|

|

3 |

0 |

1 |

1 |

Tn2 |

Tn3 |

Tp4 |

Tp5 || Tp6 |

|

|

4 |

1 |

0 |

0 |

Tn1 |

Tp3 |

Tp4 |

Tp5 |

|

|

5 |

1 |

0 |

1 |

Tn1 |

Tn3 |

Tp4 |

Tp5 || Tp6 |

|

|

6 |

1 |

1 |

0 |

Tn1 || Tn2 |

Tp3 |

Tp4 |

Tp5 |

|

|

7 |

1 |

1 |

1 |

Tn1 || Tn2 |

Tn3 |

Tp4 |

Tp5 || Tp6 |

|

Транзисторы образующие нагрузочную емкость:

=

=

+

+

+

+

=

=

+

+

+

+

=

=

+

+

=

=

+

+

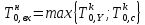

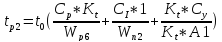

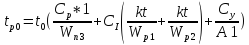

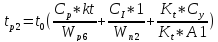

3. Вывод времен задержек формирования выходного сигнала для схемы №3

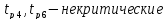

;

;

;

;

;

;

,

,

,

,

- некритические

- некритические

}

}