- •Рисунки к разделу «Организация памяти»

- •Рисунки к разделу «Регистры специальных функций»

- •Рисунки к разделу «Модуль системы прерываний»

- •Рисунки к разделу «Модуль параллельных портов ввода-вывода»

- •Рисунки к разделу «Модуль таймеров/счетчиков»

- •Рисунки к разделу «Модуль универсального асинхронного приемопередатчика»

Рисунки к разделу «Организация и структура типового микроконтроллера»

|

Структура микроконтроллера |

Рисунки к разделу «Процессорное ядро типового микроконтроллера»

|

Структура процессорного ядра микроконтроллера |

Рисунки к разделу «Модули памяти: оперативные запоминающие устройства»

|

Статическое оперативное запоминающее устройство |

Рисунки к разделу «Модули памяти: постоянные запоминающие устройства»

|

Постоянное запоминающее устройство |

Рисунки к разделу «Модуль сторожевого таймера»

|

Структура модуля сторожевого таймера |

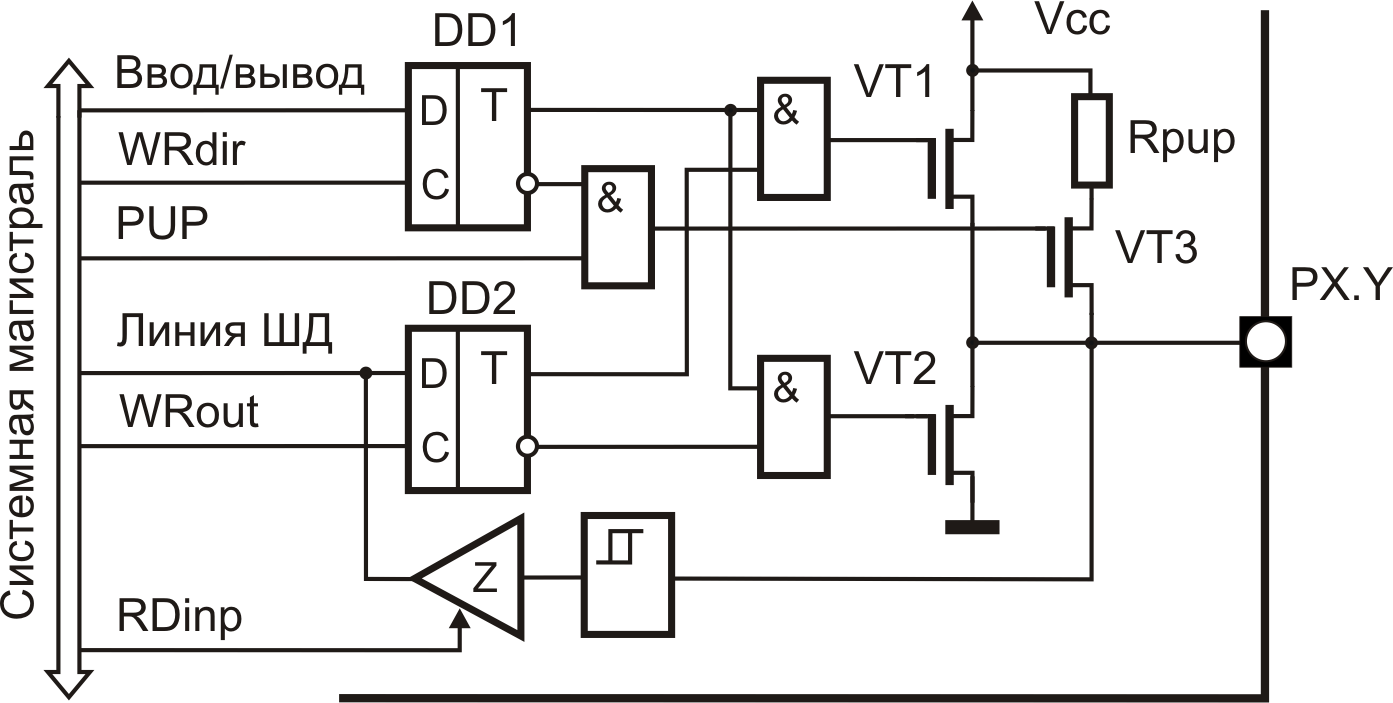

Рисунки к разделу «Модули параллельных портов ввода-вывода»

|

|

Квазидвунаправленный порт ввода-вывода |

Двунаправленный порт ввода-вывода |

|

|

Двунаправленный порт ввода-вывода с «подтягивающим» резистором |

Двунаправленный порт ввода-вывода с альтернативной функцией |

Рисунки к разделу «Модули таймеров/счетчиком и процессоров событий»

|

Модуль таймера/счетчика |

|

Структура каналов захвата/сравнения |

|

Временные диаграммы ШИМ |

|

Структура процессора событий |

Рисунки к разделу «Модули последовательного обмена»

|

|

Синхронная передача данных: а – структура; б – временная диаграмма |

Асинхронная передача данных: а – структура; б – временная диаграмма |

|

Структура модуля последовательного обмена UART |

Рисунки к разделу «Модуль АЦП»

|

Модуль аналого-цифрового преобразователя |

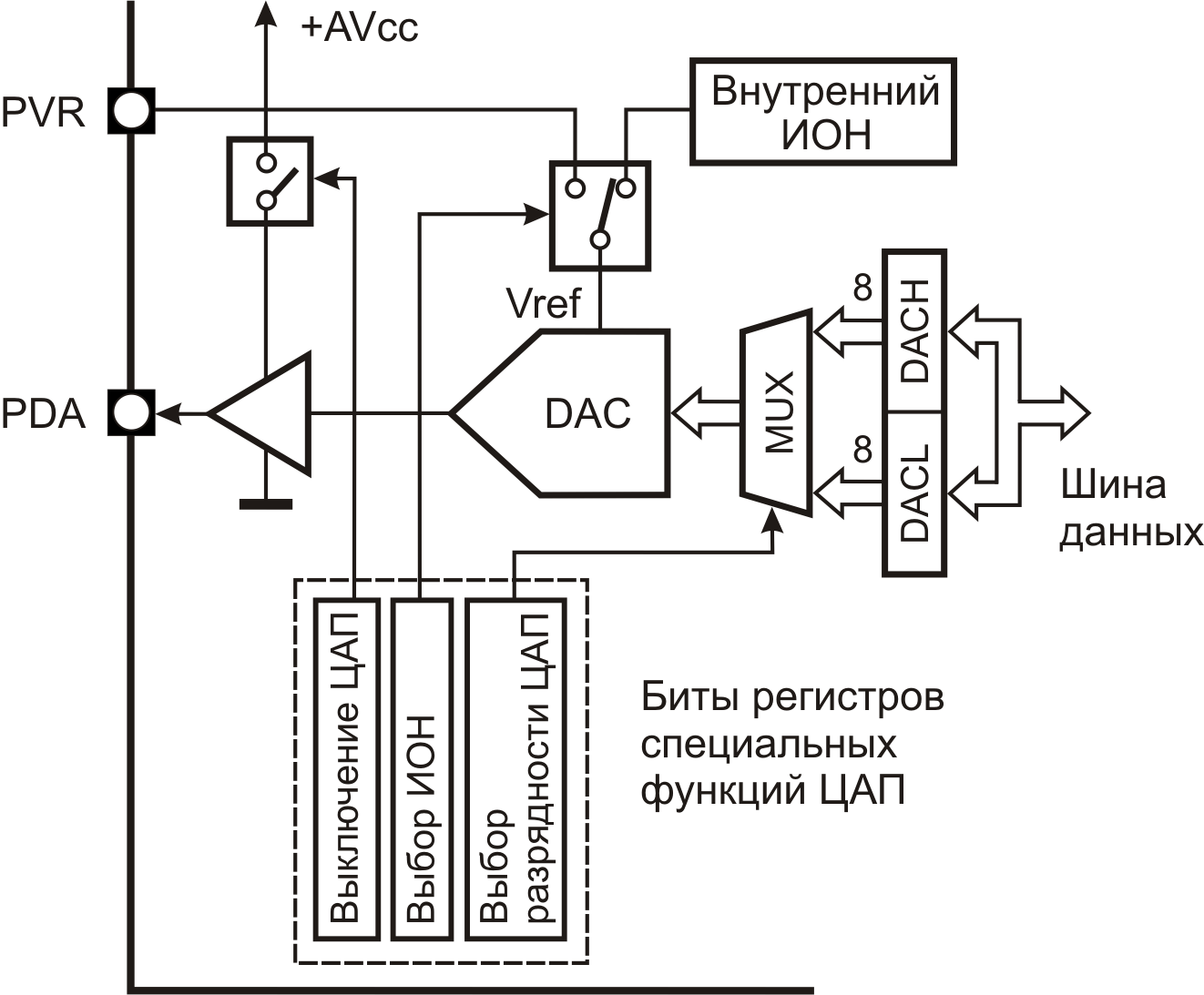

Рисунки к разделу «Модуль ЦАП»

|

Модуль цифро-аналогового преобразователя |

Рисунки к разделу «Модуль аналогового компаратора»

|

Модуль аналогового компаратора |

Рисунки к разделу «Разработка прикладных программ»

|

Процесс разработки прикладных программ |

Рисунки к разделу «Структурная схема микроконтроллера 8051»

|

Структура базового микроконтроллера 8051 |

Рисунки к разделу «Процессорное ядро микроконтроллера 8051»

|

|

Структура процессорного ядра микроконтроллера 8051 |

Структура операционного устройства |

7

|

|||||||||||||||||||||

Флаг |

Назначение |

||||||||||||||||||||

C |

Флаг переноса. Устанавливается-сбрасывается аппаратно или программно во время выполнения арифметических и логических операций |

||||||||||||||||||||

AC |

Флаг промежуточного переноса. Устанавливается-сбрасывается аппаратно при выполнении операций сложения или вычитания для индикации факта переноса-заема из бита 3 младшей тетрады |

||||||||||||||||||||

F0 |

Флаг пользователя. Устанавливается-сбрасывается программно как флаг состояния, определяемый пользователем |

||||||||||||||||||||

RS1 RS0 |

Разряды управления выбором номера банка регистров общего назначения. Устанавливаются-сбрасываются программно

|

||||||||||||||||||||

OV |

Флаг переполнения. Устанавливается-сбрасывается аппаратно во время выполнения арифметических операций для обозначения состояния переполнения |

||||||||||||||||||||

– |

Резервный разряд (состояние логической единицы) |

||||||||||||||||||||

P |

Флаг четности (паритета). Устанавливается-сбрасывается при выполнении операций для индикации четности-нечетности количества единиц в содержимом аккумулятора. Доступен только для чтения |

||||||||||||||||||||

|

Процедуры выборки команд различной сложности |

|

Структура блока шины адреса и указателей |

|

|

Длительность сигнала сброса МК |

Цепи сброса МК: а – RC-цепь; б – микросхема сброса |

Рисунки к разделу «Организация памяти»

|

Организация памяти базового микроконтроллера 8051 |

Структура резидентной памяти программ |

|

Побайтно адресуемая область ОЗУ |

||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

П

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Б назначения

|

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Структура резидентной памяти данных |

|||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|

Подключение внешней памяти программ и данных |

бласть

программ

бласть

программ

обитно

адресуемая область ОЗУ

обитно

адресуемая область ОЗУ анки

регистров общего

анки

регистров общего