Организвция ЭВм и систем

.pdf

•Сложим порядки сомножителей:

+0101 - PX

0110 - PY

1011 - PX + PY

•Нормализуем произведение:

Pнорм Z = РZ -1; qZ - сдвигаемна1 разрядвлево

1010 |

0.10011110 . |

pнорм Z |

qнорм Z |

Результат: Z = 1010 * 0.10011000(2) = 210 * 0.59375(10) = 608(10).

Задание 3. Выполнить арифметические действия над операндами, представив их в двоично-десятичном коде.

1. Выполним операцию сложения Z=X+Y= 183(10) + 331(10) = 514(10). X = 183(10) = 0001 1000 0011(2-10); Y = 331(10) = 0011 0011 0001(2-10).

+ |

0001 1000 0011 |

- X |

|

0011 0011 0001 |

- Y |

+ |

0100 1011 0100 |

- X+Y |

. . |

- коррекция 2-й цифры |

|

|

0000 0110 0000 |

|

|

|

|

|

0101 0001 0100 |

- X+Yкор |

Результат: Z = 0101 0001 0100(2-10) = 514(10).

2. Выполним операцию вычитания Z = X – Y = 183(10) – 331(10) = -148(10).

•Представим |Y| в ДК с избытком 6:

YОК →+ 1100 1100 1110

0001

YДК → 1100 1100 1111

•Выполним сложение:

XПК →+ 0001 1000 0011

YДК → 1100 1100 1111

Z’ДК → 1110 0101 0010 - нескорректированное Z в ДК

1 1 - переносы

Отсутствие переноса из старшей тетрады является признаком того, что результат получился в ДК (т.е. отрицательный).

•Перейдем к нескорректированному избыточному ПК:

Z’ДК → 1110 0101 0010

ZДК →+ 0001 1010 1101

0001

Z’ПК → 0001 1010 1110 - нескорректированное Z в ПК

70

• Произведем коррекцию результата в соответствии с п. 5 алгоритма выполнения операции вычитания двоично-десятичных чисел:

Z’ПК →+ 0001 1010 1110 коррекция → 0000 1010 1010 0001 0100 1000

переносы → |

1 |

1 отбросить |

результат |Z|= (0001 0100 1000) = 148(10)

Поскольку ранее результат получался в ДК, т.е. отрицательный, необходимо добавить знак (-).

Результат: Z = - ( 0001 0100 1000)(2-10) = -148(10).

3. Выполним операцию умножения Z = X * Y = 183(10) * 331(10) = 60573(10)

X = 183(10) = 0001 1000 0011(2-10); Y = 331(10) = 0011 0011 0001(2-10).

Для решения примера выберем вариант перемножения "младшие разряды вперед". В соответствии с п. 1 алгоритма полагаем сумму частичных произведений P0=0. (Частичные произведения будем обозначать Pi).

Y = 0011 0011 0001 |

|

X = 0001 1000 0011 |

← P0=0 |

||

1(10) |

+ |

0000 0000 0000 |

|

||

|

← P1 (1-е част. произв.) |

||||

|

|

|

0001 1000 0011 |

|

← Σ1=P0 + P1=P1 - коррекции |

|

|

|

0001 1000 0011 |

|

|

|

|

|

|

не требует |

|

|

|

|

0000 0001 1000 |

0011 |

|

|

+ |

|

← Сдвиг вправо |

||

|

|

0001 1000 0011 |

|

|

|

3(10) |

+ |

|

|

|

|

|

0001 1000 0011 |

|

← P2 (2-е част. произв.) |

||

|

+ |

|

0001 1000 0011 |

|

|

|

+ |

|

|

|

← Сдвиг вправо |

3(10) |

+ |

|

0001 1000 0011 |

|

|

|

|

0001 1000 0011 |

|

← P3 (3-е част. произв.) |

|

|

+ |

|

0001 1000 0011 |

|

|

Формирование второго и третьего частичных произведений – более длительная операция, поскольку вторая и третья анализируемые тетрады содержат 3(10), поэтому каждая операция суммирования требует проверки необходимости коррекции. Вычислим P2 ( P2 = Р3 ), последовательно суммируя слагаемые, образующие P2:

Х → |

|

0001 1000 0011 |

|

|

Х → |

+ 0001 1000 0011 |

|

||

|

|

|

|

|

P'2 неп. → |

+ |

0011 0000 0110 |

|

|

|

|

1 |

|

|

|

|

|

||

|

|

|

|

|

коррекция → |

|

0000 0110 0000 |

|

|

P2 неп. → |

|

0011 0110 0110 |

|

|

+0001 1000 0011 |

|

|||

Х → |

|

|||

|

|

|

|

|

P2 → |

|

0101 0100 1001 |

|

|

←первое слагаемое Р2

←второе слагаемое Р2

←неполное, нескорректированное Р2 тетрада требует коррекции (перенос)

←неполное, скорректированное Р2

←третье слагаемое Р2

←полное Р2, коррекции не требует

71

Таким образом, второе (а также и третье) частичное произведение, состоящее из трех слагаемых, имеет вид

P2 = Р3 = 0101 0100 1001(2-10).

Теперь можно вычислить сумму первого, второго и третьего частичного произведений, т.е. результат.

P1 → |

+ |

0000 0000 0001 1000 0011 |

←первоесдвинутоечастичноепроизведение |

||||||

P2 → |

0000 0101 0100 1001 |

|

←второесдвинутоечастичноепроизведение |

||||||

|

|

||||||||

∑‘2=P1+P2 |

+ |

|

0000 0101 0110 0001 0011 |

|

←Р1 + Р2 |

||||

|

|

|

|

1 |

|

←тетрадатребуеткоррекции(перенос) |

|||

|

|

|

|||||||

|

|

|

|

|

|

|

|||

коррекция→ |

|

0000 0000 0000 0110 0000 |

←скорректированнаясуммаР1+Р2 |

||||||

∑2=P1+P2 → |

|

0000 0101 0110 0111 0011 |

|||||||

P3 → |

|

0101 0100 1001 |

|

|

←третьечастичноесдвинутоепроизведение |

||||

∑‘3=P1+P2+P3 → |

0101 1001 1111 0111 0011 |

←Р1 + Р2+ Р3 |

|||||||

|

+ |

. . |

|

|

|

|

←тетрадатребуеткоррекции(f=1) |

||

|

|

|

|

|

|

|

|

||

|

|

|

|

|

|

|

|

|

|

коррекция→ |

|

0000 0110 0110 0000 0000 |

←скорректированнаясуммаР1+Р2+Р3 |

||||||

∑3=P1+P2+P3 → |

|

|

0110 0000 0101 0111 0011 |

||||||

Окончательный результат: Z = 0110 0000 0101 0111 0011(2-10) = 60573(10).

3. Принципы построения элементарного процессора

Ранее, при рассмотрении обобщенной структуры ЭВМ, отмечалось, что основным устройством, непосредственно осуществляющим переработку поступающей в ЭВМ информации, является процессор (в больших ЭВМ – центральный процессор). Естественно, что конкретные типы ЭВМ содержат в своем составе процессоры, построенные по различным схемам, и процессоры больших ЭВМ существенно отличаются от процессоров мини- и микроЭВМ (о суперЭВМ и говорить не приходится). Однако основные принципы построения процессоров, в общем-то, одинаковые, причем наиболее наглядно их можно продемонстрировать на примере простейшего микропроцессора. Это оправдано и с той точки зрения, что инженер-разработчик радиоэлектронной аппаратуры или аппаратов автоматического управления имеет дело не с большими ЭВМ, а с микропроцессорными комплектами и построенными на их базе мини- и микроЭВМ. Ввиду этого рассмотрев общие вопросы построения ЭВМ, более подробно остановимся на обобщенной структуре гипотетического микропроцессора.

Ранее рассматривались действия над числами (сложение, вычитание, умножение), представленными в различной форме. Было подчеркнуто, что все эти действия осуществляются с помощью элементарных операций, выполняемых в определен-

ной последовательности.

Ктаким элементарным операциям относятся:

-запись числа в регистр;

-инвертирование содержимого разрядов регистра;

-пересылка содержимого регистров;

-сдвиг содержимого регистра;

-сложение кодов;

-поразрядные логические операции или анализ разрядов;

-операция счета с+1 или с-1 (инкремент или декремент).

72

Пример.

Операция умножения реализуется с помощью:

-анализа разряда множителя;

-суммирования;

-сдвига.

Все эти действия выполняются в устройстве, называемом процессором, которое состоит из двух устройств – операционного (ОУ) и управляющего (УУ).

ОУ – выполняет указанные элементарные операции.

УУ – управляет ОУ, задавая необходимую последовательность выполнения этих операций.

Это соответствует принципу В.М. Глушкова, что в любом устройстве обработки цифровой информации можно выделить операционный и управляющий блоки.

Вкачестве узлов УУ и ОУ включают в себя регистры, счетчики, сумматоры, мультиплексоры, дешифраторы и т.д., т.е. устройства импульсной цифровой техники. Кроме того, нормальное функционирование процессора и всей ЭВМ возможно только при наличии высокостабильных импульсных последовательностей, формируемых, как правило, из одной импульсной последовательности, вырабатываемой кварцевым генератором. Эти тактовые импульсные последовательности синхронизируют работу узлов процессора, а иногда и всей ЭВМ.

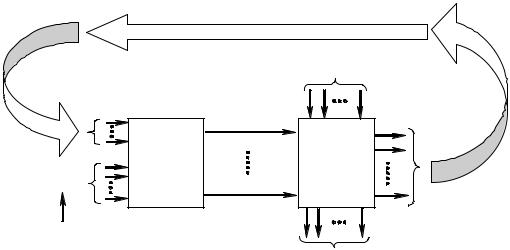

Обобщенная структура любого процессора изображена на рис. 3.1.

Каждая элементарная операция, выполняемая в одном из узлов ОУ в течение одного тактового периода, называется микрооперацией.

Вопределенные тактовые периоды одновременно могут выполняться несколь-

ко микроопераций, например: R2 ← 0, Сч ← (Сч) – 1 и т.д. Такая совокупность непротиворечивых микроопераций называется микрокомандой, а набор микрокоманд, предназначенный для решения задачи, называется микропрограммой.

Если в ОУ предусмотрена возможность выполнения n различных микроопераций, то из УУ должно выходить n управляющих цепей S1,...,Sn, каждая из которых соответствует своей микрооперации. В силу того что УУ определяет микропрограмму, т.е. какие и в какой временной последовательности должны выполняться микрооперации, оно получило название микропрограммного автомата. Соответственно ОУ часто называют операционным автоматом.

|

X |

|

|

|

Вх. данные |

||

S1 |

P1 |

|

|

УУ |

ОУ |

|

|

КОП |

Pm |

Признак |

|

Sn |

|||

результата |

|||

Код операции |

|

||

|

|

||

(+, -, /, * и т.д.) |

Вых. данные |

||

|

Z |

|

|

УУ – управляющее устройство; КОП – код операции; ОУ – операционное устройство

Рис. 3.1. Обобщенная структура процессора

73

Формирование управляющих сигналов S1,...,Sn может зависеть как от внешних сигналов КОП (команды ассемблера), так и от состояния узлов ОУ, определяемого известительными сигналами признаков состояния P1,...,Pm, поступающими с выхода ОУ на соответствующие входы УУ.

Как уже отмечалось, ОУ выполняет над исходными данными различные арифметические и логические операции, поэтому ОУ наиболее часто называют арифме-

тико-логическим устройством, или АЛУ.

Деление любого процессора на программный и операционный автоматы достаточно очевидно и не вызывает особых трудностей в понимании. Однако структурные схемы даже простейших реальных процессоров, помимо АЛУ и УУ, содержат еще ряд узлов (регистров, счетчиков, дешифраторов), которые вроде бы не относятся ни к АЛУ, ни к УУ. Для устранения путаницы в дальнейшем материале необходимо сделать ряд замечаний:

1. В абсолютном большинстве случаев устройства обработки цифровой информации имеют многоуровневую структуру, т.е. построены по принципу "матрешки". Это означает, что УУ и ОУ могут сами распадаться на пары УУ' и ОУ', которые, в свою очередь, также могут распадаться на соответствующие УУ и ОУ. Все зависит от степени детализации рассмотрения данного цифрового устройства. Этот принцип многоуровневости справедлив для всех устройств ЭВМ.

Действительно, если рассматривать процессор в целом и делить его на УУ и ОУ, то совершенно безразлично, как выполняются арифметико-логические операции в ОУ – с помощью очень сложных логических схем или с помощью простой логики, работающей под управлением какого-либо вспомогательного УУ. Аналогичные рассуждения справедливы и для УУ.

Так, например, центральный процессор больших ЭВМ общего назначения середины 70-х годов разбивался на 4-5 уровней, на каждом из которых можно выделить свое УУ и ОУ. Современные процессоры имеют еще более сложную структуру.

Более того, эти рассуждения справедливы в целом для ЭВМ, которую можно разложить на ряд виртуальных (кажущихся) машин и с каждой работать на соответствующем уровне. В общем случае современные универсальные ЭВМ имеют шесть уровней:

-уровень проблемно-ориентированного языка;

-процедурно-ориентированный язык;

-ассемблерный уровень (язык ассемблера);

-уровень операционной системы (язык операционной системы);

-традиционный машинный уровень (язык машинных команд);

-микропрограммный уровень (язык микрокоманд).

Машинные языки двух нижних уровней являются цифровыми, и программы на них состоят из длинных числовых последовательностей, очень неудобных для человека, но понятных машине. Все более высокие уровни содержат слова и аббревиатуру, что более удобно для человека.

2.Из сказанного следует, что только самые простейшие процессоры имеют один уровень и могут быть в чистом виде разложены на УУ и ОУ, состоящие из комбинационных логических схем, способных выполнять элементарные арифметикологические операции.

3.В настоящее время нет строгого определения АЛУ, что вызывает некоторую путаницу при пользовании различной литературой. АЛУ обычно обозначают так, как показано на рис. 3.2. При этом одни авторы подразумевают под АЛУ только комбинационные логические схемы, способные выполнять операции двоичного суммирования (т.е. фактически двоичный сумматор), другие – целый комплекс схем для выполнения арифметико-логических операций, который сам может быть разложен на УУ и ОУ.

74

Входы

АЛУ

Выход АЛУ – арифметико - логическое устройство

АЛУ – арифметико - логическое устройство

Рис. 3.2. Графическое обозначение простейшего АЛУ

4.Из сказанного следует вывод, что в общем случае понятия микрооперации и микропрограммы относительны и требуют конкретизации уровня рассмотрения процессора, поскольку один такт верхнего уровня может включать в себя несколько тактов нижнего уровня.

5.Для устранения путаницы при изучении основных принципов построения элементарных процессоров будем считать:

-процессор имеет один уровень;

-процессор пользуется одной тактовой последовательностью;

-значок АЛУ (см. рис. 3.2) обозначает комплекс комбинационных схем, способных выполнять двоичное суммирование, сдвиг двоичного числа, простейшие поразрядные логические операции;

-узлы микропроцессора, не относящиеся непосредственно к схеме управления, будем считать вспомогательными узлами АЛУ, или, точнее, узлами, обеспечивающими нормальное функционирование АЛУ.

3.1.Операционные устройства (АЛУ)

Вразделе "Представление информации в ЭВМ" было показано, что различные арифметические операции над числами (представленными, кроме, того в различной кодировке) требуют существенно различных последовательностей микроопераций. Кроме того, очевидно, что чем многофункциональнее электронное устройство, тем сложнее его структура (больше элементов) и тем медленнее оно работает. С другой стороны, функции такого сложного устройства может выполнить набор более простых и быстродействующих устройств, однако аппаратурные затраты и цена будут выше.

Вобщем случае операции, выполняемые в АЛУ, можно разделить на следующие группы:

-операции двоичной арифметики для ЧФЗ;

-операции двоичной (шестнадцатеричной) арифметики для ЧПЗ;

-операции десятичной арифметики;

-логические операции;

-операции индексной арифметики (при модификации адресов команд);

-операции специальной арифметики:нормализация чисел, арифметический сдвиг (сдвигаются только цифровые разряды без знакового), логический сдвиг (сдвигаются все разряды) и т.д..

ЭВМ общего назначения обычно реализуют операции приведенных выше

групп, но делают это по-разному, в зависимости от типа АЛУ, используемого в процессоре.

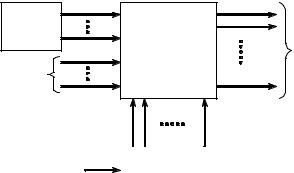

АЛУ подразделяется на блочные и многофункциональные.

В блочных АЛУ (рис. 3.3) перечисленные группы операций выполняются в отдельных электронных блоках, при этом повышается скорость работы, так как блоки могут параллельно выполнять соответствующие операции. Кроме того, специализи-

75

рованный блок всегда выполняет операции быстрее, чем универсальный перенастраиваемый блок.

X |

Арифметика |

Десятичная |

Логические |

Z |

|

|

ЧФЗ |

арифметика |

операции |

|

|

S |

Арифметика |

Специальная |

Индексная |

P |

|

ЧПЗ |

арифметика |

арифметка |

|||

|

|

X – входные данные; S – управляющие сигналы; Z – результат операции; P – извещение о завершении работы

Рис. 3.3. Блочные АЛУ

Блочные АЛУ характерны для больших ЭВМ, где главным является максимальное быстродействие, а не аппаратные затраты и стоимость. Простейшие сопроцессоры в микроЭВМ, выполняющие операции с ЧПЗ, также можно рассматривать как специализированные блоки, поэтому АЛУ микроЭВМ с сопроцессорами можно иногда рассматривать как блочные.

В многофункциональных АЛУ перечисленные группы операций выполняются одними и теми же схемами, которые коммутируются нужным образом в зависимости от требуемого режима работы. Такие АЛУ характерны для мини- и микроЭВМ, построенных на простых процессорах.

Существуют и другие структуры АЛУ (смешанные), находящиеся где-то между блочными и многофункциональными.

Следует иметь в виду, что часто ЭВМ, построенные на базе простейших микропроцессоров, имеют АЛУ, позволяющие выполнять только операции двоичной арифметики над ЧФЗ и некоторые логические операции. В этом случае остальные группы операций выполняются специальными подпрограммами, что сильно понижает скорость их выполнения.

Рассмотрим несколько подробнее структуру АЛУ простейшего процессора и определим минимально необходимый набор входящих в него устройств. Из изложенного выше следует, что в состав такого АЛУ должно входить устройство, выполняющее операции двоичного суммирования (сумматор). Кроме того, для хранения операндов и результата необходимо иметь, по крайней мере, три буферных регистра (регистры временного хранения). Однако в простейшем случае результат операции можно записывать в один из регистров временного хранения на место одного из операндов. Этот регистр принято называть аккумулятором, а процессор в целом – процессором аккумуляторного типа. Аккумулятор должен обязательно иметь двунаправленную связь с внутренней шиной данных процессора. (В более сложных АЛУ результат операции может быть записан по желанию программиста в любой из специально выделенных для этой цели регистр). Для выполнения арифметикологических операций необходимо устройство, выполняющее сдвиги двоичных чисел (сдвигатель). И, наконец, необходим регистр, в котором хранятся некоторые признаки результата выполненной операции, необходимые для функционирования УУ (регистр признаков).

Структурная схема АЛУ простейшего микропроцессора аккумуляторного типа изображена на рис. 3.4.

76

Уже отмечалось, что АЛУ в целом и двоичный сумматор имеют одно обозначение. В соответствии со сделанными ранее замечаниями регистр временного хранения и аккумулятор можно считать вспомогательными узлами АЛУ.

Внутренняя шина данных

Рг временного |

|

Аккумулятор |

хранения |

|

|

|

|

|

|

|

|

Сумматор

Рг признаков

Сдвигатель

Сдвигатель

Рис. 3.4. Структурная схема простейшего АЛУ аккумуляторного типа

3.2. Управляющие устройства

Выше отмечалось, что УУ (рис. 3.5) управляет работой АЛУ путем выработки последовательности микрокоманд, необходимых для выполнения той или иной операции (+, -, /, * и т.д.). Порядок выполнения микрокоманд определен микропрограммой реализации операции, но может изменяться в зависимости от признаков операции, вырабатываемых в АЛУ (P1,...,Pm) и подаваемых на вход УУ.

КОП |

УУ |

S |

P

УУ – управляющее устройство; S – сигнал управления (СУ); АЛУ – арифметико-логическое устройство; КОП – код операции; P – оповещающие сигналы (признаки) от АЛУ

Рис. 3.5. Общий вид УУ

Микропрограммы могут иметь как линейную структуру, так и быть разветвленными, причем условные переходы осуществляются в соответствии с признаками P.

Технические реализации УУ даже простейших процессоров разнообразны. Однако в самом общем случае их различают по способу хранения микропрограмм. По этому критерию УУ подразделяются на УУ с жесткой (схемной) логикой и УУ с хранимой в специальной памяти микропрограммой. Если микропроцессорная память

77

доступна программисту, то УУ являются микропрограммируемыми и позволяют изменить систему команд процессора. Если микропрограммная память не доступна, то процессор имеет неизменную систему команд, как и в случае УУ с жесткой логикой.

Данные варианты отличаются друг от друга принципами построения, аппаратными затратами, временем реализации микропрограмм, возможностью изменения последовательности микрокоманд, а следовательно, и системы команд процессора.

УУ современных процессоров во многих случаях комбинированные. Выполнением простых команд управляет быстродействующее УУ на жесткой логике, а выполнением сложных команд – более медленное УУ с микропрограммной памятью.

Ниже будут рассмотрены общие принципы построения обоих типов УУ.

3.2.1. УУ с жесткой логикой

УУ, построенные на жесткой логике (рис. 3.6), исторически появились первыми. Основным преимуществом таких УУ является их быстродействие. Именно поэтому абсолютное большинство специализированных процессоров, особенно предназначенных для обработки информации в режиме реального времени, имеют УУ на жесткой логике. Под специализированными понимаются процессоры, предназначенные для выполнения узкого набора специальных функций (обработка сигналов радиолокационных станций, преобразование Фурье, матричные операции, обработка сигналов в скоростных линиях связи и т.д.) с максимальной скоростью.

Однако и в процессорах общего назначения с универсальными наборами команд УУ на жесткой логике также используются очень широко, особенно, как уже отмечалось, для управления выполнением простых команд. Системы команд таких процессоров всегда фиксированные и не могут быть изменены пользователем. Подобные УУ иногда называют специализированными.

Специализированные УУ формируют неизменные последовательности сигналов управления (СУ).

Блок логических схем состоит из комбинационных схем, регистров, счетчиков, дешифраторов и других устройств, выполняющих функции запоминания текущего состояния автомата, определяющего СУ, и формирования следующего состояния в соответствии с входными признаками.

Микропрограмма в таком автомате хранится за счет системы жестких связей между узлами УУ. Для изменения микропрограммы требуется демонтаж жестких связей и создание новой схемы.

КОП |

Логические |

|

|

СУ к ОУ |

|

Признаки |

схемы |

|

|

|

|

от ОУ |

|

|

Синхроимпульсы |

Многофаз- |

|

ный счетчик |

||

от ГТИ |

||

тактов |

||

|

СУ – сигналы управления; ОУ – операционное устройство; ГТИ – генератор тактовых импульсов; КОП – код операции

Рис. 3.6. Структура УУ с жесткой логикой

78

Одним из недостатков УУ на жесткой логике является то, что любые изменения или модификации команд универсального процессора, требующие изменения микропрограмм, приведут к изменению структуры управляющего автомата, а следовательно, и топологии его внутренних связей. При производстве специализированных процессоров требуется весьма широкая номенклатура УУ (по числу решаемых задач) при относительно небольшой потребности в каждом конкретном типе. С точки зрения технологии микроэлектронного производства процессоров в виде БИС и СБИС указанный недостаток является весьма существенным. Увеличивается цена каждого выпущенного кристалла процессора за счет увеличения расходов на разработку новых топологий УУ и отладку технологии их производства.

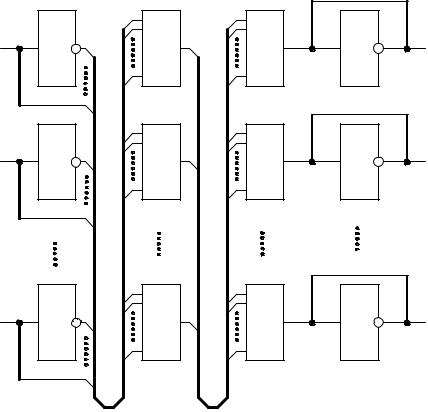

Оптимальным решением этой проблемы явилось построение УУ на специализированных логических структурах с фиксированной топологией – программируемых логических матрицах (ПЛМ). ПЛМ является слоистой структурой, в каждом слое которой сосредоточены однотипные логические элементы. Топология связей построена таким образом, что на входы каждого элемента последующего слоя подаются выходные сигналы всех элементов предыдущего слоя. ПЛМ может выполняться как отдельная БИС, так и формироваться внутри кристалла процессора, являясь весьма удобным элементом для создания управляющих автоматов.

Обобщенная функциональная схема простейшей ПЛМ представлена на рис. 3.7.

1

2

n

Слой |

|

Слой |

|

|

Слой |

Слой |

входных |

элементов |

элементов |

выходных |

|||

инверторов |

"И" |

|

"ИЛИ" |

инверторов |

||

|

|

1 |

|

1 |

|

|

1 |

1 |

& |

1 |

|

1 |

1 |

|

|

|

|

|

|

1 |

|

|

n |

|

k |

|

|

|

1' |

1 |

|

1 |

|

|

1 |

2 |

& |

2 |

|

1 |

1 |

|

|

|

|

|

|

2 |

|

|

n |

|

k |

|

|

|

2' |

|

|

|

|

|

|

|

1 |

|

1 |

|

|

1 |

n |

& |

k |

|

1 |

1 |

|

|

|

|

|

|

r |

|

|

n |

|

k |

|

|

|

n' |

|

|

|

|

|

Рис. 3.7. Функциональная схема простейшей ПЛМ

При изготовлении ПЛМ образуется схема, допускающая множество вариантов обработки входных сигналов. Входные элементы позволяют иметь все входные пе-

79