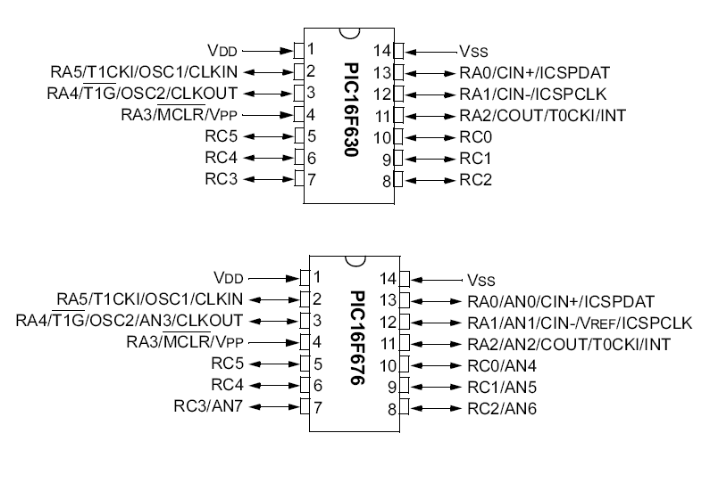

- •Расположение выводов

- •Option_reg (81h)

- •Intcon (0Bh или 8Bh)

- •Pie1 (8Ch)

- •Pir1 (0Ch)

- •Pcon (8Eh)

- •Osccal (90h)

- •Porta (05h)

- •Trisa (85h)

- •Wpua (95h)

- •Ioca (96h)

- •Portc (07h)

- •Trisc (87h)

- •T1c0n (10h)

- •Cmcon (19h)

- •Блок-схема модуля компаратора

- •Источник опорного напряжения.

- •Vrcon (99h)

- •Модуль ацп (только в pic16f676)

- •Adcon0 (1Fh)

- •Ansel (9Fh)

- •Eeprom память данных eedat (9Ah)

- •Eeadr (9Bh)

- •Eecon1 (9Ch)

- •Особенности picf630/676 Биты конфигурации

|

Master-uri.narod.ru |

|

PIC16F630/676

|

|

Описание регистров и всякое другое. |

|

Master-uri

|

Расположение выводов

Блок схема

Описание выводов

Карта памяти

STATUS (03h или 83h)

|

№-бита |

Вес бита |

Название бита |

Описание бита |

|

|

7 |

128 |

IRP |

Зарезервирован,должен поддерживатся равным “0” |

- |

|

6 |

64 |

RP1 |

Зарезервирован,должен поддерживатся равным “0” |

- |

|

5 |

32 |

RP0 |

Выбор банка(используется при прямой адресации) 1=Банк 1 (80h-FFh) 0=Банк 0 (00h-7Fh) |

R/W-0 |

|

4 |

16 |

-TO |

Флаг переполнения сторожевого таймера WDT 1= после сброса POR,выполнения команды CLRWDT или SLEEP 0= произошло переполнение WDT |

R-1 |

|

3 |

8 |

-PD |

Флаг детектора выключения питания 1= после сброса POR,или выполнения команды CLRWDT 0= после выполнения команды SLEEP |

R-1 |

|

2 |

4 |

Z |

Флаг нулевого результата операции 1=нулевой результат 0=не нулевой результат |

R/W-x |

|

1 |

2 |

DC |

Флаг десятичного переноса/заёма (команды ADDWF, ADDLW,SUBLW,SUBWF) Флаг заёма имеет инверсное значение 1=был перенос из младшего полубайта 0=не было переноса из младшего полубайта |

R/W-x |

|

0 |

1 |

C |

Флаг переноса/заёма 1=был перенос из старшего бита 0=не было переноса из старшего бита |

R/W-x |

|

Примечание: 1.Флаги C и DC используются как биты заёма и десятичного заёма соответственно,например при выполнении команд вычетания SUBLW и SUBWF. Флаг заёма имеет инверсное значение.Вычетание выполняется путём прибавления дополнительного кода второго операнда.При выполнении команд сдвига (RRF,RLF) бит С загружается старшим или младшим битом сдвигаемого регистра. | ||||

Option_reg (81h)

|

№-бита |

Вес бита |

Название бита |

Описание бита |

|

|

7 |

128 |

-RAPU |

Включение подтягивающих резисторов PORTA 1=отключены 0=включены |

R/W-1 |

|

6 |

64 |

INTEDG |

Выбор активного фронта сигнала на входе внешнего прерывания INT 1=прерывания по переднему фронту сигнала RA2/INT 0=прерывания по заднему фронту сигнала RA2/INT |

R/W-1 |

|

5 |

32 |

T0CS |

Выбор тактового сигнала для TMR0 1=внешний тактовый сигнал с вывода RA2/TOCKI 0=внутренний тактовый сигнал (CLKOUT) |

R/W-1 |

|

4 |

16 |

T0SE |

Выбор фронта приращения TMR0 при внешнем тактовом сигнале 1=приращение при переходе сигнала с “1” к “0”,на выводе RA2/TOCKI 0=приращение при переходе сигнала с “0” к “1”,на выводе RA2/TOCKI |

R/W-1 |

|

3 |

8 |

PSA |

Выбор включения предделителя 1=предделитель включен перед WDT 0=предделитель включен перед TMR0 |

R/W-1 |

|

2 |

4 |

PS2-PS0 |

Установка коэфициента деления предделителя 000=1:2 для TMR0=1:1 для WDT 001=1:4 для TMR0=1:2 для WDT 010=1:8 для TMR0=1:4 для WDT 011=1:16 для TMR0=1:8 для WDT 100=1:32 для TMR0=1:16 для WDT 101=1:64 для TMR0=1:32 для WDT 110=1:128 для TMR0=1:64 для WDT 111=1:256 для TMR0=1:128 для WDT |

R/W-1 |

|

1 |

2 | |||

|

0 |

1 | |||

|

Примечание: Если предварительный делитель включен перед WDT (3-й бит=1),то коэффициент деления тактового сигнала для TMR0 равен 1:1 | ||||