- •Лабораторная работа № 1

- •Теоретические сведения

- •1. Порты ввода/вывода

- •1.1. Общие сведения

- •1.2. Регистры портов ввода/вывода

- •1.3. Конфигурирование портов ввода/вывода

- •2. Шестнадцатибитные таймеры/счетчики

- •2.1. Управление тактовым сигналом

- •2.2. Режимы работы

- •2.2.1. Режим Normal

- •2.3. Программирование 16-тибитных таймеров/счетчиков

- •Лабораторная работа №2 (4 часа)

- •2. Произвести отладку программы средствами avrStudio.

- •3. Произвести загрузку программы в микроконтроллер.

- •Теоретические сведения

- •1. Прерывания в atMega128

- •1.1. Общие сведения

- •1.2. Таблица векторов прерываний

- •1.3. Обработка прерываний

- •1.4. Внешние прерывания

- •2. Шестнадцатибитные таймеры/счетчики

- •2.1. Управление тактовым сигналом

- •2.2. Режимы работы

- •2.3. Прерывания от таймеров/счетчиков

- •2.4. Предделители таймеров/счетчиков

- •2.4.1. Управление предделителями

- •Лабораторная работа № 3 (4 часа) «Программирование таймеров в режиме шим»

- •1. Таймеры

- •1.1. Общие сведения

- •1.2. Назначение выводов таймеров/счетчиков

- •1.3. Прерывания от таймеров/счетчиков

- •1.4. Предделители таймеров/счетчиков

- •1.4.1. Управление предделителями

- •1.5. Восьмибитные таймеры/счетчики

- •1.5.1. Управление тактовым сигналом

- •1.5.2. Режимы работы

- •2. Прерывания в atMega128

- •2.1. Общие сведения

- •2.2. Таблица векторов прерываний

- •2.3. Обработка прерываний

- •2.4. Внешние прерывания

- •3. Порты ввода/вывода

- •3.1. Общие сведения

- •3.2. Регистры портов ввода/вывода

- •3.3. Конфигурирование портов ввода/вывода

1.5.1. Управление тактовым сигналом

Формирование тактового сигнала таймера/счетчика clkT0 (clkT2) осуществляется блоком предделителя. В качестве тактового сигнала clkT0 (clkT2) таймера/счетчика T2, не имеющего асинхронного режима, может использоваться:

• системный тактовый сигнал (clkT0(Т2) = clkI/0);

• масштабированный системный тактовый сигнал (clkT0(T2) = clkI/0/n;

• внешний сигнал, поступающий на вход ТО (Т2) микроконтроллера (с1kТ0(Т2) = с1kЕхт).

Тактовый сигнал таймеров/счетчиков с асинхронным режимом может формироваться либо из системного тактового сигнала clkI/0 (clkT0 (Т2) = clkI/0/n), либо — в асинхронном режиме — из сигнала от дополнительного кварцевого резонатора (clkT0(T2) = clkTOSCI/n. Переключение между синхронным и асинхронным режимами работы осуществляется с помощью бита ASO регистра ASSR.

Выбор источника тактового сигнала, а также запуск и остановка таймеров/счетчиков осуществляются с помощью битов CS02...CS00 (CS22...CS20) регистров управления таймером TCCRn согласно Табл. 1.7.

Таблица 1.7. Выбор источника тактового сигнала таймеров/счетчиков ТО и Т2

CSn2 |

CSn1 |

CSn0 |

Источник тактового сигнала |

||

Обычный таймер/счетчик |

Асинхронный таймер/счетчик |

||||

ASn=0 |

ASn=1 |

||||

0 |

0 |

0 |

Таймер/счетчик остановлен |

Таймер/счетчик остановлен |

|

0 |

0 |

1 |

clkI/O |

clkI/O |

clkTOSCI |

0 |

1 |

0 |

clkI/O/8 |

clkI/O/8 |

clkTOSCI/8 |

0 |

1 |

1 |

clkI/O/64 |

clkI/O/32 |

clkTOSCI/32 |

1 |

0 |

0 |

clkI/O/256 |

clkI/O/64 |

clkTOSCI/64 |

1 |

0 |

1 |

clkI/O/1024 |

clkI/O/128 |

clkTOSCI/128 |

1 |

1 |

0 |

Вывод Тn, счет осуществляется по заднему фронту импульсов |

clkI/O/256 |

clkTOSCI/256 |

1 |

1 |

1 |

Вывод Тn, счет осуществляется по переднему фронту импульсов |

clkI/O/1024 |

clkTOSCI/1024 |

1.5.2. Режимы работы

Режим работы таймера/счетчика ТО (Т2) определяется состоянием битов WGMn2:WGMnO регистра TCCRn. Зависимость режима работы таймеров/счетчиков от состояния этих битов показана в Табл. 1.8.

Таблица 1.8. Режимы работы таймеров/счетчиков Т0 и Т2

Номер режима |

WGMn1 |

WGMn0 |

Режим работы таймера/счетчика |

Модуль счета (TOP) |

Обновление регистров OCRn |

Момент установки флага TOVn |

0 |

0 |

0 |

Normal |

$FF |

Немедленно |

$FF |

1 |

0 |

1 |

Phase Correct PWM |

$FF |

При TOP |

$00 |

2 |

1 |

0 |

CTC (сброс при совпадении) |

OCRn |

Немедленно |

$FF |

3 |

1 |

1 |

Fast PWM |

$FF |

При TOP |

$FF |

Режим СТС (сброс при совпадении)

В этом режиме счетный регистр тоже функционирует как обычный суммирующий счетчик, инкрементирование которого осуществляется по каждому импульсу тактового сигнала clkTn. Однако максимально возможное значение счетного регистра и, следовательно, разрешающая способность счетчика определяются регистром сравнения OCRn. После достижения значения, записанного в регистре сравнения, счет продолжается со значения $00. Если в регистре сравнения записано $FF, то в том же такте сигнала clkTn, в котором обнуляется счетный регистр, устанавливается флаг прерывания по переполнению TOVn в соответствующем регистре флагов.

При достижении счетчиком максимального значения устанавливается флаг OCFn, и, если бит ОСIEn соответствующего регистра маски установлен в 1, генерируется прерывание. Одновременно с установкой флага может изменяться состояние выводов ОСn микроконтроллера. Состояние выводов определяется битами СОМn1:СОМn0 регистра управления TCCR, как указано в Табл. 1.9.

Таблица 1.9. Управление выводами ОСn в режиме СТС

COMn1 |

COMn0 |

Описание |

0 |

0 |

Таймер/счетчик Tn отключен от вывода ОСn |

0 |

1 |

Состояние вывода меняется на противоположное |

1 |

0 |

Вывод сбрасывается в 0 |

1 |

1 |

Вывод устанавливается в 1 |

Для генерации сигнала заданной частоты необходимо записать в биты СОМn1:СОМnО значение 01 (переключение вывода). Частота генерируемого сигнала будет определяться выражением

![]() ,

,

где N — коэффициент деления предделителя.

При необходимости состояние вывода ОСn можно изменить принудительно записью лог. 1 в бит FOCn соответствующего регистра управления. Прерывание при этом не генерируется и сброса счетного регистра не производится.

Режим Fast PWM

Режим Fast PWM («Быстродействующий ШИМ») позволяет генерировать высокочастотный сигнал с широтно-импульсной модуляцией. В связи с высокой частотой генерируемого сигнала данный режим с успехом может использоваться в таких приложениях, как регулирование мощности, выпрямление, цифро-аналоговое преобразование и др.

Счетный регистр в этом режиме функционирует как суммирующий счетчик, инкрементирование которого осуществляется по каждому импульсу тактового сигнала clkTn. Состояние счетчика изменяется от $00 до максимального значения, после чего счетный регистр сбрасывается и цикл повторяется. При достижении счетчиком максимального значения устанавливается флаг прерывания по переполнению TOVn в соответствующем регистре флагов, а при равенстве содержимого счетного регистра и регистра сравнения ОСFn устанавливается флаг OCFn. Максимальное значение равно $FF.

Особенностью работы схемы сравнения в этом режиме является двойная буферизация записи в регистр OCRn, которая заключается в том, что записываемое число на самом деле сохраняется в специальном буферном регистр, а изменение содержимого регистра сравнения происходит только в момент достижения счетчиком максимального значения. Благодаря такому решению исключается появление несимметричных импульсов сигнала (помех) на выходе модулятора, которые были бы неизбежны при непосредственной записи в регистр сравнения.

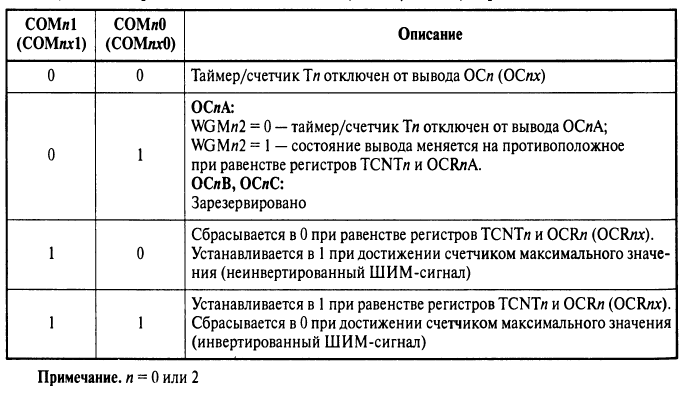

Состояние выводов ОСn микроконтроллера в этом режиме также определяется содержимым битов СОМn1:СОМn0 регистра TCCRn.

Таблица 1.10. Управление выводом OCn в режиме Fast PWM

Рис. 1.5. Формирование ШИМ-сигнала в режиме Fast PWM

Частота генерируемого сигнала определяется выражением

![]()

где N— коэффициент деления предделителя.