2. Опис макета для проведення дослідження

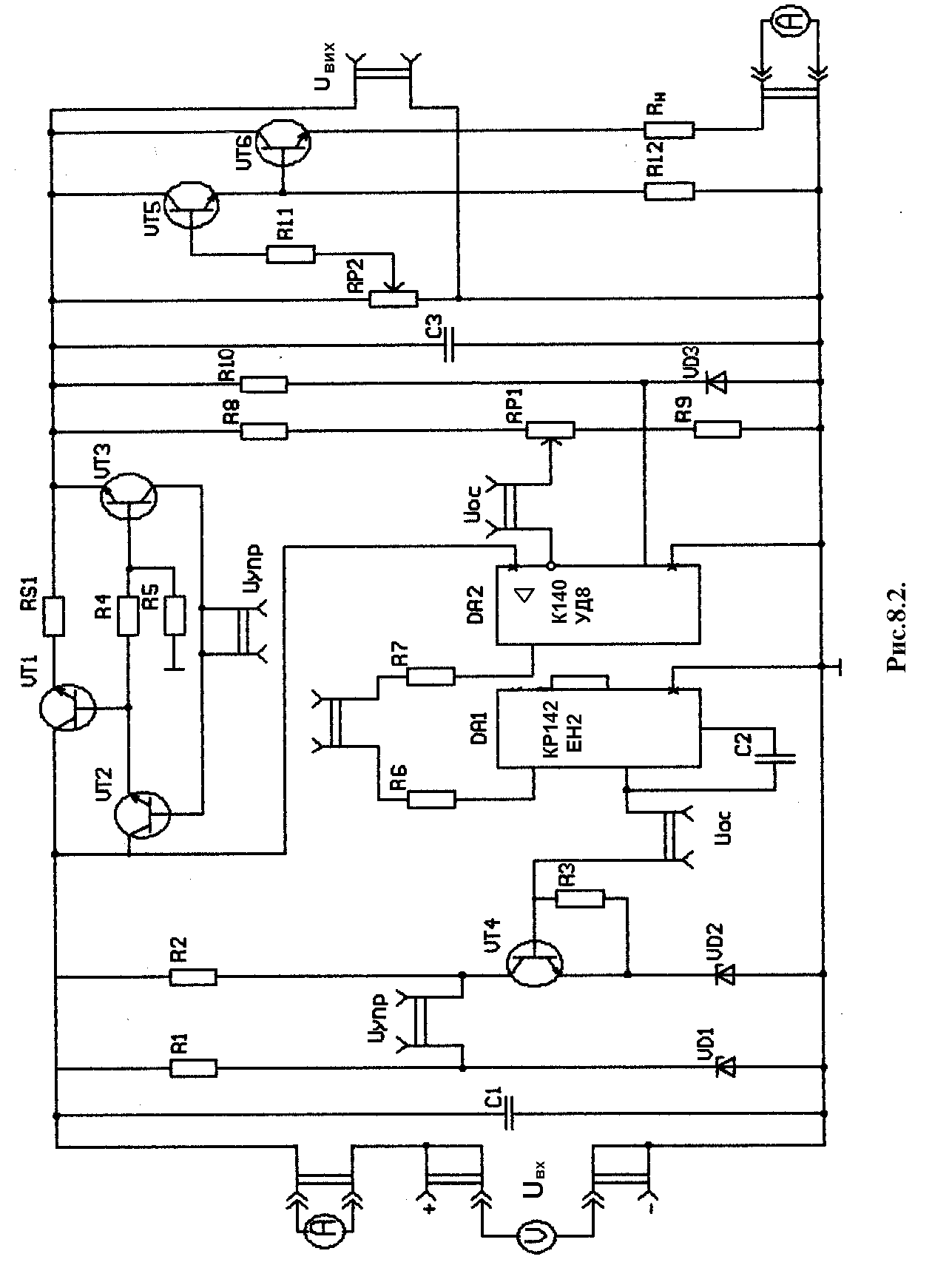

Електрична схема модуля макета для дослідження неперервних компенсаційних стабілізаторів, представлена на рис. 8.2. Дана схема дозволяє проведення досліджень схем стабілізації, показаних на рис. 8.1, а, б, в, г за рахунок комутації відповідних колів керування і негативного зворотного зв'язку по напрузі. Схема містить у собі регулюючий елемент, виконаний на складеному транзисторі VТ1, VТ2, вузол захисту по струму, виконаний на транзисторі VТЗ, регулятор струму навантаження виконаний на складеному транзисторі VТ5, VТ6, у коло емітера якого включений опір навантаження Rн, а також відповідні схеми порівняння і посилення сигналу зворотного зв'язку (VT4, DА1, DA2) .

Опорна напруга для схеми стабілізатора, зображеної на рис. 8.1,а, формується на стабілітроні VD1; для схеми рис. 8.1,6 - на VD2; для схеми рис. 8.1, в - на VDЗ. У схемі з інтегральним стабілізатором (рис.8.1,г) використовується внутрішнє джерело опорної напруги.

Коло, що складається з резисторів R8, R9, RР1, служить для формування сигналу зворотного зв'язку і регулювання вихідної напруги стабілізаторів.

Для

захисту по струму використовується

коло, що складається з транзистора VТЗ,

і резисторів RS1, R4, R5. Схема захисту

побудована таким чином, що при струмі

навантаження

![]() транзистор VТЗ закритий напругою зсуву,

яка подається через R5 на базу. При

збільшенні струму, коли

транзистор VТЗ закритий напругою зсуву,

яка подається через R5 на базу. При

збільшенні струму, коли

![]() ,

зростає спадання напруги на резисторі

RS1 і на базі транзистора VТЗ зростає

напруга Uбэ.3

. Він відкривається і шунтує перехід

база-емітер складеного транзистора

VТ2, VТ1. Останній закривається і напруга

на виході стабілізатора зменшується,

і тим самим зменшується замикаюча

напруга, подана через R5 на базу транзистора

VТЗ.

,

зростає спадання напруги на резисторі

RS1 і на базі транзистора VТЗ зростає

напруга Uбэ.3

. Він відкривається і шунтує перехід

база-емітер складеного транзистора

VТ2, VТ1. Останній закривається і напруга

на виході стабілізатора зменшується,

і тим самим зменшується замикаюча

напруга, подана через R5 на базу транзистора

VТЗ.

Це приводить до ще більшого зменшення опору VТЗ і запиранню VТ1, VТ2. При короткому замиканні на виході стабілізатора у колі навантаження встановлюється значення струму . У такий спосіб схема забезпечує захист стабілізатора по струму з обмеженням потужності, що розсіюється на регулюючому транзисторі VТ1.

3. Порядок виконання роботи

1. Ознайомитися з електричною принциповою схемою модуля і досліджуваних схем стабілізаторів, зображеними на рис. 8.1 і рис. 8.2.

2. Підключити прилади для виміру струму і напруги на вході і виході стабілізатора.

3. Зібрати схему для дослідження стабілізатора напруги (рис.8.1,а). Для цього з'єднати на макеті коло В.1, VD1 з базою транзистора VТ2 і підключити схему до джерела постійної напруги.

3.1. Установити ручку потенціометра RР2 у положення, що відповідає максимальному значенню струму навантаження і змінюючи величину вхідної напруги від 10 до 14 В визначити зміна вихідної напруги:

![]() , при

Iн

= const.

, при

Iн

= const.

3.2. Установити номінальне значення вихідної напруги рівне 12 В и змінюючи величину струму навантаження від Ін.мах до 0 визначити зміну вихідної напруги:

![]() , при

Uвх=

const.

, при

Uвх=

const.

Виконати дослідження схеми стабілізатора, зображеної на рис. 8.1,6. Для цього коло бази транзистора VТ2 з'єднати з колектором транзистора VТ4, а коло зворотного зв'язку від резистора R1 з'єднати з базою транзистора VТ4. Номінальне значення вихідної напруги

вибирається відповідно до таблиці 8.1

за указівкою викладача.

вибирається відповідно до таблиці 8.1

за указівкою викладача.

Таблиця 8.1

№ варіанта

|

1

|

2

|

3

|

4

|

5

|

6

|

7

|

8

|

Uн, В |

14.8

|

15

|

15.5

|

16

|

16.5

|

17

|

17,5

|

18

|

4.1.

Визначити мінімальний спад напруги на

регульованому транзисторі ΔUvt1.

Для цього визначити величину вхідної

напруги на 4-5 В вище

![]() і при максимальному значенні струму

навантаження установити на виході

напругу рівну Uвых.ном..

Зменшити UВХ

до величини рівної Uвх.ном.

і

вимірити напругу на виході. При цьому:

і при максимальному значенні струму

навантаження установити на виході

напругу рівну Uвых.ном..

Зменшити UВХ

до величини рівної Uвх.ном.

і

вимірити напругу на виході. При цьому:

![]()

4.2. Змінюючи величину напруги на вході від Uвх.min.=Uвых.ном.+ΔUvt1+0.5 до Uвх.мах.=1.2·Uвх.min. при максимальному значенні струму навантаження визначити залежність:

ΔUвых=f(Uвх), при IН= const.

4.3.Установити

номінальне значення вхідної напруги,

рівне

![]() і змінюючи величину струму навантаження

від

і змінюючи величину струму навантаження

від

![]() до 0 визначити залежність:

до 0 визначити залежність:

![]() ,

при

,

при

![]()

5. Зібрати схему для дослідження стабілізатора напруги, зображену на рис. 8.1, в. Для цього коло бази транзистора VT2 з'єднати з виходом мікросхеми DА2 (резистор R7) , а коло зворотного зв'язку від резистора RР1 з'єднати з інвертуючім входом мікросхеми DА2. Виконати виміру відповідно до пп.4.1, 4.2, 4.3.

6. Зібрати схему для дослідження стабілізатора напруги, показаного на рис. 8.1, г. Для цього коло зворотного зв'язку мікросхеми DА1 з'єднати з резистором RР1, а вихід, через резистор Rб - з базою транзистора VТ2. Виконати виміру по пп.4.1, 4.2, 4.3. Всі отримані результати вимірів занести в таблицю 8.2.

Таблиця 8.2.

№ |

Uвих.н В

|

Iн.max mA |

ΔUvt1 В |

Uвх.ном В |

Iвх.ном mA |

ΔUвих= =f(Iн) Uвх=const |

ΔUвих= =f(Iв) Iн=const |

Kст |

Rвих |

δ |

η |

1 |

|

|

|

|

|

|

|

|

|

|

|

2 |

|

|

|

|

|

|

|

|

|

|

|

3 |

|

|

|

|

|

|

|

|

|

|

|

4 |

|

|

|

|

|

|

|

|

|

|

|

5 |

|

|

|

|

|

|

|

|

|

|

|

6 |

|

|

|

|

|

|

|

|

|

|

|