- •Семестр 2. Раздел 1. Архитектура эвм

- •Тема 6. Сетевые устройства: сетевые платы, сетевое оборудование 124

- •Тема 7. Параллельные архитектуры, графические процессоры. Языки cuda и OpenCl. Квантовые вычисления, днк-компьютеры, нанопроцессоры. 132

- •Тема 1. Архитектуры эвм. Принципы фон Неймана. Конвейеры. Тактовый генератор и резонаторы. Архитектура компьютера

- •Архитектура фон Неймана

- •Принципы фон Неймана

- •Гарвардская архитектура

- •Скалярный процессор

- •Векторный процессор

- •Вычислительный конвейер

- •[Править] Пузырек

- •Генератор тактовых импульсов

- •Кварцевый резонатор

- •Тема 2. Схема цпу, регистры, шины, мосты, чипсеты, слоты расширения, порты

- •Типовые структуры операционного блока микропроцессора

- •Системная шина микропроцессора

- •Принципы построения параллельного порта

- •Принципы построения последовательного порта

- •Синхронные последовательные порты

- •Асинхронные последовательные порты

- •Принципы построения микропроцессорных таймеров

- •Чипсеты современных компьютеров

- •Компоненты южного моста

- •Тема 3. Пзу, озу и способы их организации. Ассоциативная память (кэш). Пзу

- •Статические оперативные запоминающие устройства - озу (ram)

- •Кэширование, выполняемое операционной системой

- •Алгоритм работы кэша с отложенной записью

- •Алгоритм вытеснения

- •Политика записи при кэшировании

- •Кэширование интернет-страниц

- •Кэширование результатов работы

- •Тема 4. Накопители данных: накопители на жестких магнитных дисках, накопители на гибких магнитных дисках, накопители на магнитных лентах, оптические накопители, flash-память Жёсткий диск

- •Устройство

- •Гермозона

- •Устройство позиционирования

- •Блок электроники

- •Низкоуровневое форматирование

- •Геометрия магнитного диска

- •Адресация данных

- •Технологии записи данных

- •Метод продольной записи

- •Метод перпендикулярной записи

- •Метод тепловой магнитной записи

- •Накопитель на гибких дисках

- •Конструкция

- •Оптический диск

- •[Править] Некоторые параметры оптических дисков

- •Флеш-память

- •Принцип действия[1]

- •Nor и nand приборы

- •Slc и mlc приборы

- •[Править] Аудиопамять

- •[Править] Технологические ограничения

- •[Править] Специальные файловые системы

- •[Править] nand

- •Твердотельный накопитель

- •[Править] nand ssd

- •[Править] ram ssd

- •Тема 5. Устройства ввода и вывода данных: принтеры, сканеры, факс-модемы, мыши, клавиатуры, мониторы, электронная бумага Принтер

- •[Править] Классификация

- •[Править] Матричные принтеры

- •[Править] Сравнение с другими типами

- •[Править] Струйные принтеры

- •[Править] Классификация

- •[Править] Сублимационные принтеры

- •[Править] Сравнение с другими типами

- •[Править] Лазерные принтеры

- •[Править] Сравнение с другими типами

- •[Править] Другие принтеры

- •[Править] Интернет-принтеры

- •[Править] История и принципы работы

- •[Править] Обзор современных технологий цифровой печати

- •[Править] Картридж принтера

- •[Править] Печатающая головка

- •Копировальный аппарат

- •История

- •Модуляция

- •[Править] Виды модуляции

- •[Править] Аналоговая модуляция

- •[Править] Цифровая модуляция

- •[Править] Импульсная модуляция

- •[Править] Развёртка

- •[Править] Модуляция

- •[Править] Каналы связи

- •[Править] Приём сигнала

- •[Править] Свёртка

- •[Править] Запись изображения

- •[Править] Запись информации

- •Компьютерная мышь

- •[Править]Трекболы

- •[Править]Сенсорные полоски и панели

- •Компьютерная клавиатура

- •Монитор (устройство)

- •Жк-дисплей

- •Электронная бумага

- •Тема 6. Сетевые устройства: сетевые платы, сетевое оборудование

- •Активное сетевое оборудование

- •Пассивное сетевое оборудование

- •[Править] Принцип работы

- •[Править] Таблица маршрутизации

- •[Править] Применение

- •Сетевой коммутатор

- •Сетевой концентратор

- •[Править] Упрощённое описание принципа работы

- •[Править] Характеристики сетевых концентраторов

- •Межсетевой экран

- •Другие названия

- •Разновидности сетевых экранов

- •[Править] Типичные возможности

- •Тема 7. Параллельные архитектуры, графические процессоры. Языки cuda и OpenCl. Квантовые вычисления, днк-компьютеры, нанопроцессоры. Квантовый компьютер

- •Теория [править] Кубиты

- •[Править] Вычисление

- •[Править] Алгоритмы

- •[Править] Квантовая телепортация

- •[Править] Применение квантовых компьютеров [править] Специфика применения

- •[Править] Приложения к криптографии

- •[Править] Физические реализации квантовых компьютеров

- •Транзисторы на нанотрубках

- •Графический процессор

- •Массово-параллельная архитектура

- •Многоядерный процессор

- •Hyper-threading

Тема 2. Схема цпу, регистры, шины, мосты, чипсеты, слоты расширения, порты

Зако́н Му́ра — эмпирическое наблюдение, сделанное в 1965 году (через шесть лет после изобретения интегральной схемы), в процессе подготовки выступления Гордоном Муром (одним из основателей Intel).

Мур высказал предположение, что число транзисторов на кристалле будет удваиваться каждые 24 месяца. При анализе графика роста производительности запоминающих микросхем им была обнаружена закономерность: появление новых моделей микросхем наблюдалось спустя примерно одинаковые периоды (18—24 мес.) после предшественников, при этом количество транзисторов в них возрастало каждый раз приблизительно вдвое. Гордон Мур пришел к выводу, что при сохранении этой тенденции мощность вычислительных устройств за относительно короткий промежуток времени может вырасти экспоненциально.

Это наблюдение получило название закон Мура. Существует масса схожих утверждений, которые характеризуют процессы экспоненциального роста, также именуемых «законами Мура». К примеру, менее известный «второй закон Мура»[1], введённый в 1998 году Юджином Мейераном, который гласит, что стоимость фабрик по производству микросхем экспоненциально возрастает с усложнением производимых микросхем. Так, стоимость фабрики, на которой корпорация Intel производила микросхемы динамической памяти ёмкостью 1 Кбит, составляла 4 млн. $, а оборудование по производству микропроцессора Pentium по 0,6-микрометровой технологии c 5,5 млн. транзисторов обошлось в 2 млрд. $. Стоимость же Fab32, завода по производству процессоров на базе 45-нм техпроцесса, составила 3 млрд. $[2].

«Если бы авиапромышленность в последние 25 лет развивалась столь же стремительно, как промышленность средств вычислительной техники, то сейчас самолёт Boeing 767 стоил бы 500 долл. и совершал облёт земного шара за 20 минут, затрачивая при этом пять галлонов (~18,9 л) топлива. Приведенные цифры весьма точно отражают снижение стоимости, рост быстродействия и повышение экономичности ЭВМ».

— Журнал «В мире науки» (1983, № 10)[3] (русское издание «Scientific American»)

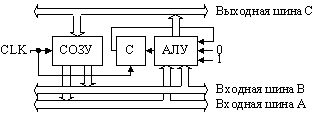

Типовые структуры операционного блока микропроцессора

Основным узлом операционного блока микропроцессора является арифметико-логическое устройство, внутреннее устройство которого мы рассмотрели в предыдущей главе. У этого узла присутствуют два входа и один выход данных. В результате логичным образом получается структурная схема операционного блока, приведенная на рис. 1.

Рис. 1 Трёхшинная структура операционного блока микропроцессора

На этом рисунке источники информации и результат выполнения операции хранятся в специальном сверхоперативном ОЗУ, которое представляет собой небольшое количество регистров с возможностью одновременного считывания из двух регистров и записи в третий. Так как для передачи данных требуется три шины данных, то такая структура операционного блока называется трехшинной.

Обратите внимание, что теперь в составе цифрового устройства присутствуют регистры, и, следовательно, для запоминания результатов работы арифметико-логического устройства на вход синхронизации этих регистров необходимо подавать сигнал синхронизации CLK. Сигнал тактовой синхронизации обязательно требуется для правильной работы любого операционного блока.

Тактовые сигналы на операционный блок микропроцессора поступают с выхода тактового генератора, причем, максимально возможная частота этого генератора, а, следовательно, и время выполнения микропроцессором одной операции будет определяться временем прохождения цифровых сигналов через арифметико-логическое устройство и регистры сверхоперативного запоминающего устройства. Очень часто быстродействие микропроцессоров оценивают именно по значению максимально возможной частоты тактового генератора.

Обычно при построении операционного блока микропроцессора один из регистров-источников и регистр-приемник информации объединяют. Это позволяет сократить количество адресных шин в управляющем коде микропроцессора. В результате минимальное количество регистров в сверхоперативном ОЗУ составляет два регистра, однако количество регистров в операционном блоке обычно делается равным шестнадцати. Этого количества регистров вполне достаточно для реализации достаточно сложных алгоритмов обработки данных и в то же время не приводит к необходимости значительного увеличения адресной части управляющей микрокоманды.

В микропроцессорной системе с применением трехшинного операционного блока возможно выполнение арифметических и логических операций в течение одного такта сигнала синхронизации. Это позволяет достигнуть максимального быстродействия микропроцессора. Именно поэтому подобная структура операционного блока широко используется внутри микросхем сигнальных процессоров.

Для обеспечения возможности работы с числами, число разрядов в которых превышает разрядность АЛУ, в состав операционного блока включен дополнительный триггер, в котором хранится флаг переноса в следующий разряд "C". При этом для того, чтобы операционный блок мог выполнять операции суммирования или вычитания с одиночной разрядностью чисел, к входу переноса АЛУ можно подключать не только выход триггера хранения флага переноса C, но и подавать уровень логического нуля или единицы.

В качестве недостатка трехшинной структуры операционного блока следует назвать то, что шины передачи данных занимают огромную площадь на кристалле микросхемы, поэтому в более дешевых микропроцессорах используется другая структура операционного блока. Структурная схема подобного операционного блока микропроцессора приведена на рис. 2.

Рис. 2 Двухшинная структура операционного блока микропроцессора

На данном рисунке сигнал синхронизации не показан, однако этот сигнал подводится ко всем регистрам и триггеру хранения признака переноса C. В этой структуре операционного блока микропроцессора используется только две шины передачи данных, поэтому она получила название двухшинной. Для формирования двух источников данных для входов АЛУ в двухшинной схеме операционного блока микропроцессора используются два регистра временного хранения TMP1 и TMP2.

В результате того, что входные данные к арифметико-логическому устройству передаются по одной шине данных, получается, что для выполнения одной операции требуется, как минимум, два такта сигнала синхронизации CLK. Это приводит к тому, что быстродействие данной структуры при той же частоте тактовой синхронизации микропроцессора будет ниже быстродействия трехшинной структуры операционного блока микропроцессора.

Наименьшую площадь на кристалле занимает одношинная структура операционного блока микропроцессора. Структурная схема подобного операционного блока микропроцессора приведена на рис. 3.

Рис. 3 Одношинная структура операционного блока микропроцессора

Теперь давайте рассмотрим подробнее особенности работы микропроцессора, построенного на основе подобного операционного блока. Прежде чем рассматривать его внутреннее устройство, определим, какие же задачи должен решать микропроцессор. Как уже упоминалось ранее, операционный блок микропроцессора предназначен для считывания команд из системной памяти процессора и последующего их выполнения. При этом не важно будет ли программа размещена в постоянном или оперативном запоминающем устройстве. Именно поэтому прежде чем перейти к построению операционного блока микропроцессора рассмотрим особенности команд, управляющих его работой.

Наиболее простой структурой, как это тоже уже упоминалось ранее, обладают команды аккумуляторного микропроцессора. Давайте остановимся подробнее на принципах построения команд подобного процессора.