- •Федеральное агентство по образованию

- •1.3. Исходные данные для курсового проектирования

- •1.4. Средства реализации модели

- •1.5. Результаты проектирования

- •2. Разработка архитектуры цп

- •2.1. Уточнение структуры системы

- •2.2. Архитектура внешних выводов

- •2.3. Выбор форматов данных

- •2.4. Определение модели памяти и структуры регистровой памяти

- •2.5. Выбор форматов команд

- •2.6. Разработка системы команд

- •2.7.Внутренняя организация

- •2.8. Основные алгоритмы функционирования

- •2.9. Алгоритмы выполнения отдельных операций.

- •2.10. Алгоритмы выполнения операций на шине.

- •3. Программный симулятор процессора

- •3.1. Руководство оператора

2.8. Основные алгоритмы функционирования

Общий алгоритм работы процессора представлен на схеме ниже.

2.9. Алгоритмы выполнения отдельных операций.

Ниже представлены алгоритмы выполнения операций, не раскрытых на предыдущей схеме.

Выполнение операции обращения к памяти

Алгоритм выполнения арифметических операций

Операция чтения следующей команды из кэша команд аналогична операции чтения данных из кэша данных за тем исключением, что команда сохраняется не в РОН, как в случае с данными, а в регистре NC. В случае, когда текущая команда в регистре CI недействительна (ее адрес не совпадает с PC), из кэша данных считываются сразу две команды.

При выполнении команды «вызов подпрограммы» значение PC сохраняется в регистре RG7, а в PC записывается адрес начала подпрограммы. По команде RET в PC загружается RG7 и продолжается выполнение основной программы.

2.10. Алгоритмы выполнения операций на шине.

Операция «чтение данных» в данном процессоре не используется, т.к. при кэш-попадании данные и команды берутся из кэша, а при промахе включается пакетное чтение из памяти.

Запись в память данных: временная диаграмма приведена на рисунке ниже. По фронту CLK процессор выставляет сигналы ALE (сообщает, что по шине будет передаваться адрес) и BHE (позволяет определить, сколько байт данных нужно передать), а также одновременно с ними сигнал WR. Потом выставляет адрес на шину адреса/данных. По спаду сигнала CLK процессор убирает сигнал ALE, сообщая памяти, что на шину будут выставлены данные. Процессор держит данные на шине данных до тех пор, пока по следующему фронту либо снова не установится сигнал ALE, либо не уберется сигнал WR.

Временная диаграмма записи в память

Пакетное чтение выполняется схожим образом; см. рис. ниже. Разница в том, что выставляется сигнал RD вместо WR, а также сигнал FRAME, который снимается за 1 такт до конца пакетного обмена; адрес при этом подается на шину адреса всего один раз, т.к. при пакетном чтении / записи данные записываются / читаются подряд.

Временная диаграмма пакетного чтения

Ниже показана временная диаграмма на шине в случае прерывания. Источник прерывания выставляет на шину сигнал INT; процессор, выполнив необходимую подготовку (завершив последнюю команду) выставляет сигнал INTA (готовность принять прерывание); источник посылает вектор прерывания по шине.

Временная диаграмма прерывания.

Захват шины неким устройством показан на рис. ниже. Сигнал HLDR означает желание сделать захват, HLDA, исходящий от процессора, является разрешающим (т.е. процессор завершил нужные операции и освободил шину).

Захват шины.

3. Программный симулятор процессора

3.1. Руководство оператора

Запуск программы производится двойным кликом по исполняемому файлу Project2.exe. Для работы требуется ОС не старше Windows 2000.

После запуска можно наблюдать главное окно программы.

Данное окно содержит следующие элементы:

Группа «Память команд». Она, в свою очередь, включает в себя следующие элементы:

Таблица со значениями ячеек памяти команд и их адресами в 16-чном виде;

Поле «Начальный адрес», изменяя которое и нажимая кнопку «Установить» можно изменить адреса просматриваемых ячеек памяти команд;

Кнопки для управления основанием системы счисления;

Галочки «Со знаком», включая которые можно просмотреть интерпретацию компьютером значения в ячейке памяти команд при условии, что старший разряд ячейки – знаковый;

Галка «показывать обращения к кэшу». При ее включении при каждом обращении к памяти команд будет выдаваться сообщение о результате обращения к кэшу: промах чтения, промах записи, попадание чтения, попадание записи.

Группа Память данных – включает в себя те же элементы, что и предыдущая группа, однако все они относятся к памяти данных, а не команд.

Группа «РОН». Содержит таблицу со значениями регистров общего назначения, а также элементы, содержащиеся в предыдущих двух группах.

Группа «Код программы». Данная группа содержит поле, в которое следует ввести код программы на псевдоассемблерном языке, а также поле «Записать в ОП с адреса», в которое вводится адрес ячейки, начиная с которой произойдет запись программы в память команд. Запись происходит по нажатию кнопки «Записать».

Группа «Флаги» - содержит значения регистра флагов. Для редактирования доступно только поле «Т» - режим пошагового выполнения команд. Для изменения значения Т необходимо ввести в поле новое значение и нажать кнопку «Установить».

Поле PC – содержит значение регистра PC. Доступно для редактирования. Для изменения значения необходимо ввести новое и нажать кнопку «Установить».

Кнопка «Выполнить» - при Т = 0 выполняет программу, начиная с адреса, находящегося в PC, до команды, первые 6 бит которой равны 111010. При Т = 1 выполняет одну команду, находящуюся по адресу, хранящемуся в PC.

Кнопка «Сброс» - сбрасывает процессор в исходное состояние.

Пример отображения информации приведен на рисунке.

На данном рисунке приведен пример выполнения простейшей программы: запись двух значений в регистры RG0 и RG1 и запись их разности в регистр RG2. Кроме того, значения ячеек памяти команд отображаются в двоичном виде, таким образом можно непосредственно видеть код команды.

При неправильно введенной команде выдается сообщение о том, что данная команда не существует:

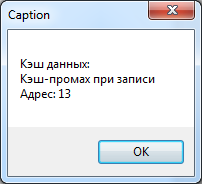

При установленной галке «Показывать результат обращения к кэшу» может выдаваться сообщение следующего вида: