- •21 Основные режимы адресации бму серии к584

- •22Функции адресации в режимах ркс и ркм. Базово-принудительная адресация.

- •00...01

- •00...01

- •23 Функции адресации в режимах ркс и ркм. Принудительно-относительные адресации.

- •24 Функции адресации в режимах ркс и ркм. Адресации впм и вызова микропроцедуры

- •25 Общие понятия об интерфейсных средствах микроЭвм. Понятие о техническом интерфейсе. Пример шинного формирователя.

- •Пример шинного формирователя.

- •26 Организация магистрального приемо-передатчика серии к584. Пример магистрального приемо-передатчика серии к584вв1 (мпп).

- •27 Общие принципы организации блоков синхронизации цвм.

- •28 Пример интегрального блока контроллера синхронизации серии к583.

- •29 Временная диаграмма работа блока контроллера синхронизации на базе к583.

- •30 Структурная организация микроЭвм с микропрограммным управлением. Назначение функциональных устройств и блоков.

- •31 Структурная организация микроЭвм с мк управлением. Организация микрокомандного цикла. Типовые циклы функционирования микроЭвм

- •32 Структурная организация микроЭвм с мк управлением. Организация командного цикла. Типовые циклы функционирования микроЭвм

- •33 Понятие о режиме прерывания в вычислительной системе. Реализация режима мэвм с мк управлением.

- •34 Понятие о режиме прямого доступа к памяти. Реализация режима микроЭвм с мк управлением. Режим прямого доступа к памяти (пдп).

- •35 Общее понятие о командном управлении. Терминология. Пример структуры цвм с командным управлением.

- •36 Понятие о системе команд. Команды с постоянной длиной формата.

- •37 Команды с переменно длиной формата.

- •Пример форматов команд переменной длины

- •38 Общее понятие об адресациях в командном цикле. Адресации к командам.

- •39 Общее понятие об адресациях в командном цикле. Адресация к операндам (прямая и относит).

- •40 Общее понятие об адресациях в командном цикле. Адресация к операндам (базов и косвенн).

- •41 Общее понятие об адресациях в командном цикле. Адресация к операндам (индексная и непосредственная).

- •42 Общее понятие об адресациях в командном цикле. Адресация к операндам (регистровая, явная, неявная, автоинкрементная, комбинированная).

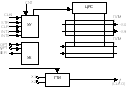

28 Пример интегрального блока контроллера синхронизации серии к583.

К онтроллер

строиться на базе двух ПЛМ (ПЛМ1, ПЛМ2),

циклического 10-ти разрядного регистра

сдвига (ЦРС), встроенного ГТИ, устройства

управления и устройства контроля. ГТИ

имеет входы Х1, Х2 для подключения внешнего

резонатора или источника внешнего поля

частоты и формирует тактовые импульсы

с макс. частотой 20МГц. В пределах периода

ГТИ возможна небольшая коррекция его

деятельности путем изменения потенциала

на поле подстройки.CLKO

подает на CLKI

в УУ, который воздействует на работу

ЦРС: по сигналу CLR-отчистка

– установка ЦРС в исходное состояние

(0 в младшем разряде); по сигналу STR

– старт – осуществляется запуск

циклического сдвига ЦРС с тактовой

частотой CLKI.

Сигналы INT1,

INT0

позволяют приостанавливать сдвиг на

четных и нечетных разрядах ЦРС. Выходные

шины ЦРС через ПЛМ1 подключают на выходы

полуфаз ¬S0-¬S9.

Эти импульсы являются унитарными

инверсными импульсами, на базе которых

с помощью внешней логики формируется

требуемая картина распределения

синхроимпульсов. Для циклического

повторения n-полуфаз

Sn-2

заводится на вход CNT

обратной связью, что позволяет варьировать

период в пределах от 2-х до 10-ти S.

Заданный цикл контролируется на ПЛМ2,

воздействующей на УК, для которого по

входам OPT1,

OPT0

задан тип цикла. Несоответствие

сопровождается сигналом ошибки ERR.

онтроллер

строиться на базе двух ПЛМ (ПЛМ1, ПЛМ2),

циклического 10-ти разрядного регистра

сдвига (ЦРС), встроенного ГТИ, устройства

управления и устройства контроля. ГТИ

имеет входы Х1, Х2 для подключения внешнего

резонатора или источника внешнего поля

частоты и формирует тактовые импульсы

с макс. частотой 20МГц. В пределах периода

ГТИ возможна небольшая коррекция его

деятельности путем изменения потенциала

на поле подстройки.CLKO

подает на CLKI

в УУ, который воздействует на работу

ЦРС: по сигналу CLR-отчистка

– установка ЦРС в исходное состояние

(0 в младшем разряде); по сигналу STR

– старт – осуществляется запуск

циклического сдвига ЦРС с тактовой

частотой CLKI.

Сигналы INT1,

INT0

позволяют приостанавливать сдвиг на

четных и нечетных разрядах ЦРС. Выходные

шины ЦРС через ПЛМ1 подключают на выходы

полуфаз ¬S0-¬S9.

Эти импульсы являются унитарными

инверсными импульсами, на базе которых

с помощью внешней логики формируется

требуемая картина распределения

синхроимпульсов. Для циклического

повторения n-полуфаз

Sn-2

заводится на вход CNT

обратной связью, что позволяет варьировать

период в пределах от 2-х до 10-ти S.

Заданный цикл контролируется на ПЛМ2,

воздействующей на УК, для которого по

входам OPT1,

OPT0

задан тип цикла. Несоответствие

сопровождается сигналом ошибки ERR.

29 Временная диаграмма работа блока контроллера синхронизации на базе к583.

Пусть по положительным фронтам тактовых импульсов CLKI осуществляется установка и сброс инверсных сигналов полуфаз с чётным номером (S0, S2, и так далее), а по отрицательным фронтам – полуфаз с нечётными номерами (S1, S3 и так далее). Тогда соседние полуфазы на выходах контроллера будут перекрываться на полпериода CLKI, что исключит появление импульсных помех при объединении сигналов на схемах дополнительной логики.

Н астроим

контроллер на цикл выработки десяти

полуфазS0,

…, S9,

подключив ко входу обратной связи SNT

выходной сигнал S7.

В этом случает период синхронизации

Т=5tCLKI

(5 периодов = 10 полупериодов). Учитывая

tCLKI=50нс,

получаем 5tCLKI=250нс.

астроим

контроллер на цикл выработки десяти

полуфазS0,

…, S9,

подключив ко входу обратной связи SNT

выходной сигнал S7.

В этом случает период синхронизации

Т=5tCLKI

(5 периодов = 10 полупериодов). Учитывая

tCLKI=50нс,

получаем 5tCLKI=250нс.

В случае необходимости останова или растяжения периода синхронизации Т в определённом моменте времени используется сигнал INT0, INT1. INT0 оказывает воздействие в виде приостанова на чётных полуфазах, INT1 – на нечётных.

Требуемые для синхронизации импульсы SYNC формируются на полуфазах путём объединения их на схеме импульса. Требуемые диаграммы синхронизации устройства будут осуществляться с точностью ±25нс.

Если для формирования временной диаграммы недостаточно 10 полуфаз S0, …, S9, может быть выбрано два контроллера (20 полуфаз) и так далее. Контроллеры соединяются последовательно по схеме. Выход S7 предыдущего подключается ко входу CNT последующего.

Выход Si последнего контроллера заводится на CNT первого. В качестве опорного генератора используется встроенный генератор одного из контроллеров.

30 Структурная организация микроЭвм с микропрограммным управлением. Назначение функциональных устройств и блоков.

Типовая схема простейшего микро ЭВМ

В состав микро ЭВМ входят средства операционной части, управляющей части, системные устройства.

В частности, к операционной части относятся: блок микропроцессоров (БМП) со схемами ускоренного переноса (СУП), постоянно запоминающее устройство констант (ПЗУК), оперативная память расширенного регистра файлов (ОПР), табличные преобразователи (ТП), функциональные преобразователи (ФП), возможно наличие буферных регистров для временного хранения информации (БР).

К управляющей части относятся: блок микропрограммного управления (БМУ), контроллер состояний (КС), управляющая память (УП).

К системным устройствам относятся: (БППР), контроллеры прямого доступа к памяти (КПДП), средства внешнего интерфейса на базе блока магистрального приёмо-передатчика (БМПП), управляющая память (УП) командного уровня и прочее.

Структура микро ЭВМ определяется теми задачами, которые на неё возлагают. В общем случае, микро ЭВМ может организовываться по магистральному типу, по радиальному или смешанному.

Магистральный тип предполагает наличие шин внутреннего интерфейса, предназначенных для передачи информации между группой приёмников и группой источников в режиме разделения времени. В конкретный момент в магистрали осуществляется передача от конкретного источника конкретному приёмнику в интервале времени. В другие интервалы реализуются иные передачи. Направлением передачи может быть одно- и двунаправленным. Магистрали могут быть многофункциональными (реализуют определённый тип передачи определённой функциональной информации), многофункциональные (когда во времени разделяются различные типы передачи информации).

Магистральные структуры бывают двухмагистральными (магистраль двунаправленных данных и магистраль управления); трёхмагистральные (двунаправленная, адресная, управления); четырёхмагистральная (данные выхода, данные входа, управление, адресная).

В радиальных структурах передача по той или иной шине функционально закреплена за определённым источником и определённым приёмником.

Магистральный тип обеспечивает простоту реализации и технологичность изготовления микро ЭВМ. Но имеет пониженные скоростные характеристики из-за разделения времени работы между различными функциональными передатчиками. Радиальные – обеспечивают максимальную скорость передачи, но менее технологичные, обычно в интегральном исполнении, имеют более высокую стоимость.

В БМП может входить одна или несколько процессорных секций в зависимости от разрядности микро ЭВМ. В последнем случае для повышения быстродействия следует подключать СУП, которые обрабатывают межсекционные выходные переносы, общий входной перенос и формирует межсекционные входные переносы и общий выходной перенос БМП-ВП. БМП может формировать логические условия в соответствии с состоянием своих устройств.

К584 имеет разделённую входную шину, выходную и шину адреса. Управление микропрограммно по шине микроинструкций (ШМИ). Это позволяет использовать его в четырёхмагистральной системе, либо в трёхмагистральной системе, когда шина входа и шина выхода объединяются, что возможно из-за реализации шины выхода по схеме с открытым коллектором. ПЗУК содержит требуемые рабочие константы и имеет соответственно шину микроинструкций, задающую адрес константы и режим чтения и выходную шину данных, с которой константы через магистраль входа может загружаться на шины входа БМП.

Оперативная память расширителя (ОПР) является выносным регистровым файлом БМП и используется в том случае, если для решения задачи недостаточно внутренних регистров БМП.

Микроинструкция ОПР будет содержать адрес конкретной ячейки и управление операцией записи или чтения в этой ячейке. Записанная информация поступает с магистрали выхода (МВ), куда подаётся с шины выхода (ШВ). Считанная информация представляется на магистраль входа (МВх) и далее на шину входа (ШВх).

Адресное обращение у ПЗУК и ОПР идёт по фиксированным адресам, адреса жёстко заданы в микрокоманде.

ТП и ФП различного типа используются, если необходимо повысить производительность БМП и позволяют за два цикла работы БМП (1 – выдача данных с БМПП в БР; 2 – опрос ТП или ФП и приём результатов в БМП) реализовать любое функциональное преобразование.

Управляющая часть (УЧ) строится на основе контроллера состояний (КС), в функции которого фиксация условий микрокомандного цикла, командного цикла, хранение этих условий и формирование на их основе сигналов модификации М0, М1.

Кроме этого КС содержит таймеры для счёта временных интервалов, средств побитовой обработки данных и других операций УЧ.

В простейшем случае КС может быть заменён мультиплексором условий.