- •Работа над ошибками

- •Три основные подсистемы вычислительной системы

- •Назначение основных разрядов флагового регистра

- •Назначение указателя стека

- •Понятие суперскалярной архитектуры

- •Шина pci – общие сведения

- •Режимы работы запоминающего элемента

- •Триггер – общие сведения

- •Основные характеристики интерфейсов.

- •Передача данных по параллельному интерфейсу.

- •Список используемой литературы:

Назначение основных разрядов флагового регистра

Девять из 16 бит флагового регистра являютсяактивными и определяют текущее состояние машины и результаты выполнения команд. Многие арфметические команды и команды сравнения изменяют состояние флагов.

|

Флаг |

Назначение |

|

O(Переполнение) |

Указывает на переполнение старшего бита при арифметических командах |

|

D(Направление) |

Обозначает левое или правое направление пересылки или сравнения строковых данных (данных в памяти, превышающих длину одного слова) |

|

I(Прерывание) |

Указывает на возможность внешних прерываний |

|

T(Пошаговый режим) |

Обеспечивает возможность работы процессора в пошаговом режиме |

|

S(Знак) |

Содержит результирующий знак после арифметических операций (0-плюс, 1-минус) |

|

Z(Ноль) |

Показывает результат арифметических операций и операций сравнения (0 – ненулевой, 1-нулевой результат) |

|

A(Внешний перенос) |

Содержит перенос из 3-го бита для 8-битовых данных. Используется для специальных арифметических операций |

|

P(Контроль четности) |

Показывает четность младших 8-битовых данных (1-четное, 0-нечетное число) |

|

С (перенос) |

Содержит перенос из старшего бита после арифметических операций, а также последний бит при сдвигах или циклических сдвигах |

Назначение указателя стека

Регистр SP– указатель стека обеспечивает использование стека в памяти, позволяет временно хранить адреса и иногда данные. Этот регистр связан с регистромSSдля адресации стека.

Регистр BP– указатель базы облегчает доступ к параметрам (данным и адресам, переданным через стек).

Понятие суперскалярной архитектуры

Термин «суперскалярная» обозначает микропроцессорную архитектуру, которая содержит более одного вычислительного блока. Эти вычислительные блоки (конвейеры ) являются узлами, где происходят все основные процессы обработки данных и команд.

Появление суперскалярной архитектуры процессора Pentiumявилось логическим развитием семейтсва процессоровIntel. Например, процессор 80486 способен выполнять несколько команд за один период тактовой частоты, однако предыдущие семейства процессоров фирмIntelтребовали множество циклов тактовой частоты для выполнения одной команды (от 3 до 180).

Выполнение множества команд за один период тактовой частоты возможно благодаря наличию двух конвейеров, которые могут выполнять две инструкции одновременно. Двойной конвейер процессора Pentiumпозволяет нескольким командам находиться в различных стадиях выполнения, увеличивая тем самым общую производительность. Каждый конвейер имеет свое АЛУ, совокупность усройств генерации адреса и интерфейс кэширования данных. В случае выполнения сложных команд используются оба конвейера.

Шина pci – общие сведения

Шина PCI(PeripheralComponentInterconnect) созданаIntelв 1993 году как новая разработка шиныVESA. Она, как иVESA, обеспечивает скорость работы 132М/сек (максимальная частота – 66 МГц). При разработке шины было уделено особое внимание рабте с периферией, высокоскоростным приложениям для процессораPentium. СпецификацияPCIпозволяет обеспечить большую гибкость и быстродейтсвие шины, но предпологает значительные аппаратные затраты, что увеличивает стоимость системной платы.

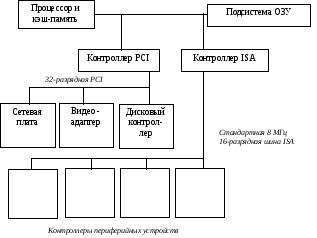

К шине PCIможно подключить до 10 периферийных устройств, но разъемов расширения при этом можно использовать не более трех: каждая плата расширенияPCIможет разделяться между двумя периферийными устройствами, и несколько таких устройств можно разместить на самой системной плате (т.н. втроенные контроллеры). ШинаPCIявляется процессорно-независимой (т.е. используется не только с процессорамиIntel). Структура шина на рисунке 2.

Р ис.2

Структура шиныPCI

ис.2

Структура шиныPCI