Шпоры по АиЛОВТ

.doc|

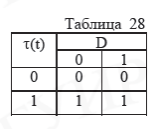

Приняты следующие изображения входов триггеров: S − раздельный вход установки триггера в единичное состояние по прямому выходу; R − раздельный вход сброса триггера в нулевое состояние по прямому выходу; J и K − назначение аналогично входам S и R; D − информационный вход. Используется для приема информации, записываемой в триггер; T − счетный вход; С − вход синхронизации.

|

D τ |

T

|

|

RS-триггеры. Асинхронные RS-триггеры являются простейшими триггерами. Такие триггеры строятся на логических элементах: 2ИЛИ-НЕ – триггер с прямыми входами (рис. 41 ) или 2И-НЕ – триггер с инверсными входами. Выход каждого из логических элементов подключен к одному из входов другого элемента, что обеспечивает нахождение триггера в одном из двух устойчивых состояний.

Табл.30 определяет переходы RS-триггера по формуле τ(t+1)=τ(t)RVS.

|

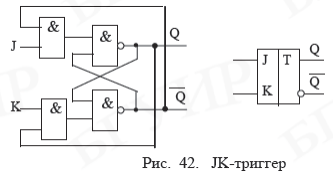

JK-триггеры. Асинхронный JK-триггер строится на базе RS-триггера.

JK-триггер имеет

два информационных входа. Простейший

JK-триггер можно получить из RS-триггера,

если ввести дополнительные обратные

связи с выходов триггера на входы,

которые позволяют устранить

неопределенность в таблице состояний.

Логическая схема и условное обозначение

JK-триггера приведены на рис.42.

Табл. 31 определяет переходы JK-триггера согласно логической формуле τ(t+1)= τ(t)J V τ(t) K.

|

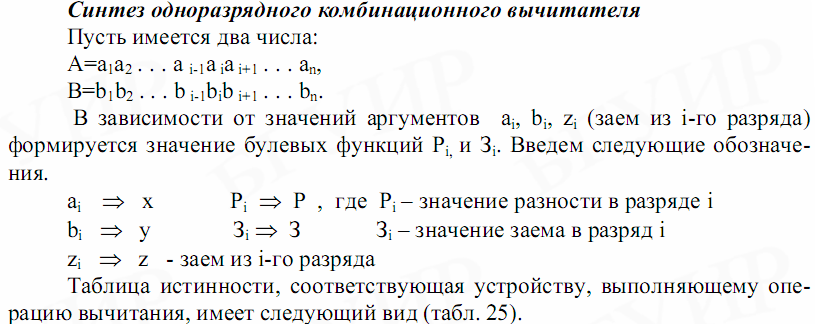

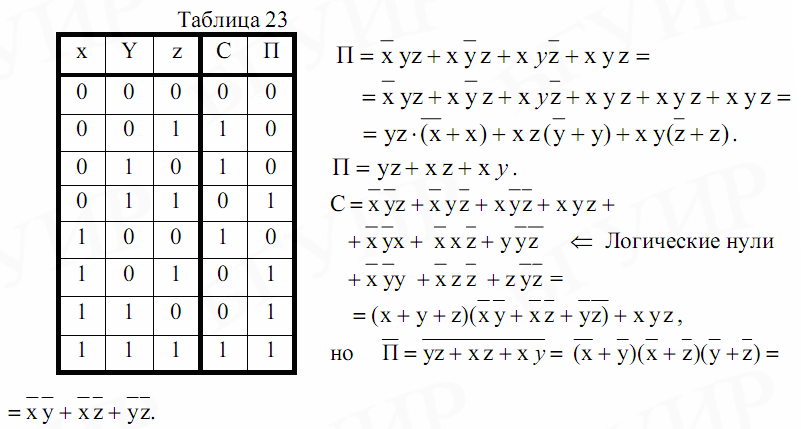

Синтез одноразрядного полного комбинационного сумматора

|

|

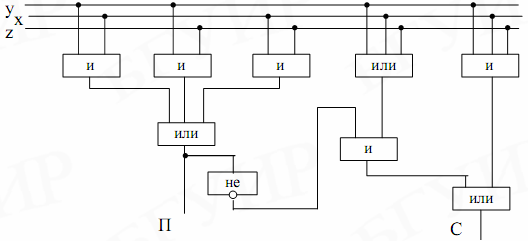

Синтез одноразрядного комбинационного полусумматора О

|

|

|

|

Объединенная схема одноразрядного комбинационного сумматора-вычитателя Для системы булевых функций C, P, П и З, полученных выше, может быть построена логическая схема (рис. 34) на элементах И, ИЛИ и НЕ.

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

-триггер.

Принцип работы синхронного D-триггера

основан на том, что сигнал на выходе

после переключения равен сигналу на

входе D до переключения. На рис. 39

приведена схема одноступенчатого

D-триггера на элементах И-НЕ и его

условное изображение.

-триггер.

Принцип работы синхронного D-триггера

основан на том, что сигнал на выходе

после переключения равен сигналу на

входе D до переключения. На рис. 39

приведена схема одноступенчатого

D-триггера на элементах И-НЕ и его

условное изображение. (t+1)=

τ(t)С

V DC

(t+1)=

τ(t)С

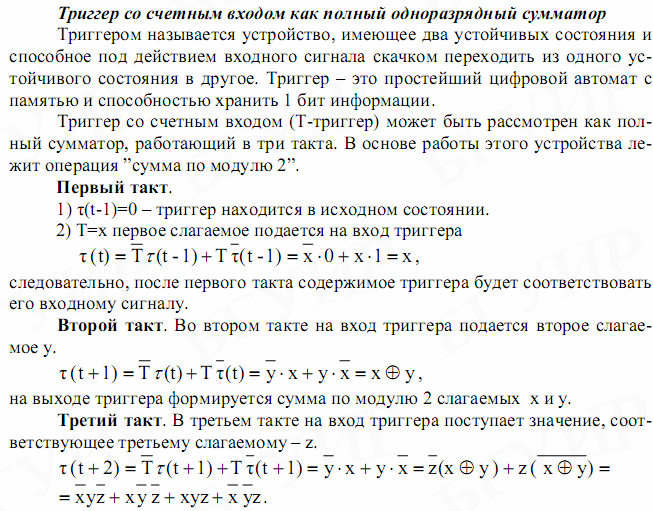

V DC -триггер

единичный сигнал на входе изменяет

содержимое триггера на противоположное

Переключение состояний выполняется

по формуле τ(t+1)=

τ(t)

-триггер

единичный сигнал на входе изменяет

содержимое триггера на противоположное

Переключение состояний выполняется

по формуле τ(t+1)=

τ(t)

дноразрядный

полусумматор − это устройство для

сложения разрядов двух чисел без

учета переноса из предыдущего

разряда, имеющее два входа (два

суммируемые разряды) и два выхода

(суммы и переноса). Таблица истинности,

отражающая алгоритм работы полусумматора,

имеет следующий вид (табл. 24).

дноразрядный

полусумматор − это устройство для

сложения разрядов двух чисел без

учета переноса из предыдущего

разряда, имеющее два входа (два

суммируемые разряды) и два выхода

(суммы и переноса). Таблица истинности,

отражающая алгоритм работы полусумматора,

имеет следующий вид (табл. 24).