Лабораторная работа №4.

Задания.

-суммирующего счётчика на D-триггерах.

При использовании D-триггеров в качестве счетных, его инверсный выход соединяют со своим входом D. Суммирующий асинхронный счетчик на D триггерах получается, если инверсный выход предыдущего триггера соединить со входом С последующего триггера.

-асинхронный суммирующий счетчик на JK-триггерах

Синхронизирующие входы всех триггеров,кроме крайнего левого (Т1), соединены с прямыми выходами предыдущих триггеров. Поэтому состояние триггера меняется в ответ

на изменение состояния предыдущего триггера.

Таблица состояний на прямых выходах триггеров.

|

N |

Q3 |

Q2 |

Q1 |

Q0 |

|

0 |

0 |

0 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

|

2 |

0 |

0 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

|

4 |

0 |

1 |

0 |

0 |

|

5 |

0 |

1 |

0 |

1 |

|

6 |

0 |

1 |

1 |

0 |

|

7 |

0 |

1 |

1 |

1 |

|

8 |

1 |

0 |

0 |

0 |

|

9 |

1 |

0 |

0 |

1 |

|

10 |

1 |

0 |

1 |

0 |

|

11 |

1 |

0 |

1 |

1 |

|

12 |

1 |

1 |

0 |

0 |

|

13 |

1 |

1 |

0 |

1 |

|

14 |

1 |

1 |

1 |

0 |

|

15 |

1 |

1 |

1 |

1 |

Управление триггерами выполняем задним фронтом счетных импульсов.

Временные диаграммы, поясняющие работу асинхронного суммирующего счетчика.

- асинхронный вычитающий на JK-триггерах

- синхронный

суммирующий

синхронный

суммирующий

В синхронном последовательном счетчике синхроимпульсы поступают на все триггеры счетчика параллельно, а управляющие импульсы от предыдущего разряда к последующему – последовательно, что несколько уменьшает его быстродействие.

-счетчик Джонсона. Для получения схемы счетчика Джонсона необходимо соединить инверсный выход старшего разряда регистра с входом младшего.

-реверсивный асинхронный счётчик(. Управление направлением счёта организовать с помощью управляющего триггера).

В некоторых случаях необходимо, чтобы счетчик мог работать как в прямом, так и в обратном направлении счета. Такие счетчики называются реверсивными. Реверсивные счетчики могут быть как асинхронного, так и синхронного типа. Они строятся путем применения логических коммутаторов (мультиплексоров) в цепях связи между триггерами. Так, например, асинхронный реверсивный двоичный счетчик можно построить, если обеспечить подачу сигналов с прямого (при суммировании) или с инверсного (при вычитании) выхода пре-дыдущего JK- или Т-триггера на счетный вход последующего. В случае, когда реверсивный счетчик строится на базе D-триггеров, управляемых передним фронтом, для получения режима прямого счета следует соединить инверсный выход предыдущего с счетным входом последующего триггера.

. Управление направлением счёта организовать с помощью управляющего триггера.

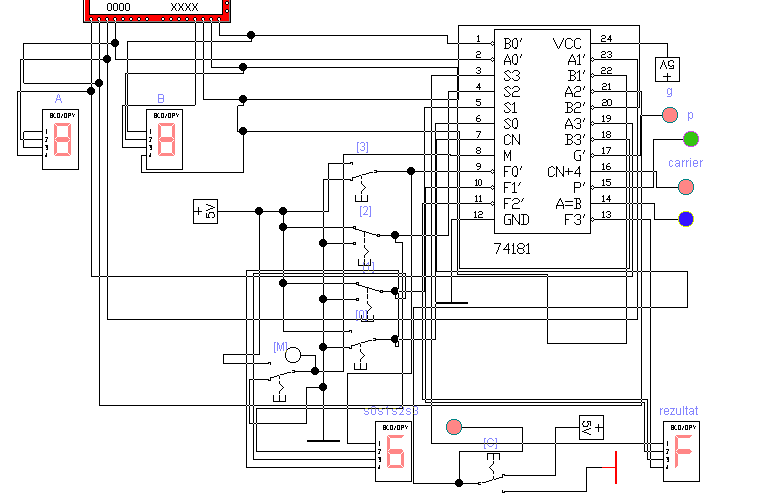

АЛУ.

|

S3 |

S2 |

S1 |

S0 |

Логическая функция М=1 |

Арифметико-логическая функция М=0, С'=1 (входной перенос отсутствует) |

|

0 |

0 |

0 |

0 |

А' |

A или А+1 (вх.перенос ) |

|

0 |

0 |

0 |

1 |

(A+B)' |

A+B или A+B+1 |

|

0 |

0 |

1 |

0 |

A' B |

A+B' или (A+B')+1 |

|

0 |

0 |

1 |

1 |

0 |

-1 или 0 при переносе |

|

0 |

1 |

0 |

0 |

(AB)' |

A+AB' или (A+AB')+1 |

|

0 |

1 |

0 |

1 |

B' |

(A+B)+AB' или ((A+B)+AB')+1 |

|

0 |

1 |

1 |

0 |

A EB искл. ИЛИ |

A-B-1 или A-B |

|

0 |

1 |

1 |

1 |

AB' |

AB'-1 или AB' |

|

1 |

0 |

0 |

0 |

A'+B |

A+AB или A+B+1 |

|

1 |

0 |

0 |

1 |

(A+B)' |

A+B или A+B+1 |

|

1 |

0 |

1 |

0 |

B |

(A+B')+ABили (A+B')+AB+1 |

|

1 |

0 |

1 |

1 |

AB |

AB-1 или AB |

|

1 |

1 |

0 |

0 |

1 |

A+A или A+A+1 |

|

1 |

1 |

0 |

1 |

A+B' |

(A+B)+A или (A+B)+A |

|

1 |

1 |

1 |

0 |

A+B |

(A+B')+A или (A+B')+A+1 |

|

1 |

1 |

1 |

1 |

A |

A-1 или A |

Например.

На рисунке приведена схема троичного одноразрядного трёхбитного одноединичного бинарного АЛУ. Устройство состоит из дешифратора "два трёхбитных одноединичных трита в один девятибитный одноединичный трит" на девяти логических элементах "2И", девяти демультиплексоров (переключателей) DMX "1 на 3" управляемых одним трёхбитным одноединичным тритом и одного девятитритного регистра RG. На входы T1 и Т2 подаются трёхбитные одноединичные триты двух операндов, в девятитритный регистр номера функции RG по стробу на входе C загружается девятитритный трёхбитный одноединичный код номера операции (номера троичной функции), который переключает девять демультиплексоров DMX для выполнения требуемой троичной бинарной функции с унарным выходом. Устройство выполняет любую из 3^9=19 683 одноразрядных троичных бинарных функций с унарным выходом, в том числе и логическое сложение по модулю 3.

Контрольные вопросы.