- •1) Комбинационная логика, основные элементы (и, или, не), их схемы на кмоп транзисторах.

- •Временная диаграмма работы сдвигового регистра.

- •6) Общая структура микроконтроллерного устройства, алу, программный счётчик.

- •Общая структура микроконтроллерного устройства (из интернета)

- •Программный счётчик.

- •7. Виды памяти микроконтроллеров (на примере семейства avr). Стек и его инициализация.

- •8. Прерывания, вектор прерываний.

- •9) Основы языка Assembler для микроконтроллеров семейства avr. Синтаксис, классификация команд.

- •Команды логических операций.

- •Команды операций с битами.

- •Команды пересылки данных.

- •Команды передачи управления.

- •Команды управления системой.

- •10. Регистры ввода-вывода. Схема устройства вывода микроконтроллера, управляющие регистры, режимы работы.

- •Источники тактовой частоты

- •Управляющие регистры таймера

- •Прерывания таймера

- •3. Цифро-аналоговые преобразователи. Структурная схема цап. Параллельная схема суммирования токов. Последовательная схема суммирования токов.

- •Классификация ацп

- •5. Структурная схема встроенного аналого-цифрового преобразователя, его основные параметры. Настройка ацп, управляющие регистры. Прерывания по завершению цикла преобразования.

- •17. Передача данных с использованием асинхронного последо-вательного интерфейса spi. Схема организации spi интерфейса, сдвиговые регистры. Пакетная передача данных.

- •18) Интерфейс i2c. Протокол передачи данных, режимы работы. Основные преимущества и недостатки интерфейса.

1) Комбинационная логика, основные элементы (и, или, не), их схемы на кмоп транзисторах.

Комбинационная схема – логическая схема, сигнал на выходе которой определяется только уровнями сигналов на ее входах. Такой подход построения схем называется комбинационной логикой.

Логические элементы – устройства, предназначенные для обработки информации в цифровой форме (последовательности сигналов высокого «1» и низкого «0» уровней).

Основные логические элементы

1) Вентиль И (AND)

|

|

Если хоть на одном входе «0», то на выходе – «0» |

2)

Вентиль

ИЛИ (OR) |

|

Если хоть на одном вентиле «1», то на выходе – «1» |

3) Вентиль НЕ (NOT) – инвертор |

|

Сейчас почти все строится с помощью инверторов. Если взять И-НЕ или ИЛИ-НЕ, то соединив входы получим инвертор |

Схемы на КМОП транзисторах

Повторение на тему ПОЛЕВЫЕ ТРАНЗИСТОРЫ

0 – блокирует n-канальный транзистор 1 – открывает n-канальный транзистор

(с р-канальным все наоборот) |

n-канальный – стрелка к затвору p-канальный – стрелка от затвора |

В основе ЛЭ на ПТ лежат инверторы (ключи). Рассмотрим логические элементы И-НЕ и ИЛИ-НЕ, а также инвертор.

1) Вентиль И-НЕ (и + инвертор) на КМОП-транзисторах (NAND)

|

Пример: На входе А и В «1»: Tр1 –закрыт; Tр2 – закрыт; Tn1 –открыт; Tn2 – открыт, поэтому на выходе «0» Таблица истинности:

|

2) Вентиль ИЛИ-НЕ (или + инвертор) на КМОП-транзисторах (NOR)

|

Пример: На входе А и В «1»: Tр1 –закрыт; Tр2 – закрыт; Tn1 –открыт; Tn2 – открыт, поэтому на выходе «0» Таблица истинности:

|

3) Вентиль НЕ на КМОП-транзисторах

|

1. На входе «1», VT1 – закрыт; VT2 – открыт, поэтому на выходе «0»

2. На входе «0», VT1 – открыт; VT2 – закрыт, поэтому на выходе «1» |

Объянение как работает инвертор (картинка В и Г):

2) RS-триггер. Простейший триггер на биполярных транзисторах. RS-триггер на логических элементах И-НЕ, ИЛИ-НЕ. Синхронный RS триггер.

Триггер – устройство, обладающее способностью длительно находиться в одном из 2-х устойчивых состояний и чередовать их под воздействием внешних сигналов.

Свойство «запоминания» двоичной информации – способность оставаться в одном их 2-х состояний (помнит «1» или «0»)

При включении питания триггер непредсказуемо принимает одно из двух состояний.

Триггер на биполярных транзисторах

Схема устройства представляет собой каскады, выполненные на транзисторах. Вход каждого из них подключается к выходу противоположного.

Пусть в начальный момент времени VT2 закрыт. Под действием напряжения на его коллекторе через Rб3 протекает ток, удерживающий VT1 в открытом состоянии. В то же время открытый VT1 закорачивает базовую цепь транзистора VT2 с резистором Rб4. Закрытое состояние VT2 соответствует значению выхода Q=1. Открытое

состояниеVT1

Напряжение на коллекторе закрытого транзистора (Q=1) равно: UQ=Uп×Rб3/(RК2+Rб3) |

Для того, чтобы сменить состояние триггера на противоположное, необходимо подать сигналы на вход R или S. Входные сигналы обычно являются импульсными. Наличие напряжения на входе S (S=1) устанавливает Q=1, а наличие напряжения на входе R (R=1) устанавливает Q=0. Одновременная подача сигнала на входы S и R запрещена, т.к. триггер при этом перестаёт быть триггером (не будет противоположного состояния Q и ). |

|

Диаграммы работы при наличии входных импульсных сигналов. На интервале между импульсами на входах S и R триггер помнит то состояние, в которое он был установлен по этим входам, т.е. триггер - элемент памяти. |

Триггер на логических элементах

RS триггер получил название по названию своих входов.

Вход S (Set –установка) позволяет устанавливать выход триггера Q в единичное состояние (записывать единицу). Вход R (Reset – сброс) позволяет сбрасывать выход триггера Q в нулевое состояние (записывать ноль).

У триггера два выхода Q – прямой и – инверсный. Состояние триггера определяется состоянием прямого выхода.

RS-триггер собирается на базе двух логических элементов: ИЛИ-НЕ и И-НЕ. Различие в том, что триггер на элементах И-НЕ переводится в другое состояние потенциалом логического нуля (активный уровень – низкий). Триггер, собранный на элементах ИЛИ-НЕ активируется логической единицей (активный уровень – высокий)

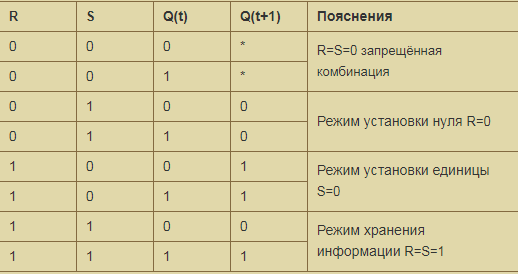

Для описания работы триггера используют таблицу состояний (переходов, истинности).

Опишем принцип работы RS-триггера, собранного на элементах ИЛИ-НЕ.

Если на R подаем активный уровень, то на выходе будет «0»

Если на S подаем активный уровень, то на выходе будет «1»

Состояние 0-0 – хранение предыдущего состояния Состояние 1-1 – неопределенность |

Q(t) – состояние триггера до поступления управляющих сигналов (изменения на входах R и S); Q(t+1) – состояние триггера после изменения на входах R и S.

|

Пусть R=0, S=1. Нижний логический элемент выполняет логическую функцию ИЛИ-НЕ, т.е. «1» на любом его входе приводит к тому, что на его выходе будет логический ноль =0. На выходе Q будет «1», т.к. на оба входа верхнего элемента поданы нули (один ноль – со входа R, другой – с выхода ). Триггер находится в единичном состоянии.

Если теперь убрать сигнал установки (R=0, S=0), на выходе ситуация не изменится, т.к. несмотря на то, что на нижний вход нижнего логического элемента будет поступать 0, на его верхний вход поступает 1 с выхода верхнего логического элемента. Триггер будет находиться в единичном состоянии, пока на вход R не поступит сигнал сброса.

Пусть теперь R=1, S=0. Тогда Q=0, а =1. Триггер переключился в "0". Если после этого убрать сигнал сброса (R=0, S=0), то все равно триггер не изменит своего состояния.

Опишем принцип работы RS-триггера, собранного на элементах И-НЕ.

Входы R и S инверсные (активный уровень "0"). Переход (переключение) этого триггера из одного состояния в другое происходит при установке на одном из входов "0". Комбинация R=S=0 является запрещённой.

Синхронный RS-триггер

Так как управляющие сигналы могут приходить как им вздумается, был предложен синхронный RS-триггер (добавлена схема синхронизации), т.е. переключение будет только если имеется синхронизированный сигнал.

3) Статический D триггер, схема, принцип работы. Таблица истинности D триггера. Принципиальная схема статического D триггера на элементах И-НЕ, ИЛИ-НЕ. Динамические D триггеры. Временные диаграммы работы D триггера.

D-триггером называется триггер с одним информационным входом, работающий так, что сигнал на выходе после переключения равен сигналу на входе D до переключения, т. е. Qn+1=Dn Основное назначение D-триггеров - задержка сигнала, поданного на вход D. Он имеет информационный вход D (вход данных) и вход синхронизации С. Вход синхронизации С может быть статическим (потенциальным) и динамическим. У триггеров со статическим входом С информация записывается в течение времени, при котором уровень сигнала C=1. В триггерах с динамическим входом С информация записывается только в течение перепада напряжения на входе С. Динамический вход изображают на схемах треугольником. Если вершина треугольника обращена в сторону микросхемы (прямой динамический вход), то триггер срабатывает по фронту входного импульса, если от нее (инверсный динамический вход) - по срезу импульса. В таком триггере информация на выходе может быть задержана на один такт по отношению к входной информации.

Если уровень сигнала на входе С = 0, состояние триггера устойчиво и не зависит от уровня сигнала на информационном входе D. При подаче на вход синхронизации уровня С = 1 информация на прямом выходе будет повторять информацию, подаваемую на вход D. Следовательно, при C=0 Qn+1=Qn, а при C=l Qn+1=Dn.

Мои комментарии:

Черта / или \ у С-входа триггера означает, что динамический триггер работает либо по фронту входного импульса (началу), либо по срезу (концу). Чаще используют аналогичные изображения треугольника, повернутые в сторону триггера или же от него.

На рисунке 1 изображена схема D-триггера в базисе И, она нам не нужна, необходимые схемы указаны на рисунках 2 и 3.

Прозрачная защелка –то же самое, что и статические триггер, Триггер задержки – альтернативное название динамическому триггеру.

Выдержка из конспекта: может хранить 1 бит информации, из нескольких D-триггеров можно собрать регистр.

Рисунок 1 – Временные диаграммы работы D-триггера, таблица истинности, условное обозначение динамического D-триггера (от статического отличается чертой «/»у C-входа)

Рисунок 2 – Схема D-триггера в базисе И-НЕ

Рисунок 3 – Схема D-триггера в базисе ИЛИ-НЕ

4) T-триггер (счетный триггер). Схема T триггера (на основе D триггера). 4-битный суммирующий счётчик на основе T-триггеров, его временная диаграмма. 4-битный вычитающий счётчик на основе T-триггеров, его временная диаграмма.

Выдержка из конспекта: D-триггер с динамическим входом C может работать как T-триггер. Для этого необходимо вход С соединить с инверсным выходом триггера /Q. Из T-триггера можно собрать счетчик. Зная длительность импульса, можно настраивать промежутки времени (мигание светодиода)

Рисунок 4 – Преобразование D-триггера в T-триггер и его временная диаграмма работы

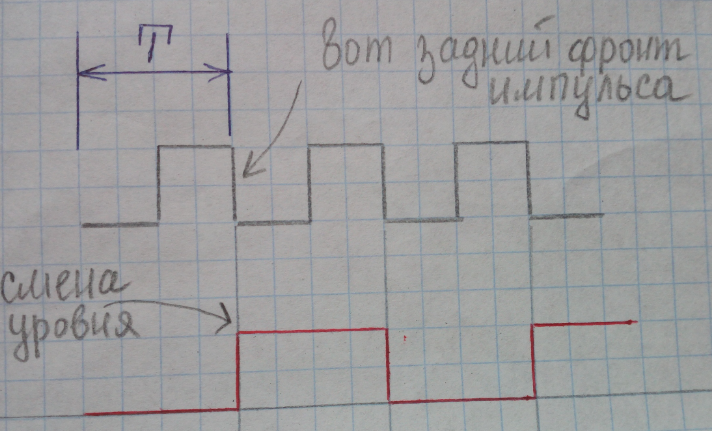

Из динамического D-триггера можно собрать Т-триггер: вход триггера – тактовый (С), а вход данных (D) объединен с инвертированным выходом. У такого триггера имеется только один вход. Когда подается входной тактовый импульс, выход переключается по заднему фронту.

Рисунок 5 – Схематическое изображение T-триггера

Принцип работы T-триггера

После поступления на вход T импульса, состояние триггера меняется на прямо противоположное. Счётным он называется потому, что T-триггер как бы подсчитывает количество импульсов, поступивших на его вход.

Жаль только, что считать этот триггер умеет только до одного. При поступлении второго импульса T-триггер снова сбрасывается в исходное состояние.

|

Q переключается по заднему фронту С.

Это своего рода «делитель частоты (сигнала)»

|

Рисунок 6 – Что такое фронт (на всякий случай)

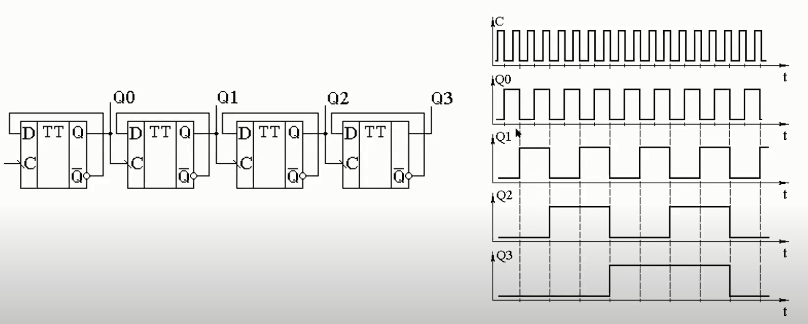

Счетчик – устройство, совокупность сигналов на выходе которого в определенном коде отображает число импульсов, поступивших на его вход.

Объединяя Т-триггеры получаем счетчики (или суммирующие или вычитающие). Триггеры соединяют последовательно, так, чтобы выход предыдущего был подключен ко входу последующего.

Количество подсчитанных импульсов NMAX = 2m, m – количество триггеров.

4-битный суммирующий счётчик на основе T-триггеров, его временная диаграмма

Схема счётчика, позволяющего посчитать любое количество импульсов, меньшее шестнадцати, приведена на рисунке ниже. Количество поступивших на вход импульсов можно узнать, подключившись к выходам счётчика Q0 … Q3. Это число будет представлено в двоичном коде.

Рисунок 7 – 4 битный суммирующий счетчик на основе T-триггеров

Пусть первоначальное состояние всех триггеров счётчика будет нулевым. Это состояние мы видим на временных диаграммах. Запишем его в таблицу 1. После поступления на вход счётчика тактового импульса (который воспринимается по заднему фронту) первый триггер изменяет своё состояние на противоположное, то есть единицу. Запишем новое состояние выходов счётчика в ту же самую таблицу.

Так как по приходу первого импульса изменилось состояние первого триггера, то этот триггер содержит младший разряд двоичного числа (единицы). В таблице поместим его значение на самом правом месте, как это принято при записи любых многоразрядных чисел.

Подадим на вход счётчика ещё один тактовый импульс. Значение первого триггера снова изменится на прямо противоположное. На этот раз на выходе первого триггера, а значит и на входе второго триггера сформируется задний фронт. Это означает, что второй триггер тоже изменит своё состояние на противоположное.

Продолжая анализировать временную диаграмму, можно определить, что на выходах приведённой схемы счётчика последовательно появляются цифры от 0 до 15. Эти цифры записаны в двоичном виде. При поступлении на счётный вход счётчика очередного импульса, содержимое его триггеров увеличивается на 1. Поэтому такие счётчики получили название суммирующих двоичных счётчиков.

Таблица 1 –Изменение уровней на выходе суммирующего счётчика при поступлении на его вход импульсов.

4-битный вычитающий счётчик на основе T-триггеров, его временная диаграмма

Счётчики могут не только увеличивать своё значение на единицу при поступлении на счётный вход импульсов, но и уменьшать его. Такие счётчики получили название вычитающих счётчиков. Для реализации вычитающего счётчика достаточно чтобы T-триггер изменял своё состояние по переднему фронту входного сигнала.

Изменить рабочий фронт входного сигнала можно инвертированием этого сигнала.

Рисунок 8 – 4 битный вычитающий счетчик на основе T-триггеров

По диаграмме видно, что при поступлении на вход счётчика первого же импульса на выходах появляется максимально возможное для четырёхразрядного счётчика число. При поступлении следующих импульсов содержимое счётчика уменьшается на единицу.

Это вызвано тем, что при поступлении переднего фронта тактового импульса первый триггер переходит в единичное состояние. В результате на его выходе тоже формируется передний фронт. Он поступает на вход второго триггера, что приводит к записи единицы и в этот триггер. Точно такая же ситуация складывается со всеми триггерами счётчика, то есть все триггеры перейдут в единичное состояние.

Следующий тактовый импульс приведёт к изменению состояния только первого триггера, так как при этом на его выходе сформируется задний фронт сигнала. Обратите внимание, что при поступлении каждого последующего импульса содержимое счётчика, построенного по анализируемой схеме, уменьшается на единицу.

Таблица 2 – Изменение уровней на выходе вычитающего счётчика при поступлении на его вход импульсов.

5) Регистры на основе D-триггеров. Параллельные регистры, последовательные (сдвиговые) регистры. Временная диаграмма работы сдвигового регистра.

Сдвиговый регистр построен на четырех D триггерах с динамической блокировкой входов. Для управления регистром сформированы:

вход С - вход синхронизации

вход R - общий сброс регистра.

Регистры на основе D-триггеров

На базе динамических Д-триггеров мы можем собрать регистры.

Единичный Д-триггер это простейшая ячейка памяти, которая способна хранить 1 бит информации. Поэтому есть смысл объединить динамические Д-триггеры в сборки по 4, 8 (столько разрядов и будет, 4-битный регистр и тд.).

Figure1 – слева-параллельные, справа-последовательные

Параллельные регистры

Все Д-триггеры объединены параллельно

На все входы подаем информацию

Тактовый импульс записывает новую информацию

Инф появляется на выходах

До появления нового синхроимпульса, новой порции данных старая будет сохраняться

Последовательные (сдвиговые) регистры.

Данные подаются только на 1-ый динамический Д-триггер

Сдвиговый регистр с последовательным входом – это устройство, в котором данные последовательно поступают на вход

Используются для преобразования последовательных данных в параллельный формат.

Figure2 – Типичный 4х разрядный регистр с последовательным входом

В данном случае используются D – триггеры. Работает регистр следующим образом.

В исходном положении импульс сброса (логический 0) подается на вход «Установка в 0», устанавливая выходы Q0-Q3 в 0.

Далее первый бит данных подается на последовательный вход.

При воздействии переднего фронта первого тактового импульса Q0 принимает значение равное D1.

Затем на последовательный вход подается D2.

При воздействии переднего фронта второго тактового импульса Q0=D2 и Q1=D1.

После четырех тактовых импульсов имеем Q0=D4, Q1=D3, Q2=D3, Q3=D1.

Выход данных при этом может быть как последовательным, так и параллельным. В последнем случае сдвиговый регистр работает как последовательно-параллельный преобразователь. Очевидно, для сдвиговых регистров, имеющих большое число разрядов (более восьми), параллельные выходы нецелесообразны из-за большого количества выходов в корпусе ИС. Существуют сдвиговые регистры, имеющие более 1000 разрядов.

=0.

=0.