6) Общая структура микроконтроллерного устройства, алу, программный счётчик.

В рамках единой базовой архитектуры 8-битные МК AVR подразделяются на 4 семейства:

Classic

устаревшие

Tiny

небольшой объем память 1-2 КБайта и ограниченная периферия

Mega

развитая периферия, расширенный объем данных (до 256 Кб) и программ

XMega

16-битные МК, развитая периферия (к примеру, встроенный 12-битный ЦАП, блок прямого доступа к памяти), наибольший объем памяти и повышенная тактовая частота (до 120 МГц)

Структура микроконтроллеров семейства Tiny.

Ядро микроконтроллеров AVR cемейства Тiny, как и ядро микроконтроллеров семейств Classic и Mega, выполнено по усовершенствованной RISC-архитектуре (Enchanced RISC), erо упрощенная схема представлена на рис. 1.1. Арифметико-логическое устройство (АЛУ), выполняющее все вычисления (т. е. предназначенное для выполнения арифметических и логических преобразований над данными - вычитание, сложение, умножение, сравнение, сдвиг данных) подключено непосредственно к 32 рабочим регистрам, объединенным в регистровый файл; B это так называемые оперативные регистры общего назначения (РОН). Доступ к этим ячейкам самый быстрый, а число операций с их содержимым наиболее разнообразное. Благодаря этому АЛУ выполняет одну операцию (чтение содержимого регистров, выполнение операции и запись результата обратно в регистровый файл) за один машинный цикл. Практически каждая из команд (за исключением команд, у которых одним из операндов является 16-разрядный адрес) занимает одну ячейку памяти программ. В микроконтроллерах AVR реализована Гарвардская архитектура, которая характеризуется раздельной памятью программ и данных, каждая из которых имеет собственные шины доступа к ним. Такая организация позволяет одновременно работать как с памятью программ, так и с памятью данных.

Разделение шин доступа позволяет использовать для каждого типа памяти шины различной разрядности, причем способы адресации и доступа к каждому типу памяти также различны. Еще одним решением, направленным на повышение быстродействия, является использование технологии конвейеризации. Конвейеризация заключается в том, что во время исполнения текущей команды производится выборка из памяти и дешифрация кода следующей команды. Причем, поскольку длительность машинного цикла микроконтроллеров AVR составляет всего один период тактового генератора, они могут обеспечивать ту же производительность, что и RISC-микроконтроллеры других фирм, но при более низкой тактовой частоте.

Рисунок 1 – Упрощенная схема МК ядра

Общая структура микроконтроллерного устройства (из интернета)

Типовая структура системы управления на основе микроконтроллера:

ФСУ – формирователи сигналов управления; ИУ – исполнительные

устройства; Д – датчики; ФСС – формирователи сигналов состояния

АЛУ

АЛУ — устройство, предназначенное для выполнения логических и математически операций над двоичными числами. АЛУ входит в состав любого микропроцессора.

ALU -Arithmetic Logic Unit

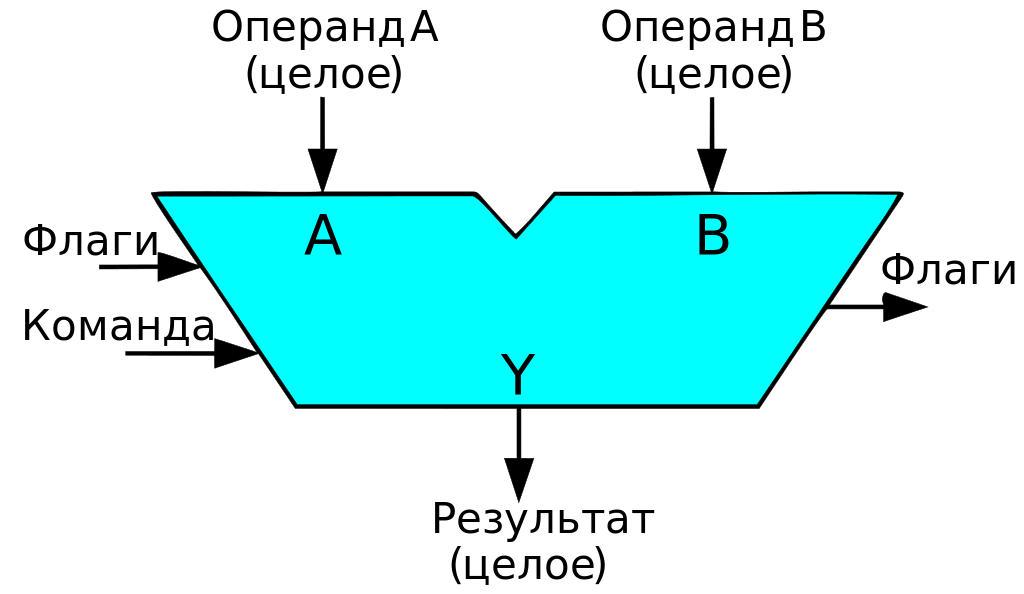

Обобщённая блок-схема арифметико-логического устройства (АЛУ).

Стрелками указаны входные и выходные слова.

Флаги — признаки (например, результата сравнения операндов) выполнения предыдущей операции (вход) и результата выполнения текущей операции (выход). В одноместных операциях таких, например, как инверсия битов слова или битовый сдвиг второй операнд (B) не участвует в операции. Слово команды указывает необходимую операцию.

По способу действия над операндами АЛУ делят на:

1.Параллельные – Операнды представляются параллельным кодом и операции совершаются одновременно над всеми разрядами операндов.

2.Последовательные – Операции над операндами производятся последовательно во времени над их отдельными разрядами.

Принцип работы:

|

|

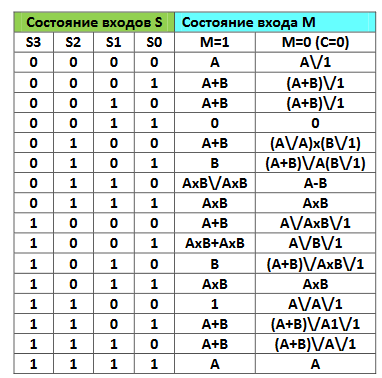

В зависимости от значений, поступающих на входы S и M, выполняется одна из 32 возможных операций. Разные операции требуют различного количества времени на свое выполнение.

Увеличение разрядности АЛУ

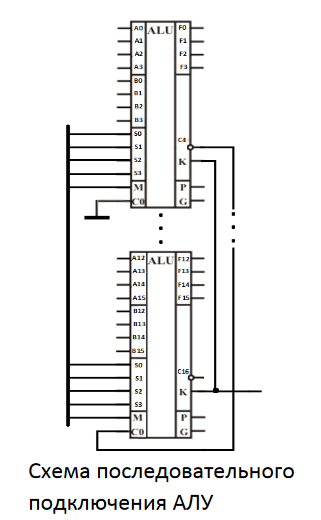

Последовательное - выход переноса предыдущей ИС соединяется со входом переноса последующей, пока не будет получена требуемая разрядность. При этом во всех АЛУ входы выбора операции и ее типа соединяются общей шиной.

При последовательном соединении АЛУ увеличивается время выполнения операции, что уменьшает быстродействие конечного устройства. Для устранения этого недостатка в АЛУ предусмотрены выходы быстрого переноса, используемые при параллельном соединении.

|

|

Увеличение разрядности АЛУ

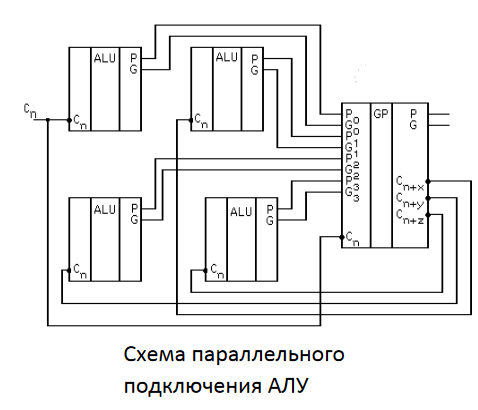

Параллельное – для этого типа подключения используются специальные микросхемы, называемые схемами ускоренного переноса. Выходы G и P АЛУ подключаем к аналогичным входам G и P схемы УП, а выходы переноса последней ко входам переноса АЛУ. При этом входы М всех микросхем должны быть объединены