- •Цели курсового проектирования

- •Тематика курсовых проектов

- •Этапы выполнения курсового проекта

- •Структура, объём и оформление проекта

- •5. Проектирование основных блоков мпу.

- •5.1. Процессорный блок.

- •Блок памяти

- •5.3. Обмен информацией в микропроцессорной системе.

- •Формирование управляющих сигналов мпс.

- •5.3.2. Интерфейсы ввода - вывода.

- •6. Пример проектирования микропроцессорного устройства.

- •6.1. Выбор микропроцессорного комплекта.

- •Разработка структурной и принципиальной электрической схем устройства.

- •Программная часть.

- •6.4. Расчёт быстродействия

- •Электротехнические чертежи и схемы. Правила выполнения схем [ 12 ]

- •Схемы цифровой вычислительной техники Общие положения

- •Принципиальные схемы

- •Программируемый параллельный интерфейс кр580вв55

- •Статические озу

- •Двоичные коды

- •Двоично-десятичные коды

- •Алфавитно-цифровые коды

- •394026, Воронеж, Московский просп. , 14

Программируемый параллельный интерфейс кр580вв55

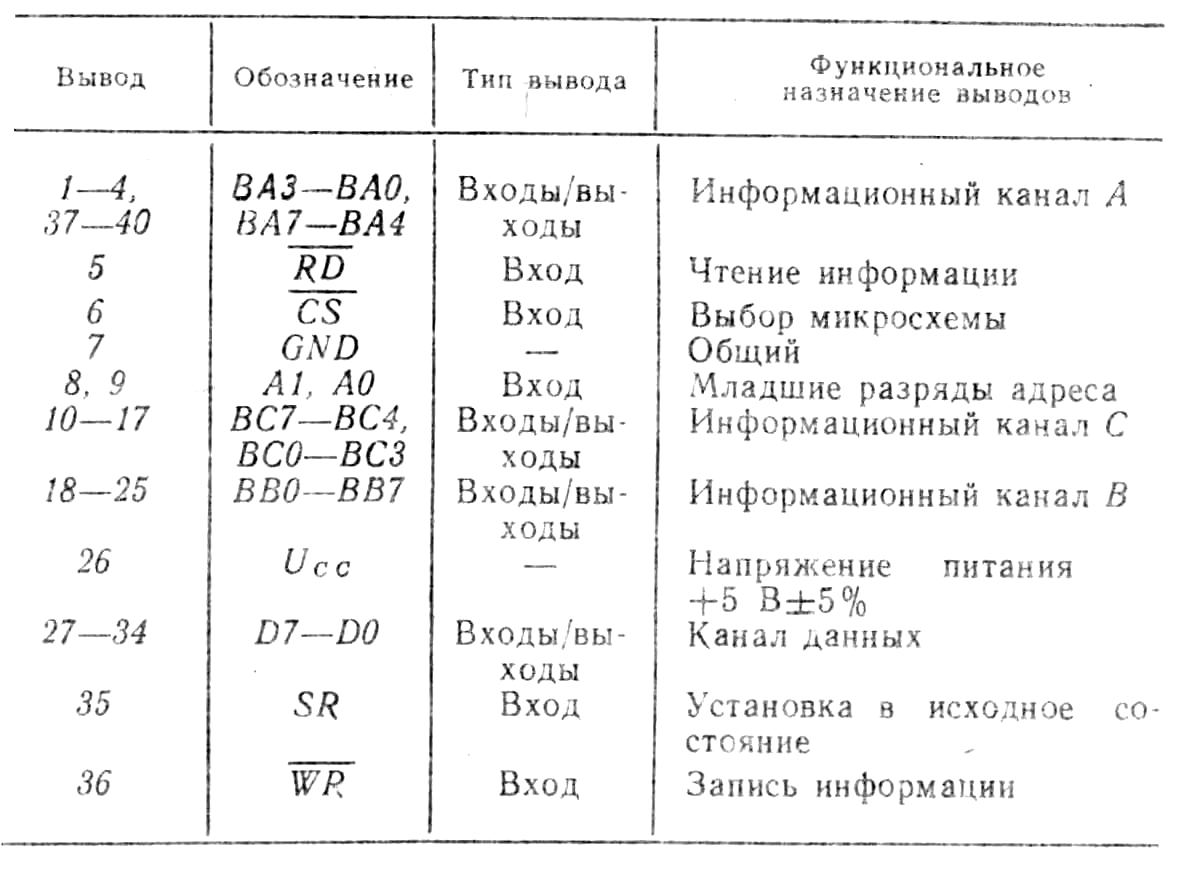

Микросхема предназначена для сопряжения устройств ввода / вывода (УВВ) с системной шиной МПС на базе МП КР580ВА80А [13]. Условное графическое обозначение приведено на рис. П4.1, назначение выводов в табл. П4.1.

О бмен

информацией между шиной данных МПС

и микросхемой ППИ осуществляется

через 8-разрядный двунаправленный

трёхстабильный канал данных (D).

Для связи с периферийными устройствами

используются три 8-разрядных канала

(порта) BA, BB,

BC, направление передачи

нформации и режимы работы которых

определяются программным способом.

бмен

информацией между шиной данных МПС

и микросхемой ППИ осуществляется

через 8-разрядный двунаправленный

трёхстабильный канал данных (D).

Для связи с периферийными устройствами

используются три 8-разрядных канала

(порта) BA, BB,

BC, направление передачи

нформации и режимы работы которых

определяются программным способом.

Управление ППИ осуществляется

сигналами: чтение / запись - стробы

чтения и записи RD и WR

(это сигналы IOR и IOW

стандартного интерфейса);

Управление ППИ осуществляется

сигналами: чтение / запись - стробы

чтения и записи RD и WR

(это сигналы IOR и IOW

стандартного интерфейса);

Рис. П4.1 сигнал сброса SR, сигнал выбора микросхемы CS,

получаемый на одной из свободных линий адреса ША,

50

выделенной для адресации данного ППИ, либо на одном из выходов дешифратора адреса;

два младших разряда А 1 и А 0 для адресации внутренних регистров.

Т аблица

П4.1

аблица

П4.1

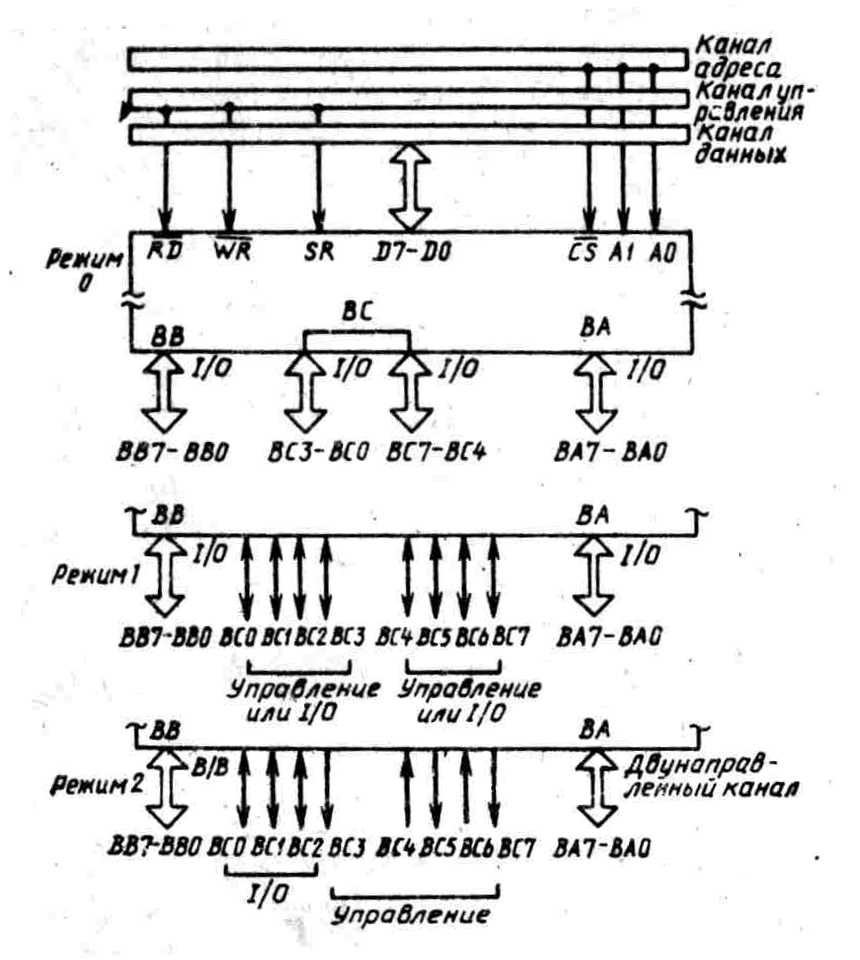

Микросхема может функционировать в трех основных режимах.

В режиме «0» обеспечивается возможность синхронной программно-управляемой передачи данных через два независимых 8-разрядных канала ВА и ВВ и два 4-разрядных канала ВС.

В режиме «1» обеспечивается возможность ввода или

вывода информации в/ или из/ периферийного устройства через два независимых 8- разрядных канала ВА и ВВ по сигналам квитирования. При этом линии канала ВС

используются для приема и выдачи сигналов управления обменом.

51

В режиме «2» обеспечивается возможность обмена информацией с периферийными устройствами через дву-

направленный 8-разрядный канал ВА по сигналам квитирования.

Порт ВС имеет особенности, в отличие от портов А и В, которые оперируют со словами в целом, разряды порта ВС могут программироваться и использоваться поодиночке. В частности, любой из восьми разрядов канала ВС может быть установлен или сброшен программным способом. Это нужно для передач сигналов квитирования при обмене через порты ВА и ВВ в режимах «1» и «2». При работе порта в режиме «1» для него требуются три линии под сигналы управления, в режиме «2» - 5. Квитирование, как известно, позволяет вести асинхронный обмен с учетом готовности абонента к передаче, т.е. иметь переменный темп обмена соответственно возможностям внешнего устройства.

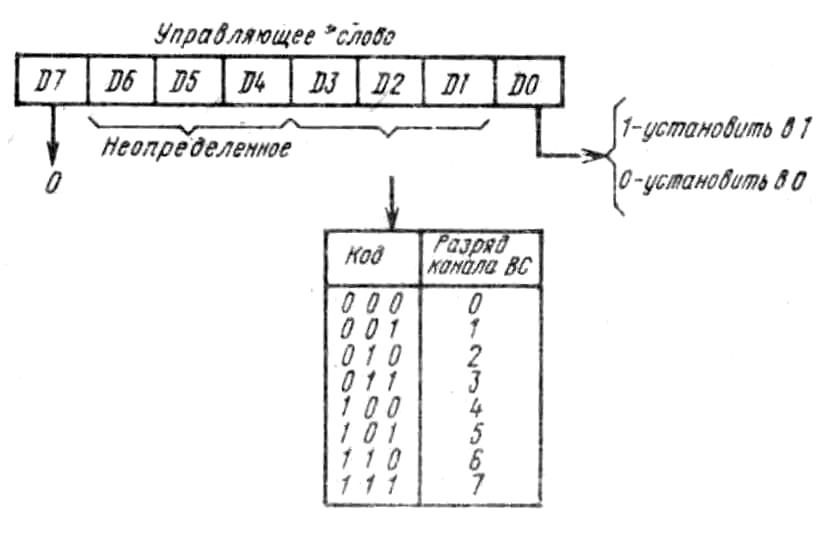

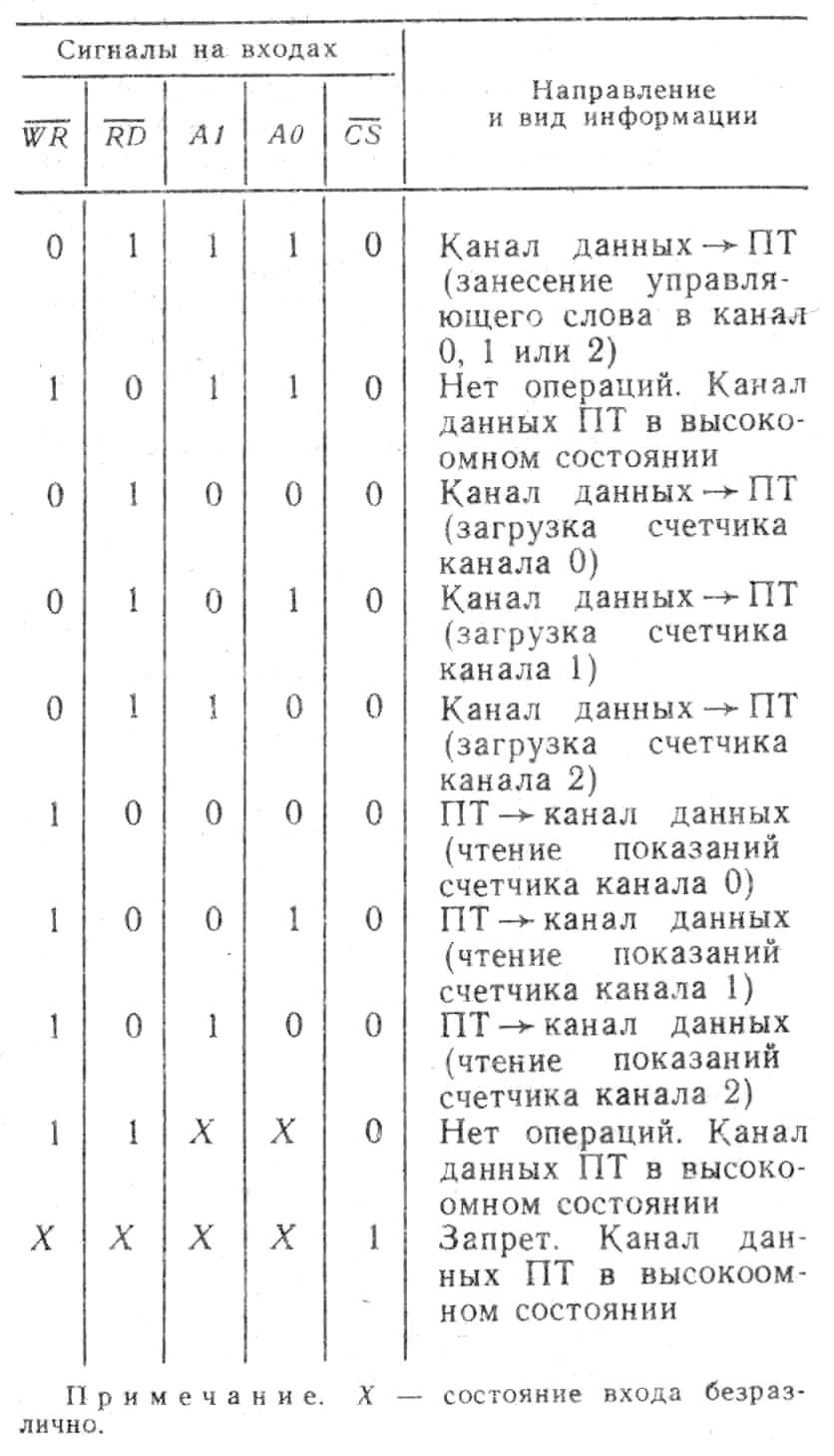

Выбор соответствующего канала и направление передачи информации через канал определяется сигналами в соответствии с табл. П4.2.

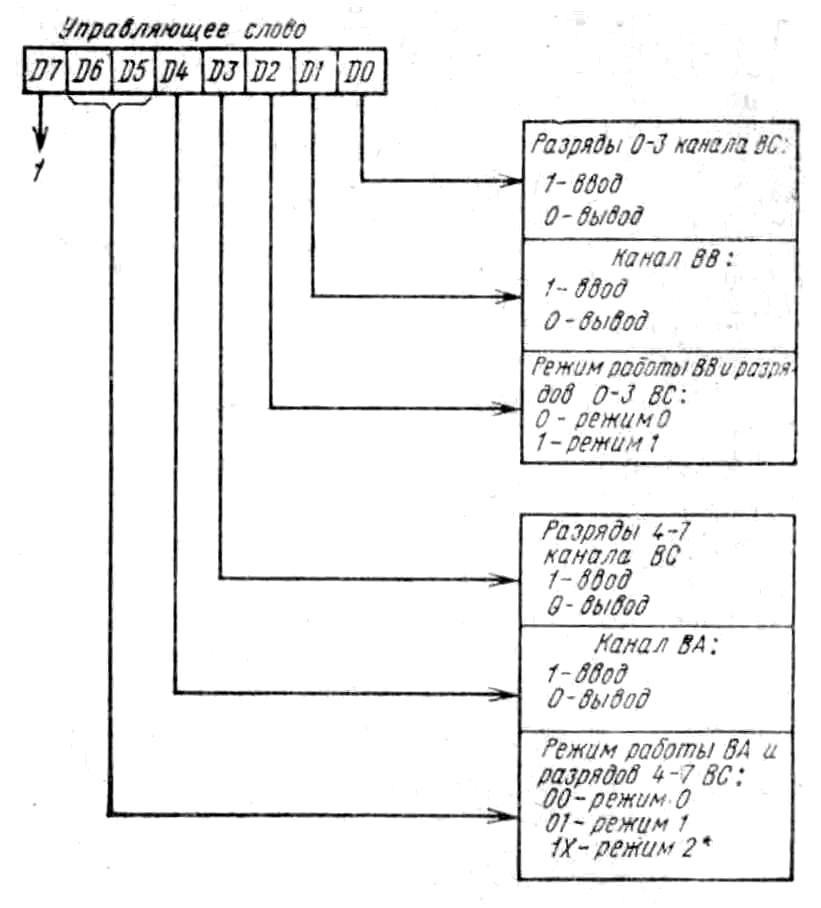

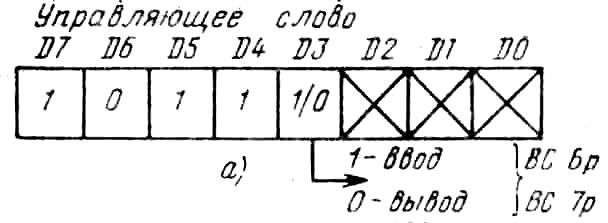

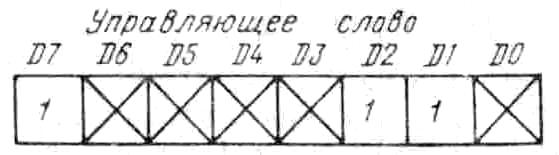

Режим работы каждого из каналов ВА, ВВ, ВС определяется содержимым регистра управляющего слова (РУС), в который заносится код управляющего слова. Графическое представление режимов работы каналов показано на рис. П4.2, а формат управляющего слова УС1, определяющего режим работы каналов приведен на рис. П4.3, а.

В дополнение к основным режимам работы микросхема обеспечивает возможность программной независимой установки в 1 и сброса в 0 любого из разрядов регистра канала ВС. Формат управляющего слова установки / сброса разрядов регистра канала ВС ( УС2) показан на рис. П4.3, в.

52

Таблица П4.2

При подаче на вход SR (СБРОС) напряжения логической «1» РУС устанавливается в состояние, при кото-

ом каналы А, В, С переходят в режим «0 для ввода ин-

53

формации, а шины каналов А, В, С переходят в высокоомное состояние.

Рис.

П4.2

Рис.

П4.2

Для записи управляющего слова в РУС используется команда вывода OUT PORT. При этом управляющее слово предварительно записывается в аккумулятор, а затем выводится в соответствующий интерфейс с указанным ад-

ресом (А1 А 0 = 11).

54

а)

б)

б)

Рис. П4.3

55

Например, для записи управляющего слова УПС (режим «0», каналы А, В, С - на вывод) в интерфейс с адресом 0111 1111 требуется следующая последовательность команд:

выборка РУС

MVI A, 1000 0000 - загрузка УПС в А;

OUT 0 1 1 1 1 1 1 1

Адрес интерфейса Выборка РУС

После этого интерфейс готов к выводу информации. Например, команда вывода через канал А

O UT 0 1 1 1 1 1 0 0

Адрес интерфейса Выборка канала А

В режиме «1» передача данных осуществляется только через каналы ВА и ВВ, а линиии канала ВС используются для приема и выдачи сигналов управления обменом (сигналов квитирования).

Форматы

управляющих слов при вводе данных

в режиме «1» показаны на рис. П4.4, а,

б для каналов ВА и ВВ соответственно.

Форматы

управляющих слов при вводе данных

в режиме «1» показаны на рис. П4.4, а,

б для каналов ВА и ВВ соответственно.

а) б)

Рис. П4.4

Форматы управляющих слов каналов ВА и ВВ при

56

выводе информации в режиме «1» показаны на рис. П4.5, а, б.

б)

б)

Рис. П4.5

Режим «2» обеспечивает двунаправленную передачу информации по каналу ВА к ВУ и обратно. Процесс обмена сопровождают пять управляющих сигналов, подаваемых по линиям ВС7 – ВС3. Оставшиеся линии ВС2 - ВС0 можно использовать для управления каналом ВВ в режиме «0» или «1». В управляющем слове для режима «2» разряд D0 определяет настройку на ввод (D0 = 1) или вывод (D = 0) интерфейсных линий ВС2 – ВС0 (рис. П4.6).

Рис. П4.6

Если микросхема запрограммирована для работы в режиме «1» или «2», то состояние каждого сигнала управления связи с внешним устройством, принимаемого и выдавемого через каналы ВС, фиксируется в регистре канала ВС. Это позволяет программисту простым чтением содер-жимого регистра канала ВС проверить состояние каждого

57

ВУ, подключенного к микросхеме, и в соответствии с состоянием ВУ изменять процесс прохождения программы.

Пример. Выполнить ввод информации о положении двухпозиционных выключателей и управление сигнальными лампочками и светодиодами с помощью КР580ВВ55 [2].

В таком случае восемь входных сигналов (К0 … К7) подключаются к одному каналу ввода (например, ВС). Аналогично к каждому выходному каналу (ВА и ВВ) подключаются по восемь линий управления лампочками и светодиодами. Работа всех каналов БИС осуществляется в режиме «0». Порты ввода и вывода микросхемы используют адреса F0H - F3H.

Определения состояния входного логического сигнала (положения выключателей) и вывод выходного сигнала осуществляется с использованием следующих программных блоков:

; программирование режима работы и направления

; передачи информации

MVI A, 89H ; управляющее слово в аккумулятор

OUT F3H ; запись в БИС управляющего слова

….

.…

; определение состояния входного сигнала

IN F2H ; ввод данных с канала ВС

ANI 04H ; выделение второго бита (назначенного)

JNZ M1 ; переход при единичном значении сигнала

….

….

; вывод сигнала

MVI A, 08H ; установка в единицу определенного бита

OUT F0H ; выдача содержимого аккумулятора в

; канал ВА

58

Приложение П5

Программируемый последовательный интерфейс связи (ППИС) КР580ВВ51

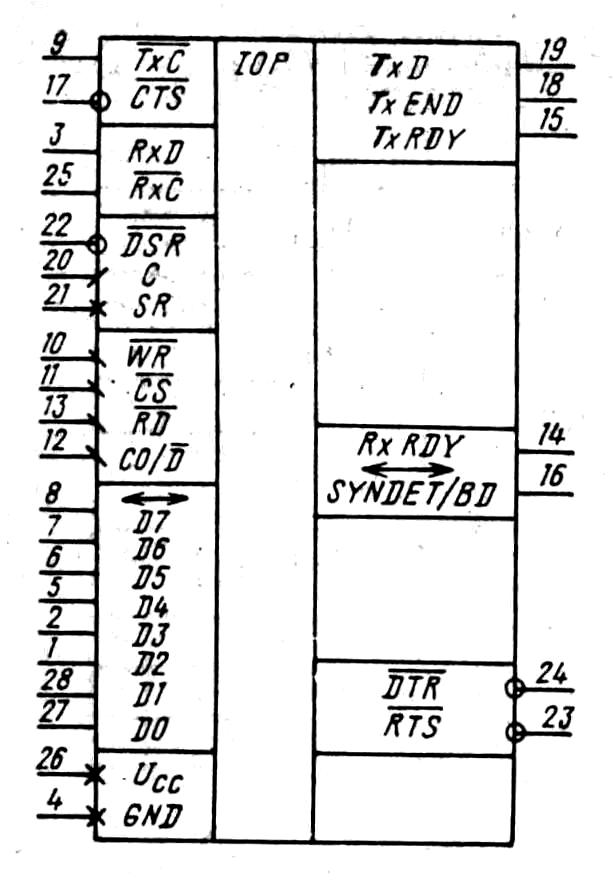

Микросхема КР580ВВ51А – универсальный синхронно-асинхронный приёмопередатчик (УСАПП) и предназначен под воздействием команд IN / OUT микропроцессора КР580ВМ80А (КМ1810ВМ86) принимать информацию, представленную последовательным кодом, преобразовывать её в параллельный код для ввода в МП, а также принимать байт данных из МП в параллельном коде с преобразованием его в последовательный код со служебными символами (стартовым, стоповым и контрольными битами) для их передачи по каналам связи с различной скоростью [5, 9, 13] .

Микросхема

ППИС программируется на выполнение

почти всех применяющихся в настоящее

время протоколов последовательной

передачи данных и работает в двух

режимах: синхронном и асинхронном.

Микросхема

ППИС программируется на выполнение

почти всех применяющихся в настоящее

время протоколов последовательной

передачи данных и работает в двух

режимах: синхронном и асинхронном.

Для управления ППИС используются два формата управляющих слов: управляю-щие слова режима (УСР) и управляющие слова команды (УСК). Условное графическое обозначение микросхемы при-ведено на рис. П5.1, назначение выводов - в табл. П5.1.

Рис. П5.1

59

Таблица П5.1

6 0

0

В озможные

варианты сочетания управляющих

сигналов и направления передачи

информации в системе приведены в

табл. П5.2.

озможные

варианты сочетания управляющих

сигналов и направления передачи

информации в системе приведены в

табл. П5.2.

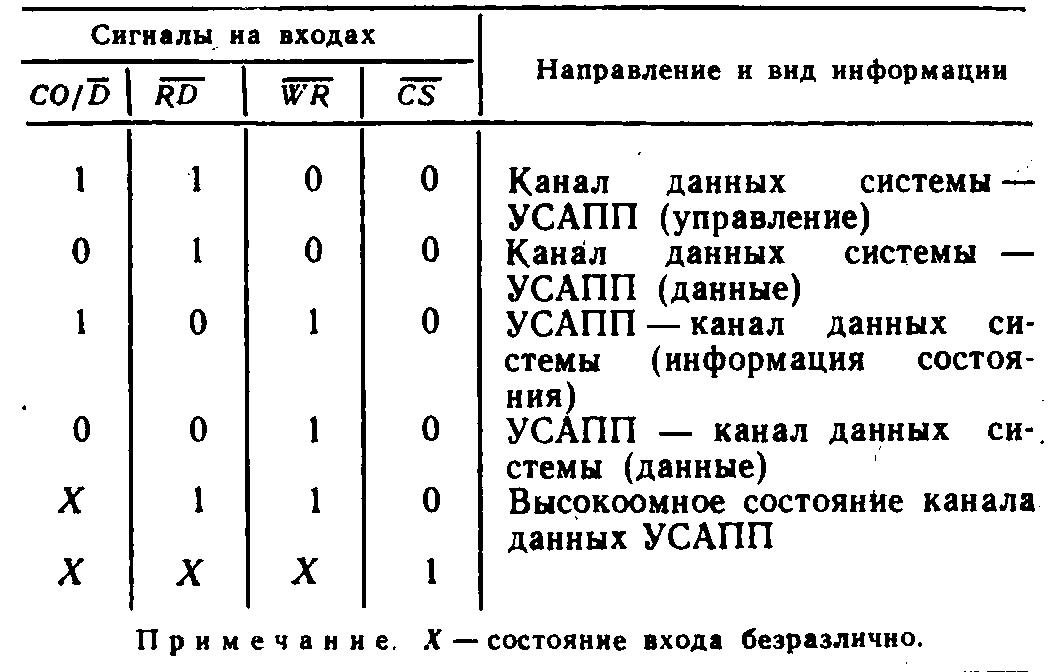

Таблица П5.2

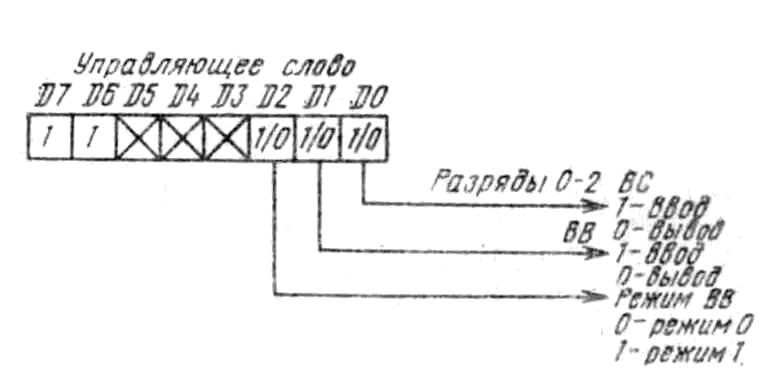

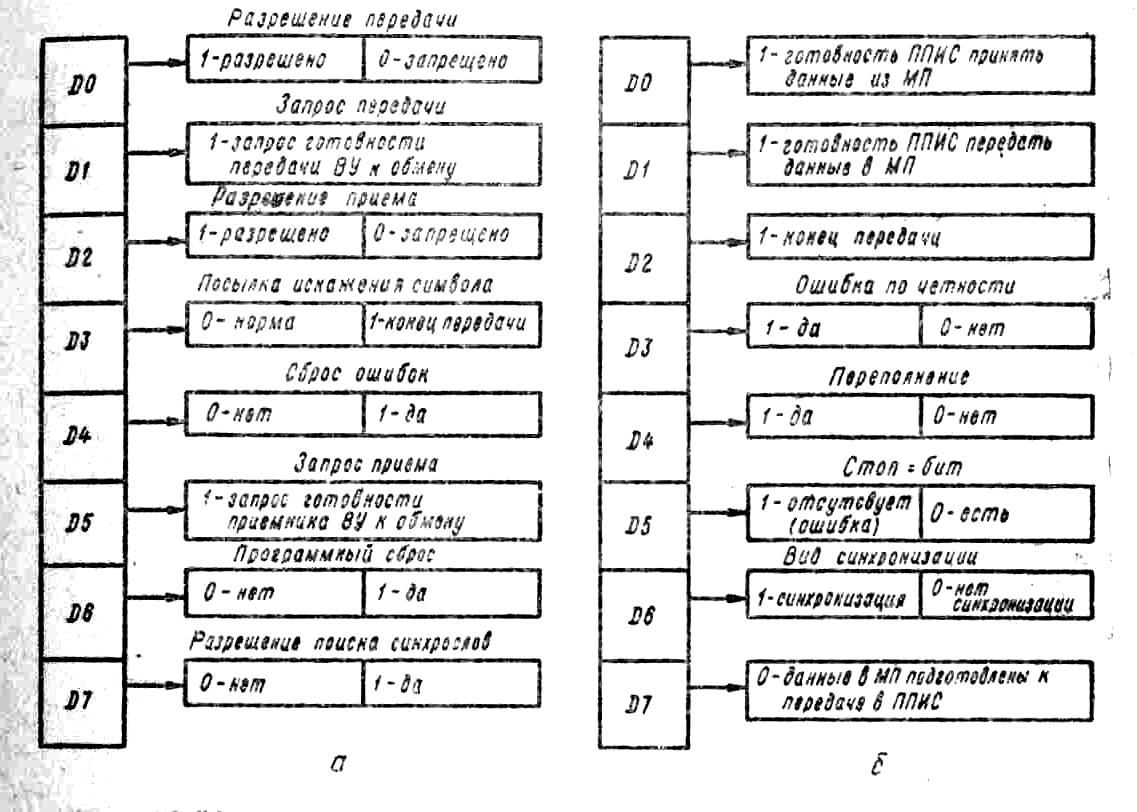

Программирование микросхемы на требуемый режим работы производится путем занесения в соответствующие регистры слов управления режимом, синхросимволов (для синхронного режима) и команд. Форматы и содержащие инструкции режима приведены на рис. П5.2, команды - на рис. П5.3.

Последовательность программирования инструкций команды, режима и синхросимволов для подготовки микросхемы к работе приведена в табл. П5.3.

Управляющие слова режима задают синхронный (рис. П5.2, а) или асинхронный (рис. П5.2, б) режимы работы, формат данных, скорость приема или передачи необходимого контроля. УСР заносится программно после установки ППИС в исходное состояние или после сигнала Сброс и заменяется лишь при смене режима. Управляющее слово команды (рис. П5.3, а) устанавливает режим

61

обмена и его можно многократно задавать в процессе обмена и управления различными этапами.

Рис. П5.2

Рис.

П5.3

Рис.

П5.3

62

Таблица П5.3

Режим приема или передачи данных программирует-

с я подачей УСР на ППИС при CO / D = 1. Последовательность программирования следующая:

MVI A, УСР ; загрузка УСР в аккумулятор

OUT ППИС ; запись УСР в ППИС

программирование режима:

MVI A, 01 11 11 01 УСР

Один Контроль Длина Асинхронный режим

стоп на четность слова скорость 1 : 1

бит 8 бит

OUT ППИС

программирование работы:

MVI A, 0 0 1 1 0 0 0 1 УСК

63

OUT ППИС

Структура программного блока, управляемого работой ППИС, имеет вид:

CS = 0 сброс сигналом r или командой

CO / D = 1 УСР

C O

/ D

= 1 синхросимвол 1 Для синхронного

O

/ D

= 1 синхросимвол 1 Для синхронного

C O / D = 1 синхросимвол 2 режима

C O / D = 1 УСК

C O / D = 0 данные

C O / D = 1 УСК

CO / D = 0 данные

Программа обмена МП и ППИС во время передачи:

XMIT: IN PORT C; чтение слова состояния (CO / D = 1)

ANI MACK1 ; выделение бита D0 (MACK1=

; 0000 0001)

JZ XMIT ; переход к чтению, если TxRDY = 0

MOV A, M ; загрузка слова данных в аккумулятор

; из ЗУ

OUT PORT D ; вывод слова данных (CO / D = 0).

Программа приема данных из ППИС при програмном обмене:

RECY: IN PORT C ; чтение слова состояния (CO / D = 1)

ANI MACK2 ; выделение бита D1 (MACK2 =

; 00000010)

JZ RECY ; переход к чтению, если RxRDY=0

ANI MACK3; анализ ошибок (MACK3=00111000)

64

CNZ ERROR; переход к подпрограмме обработки

; ошибок, если она обнаружена

IN PORT D; чтение данных (CO / D = 1).

П

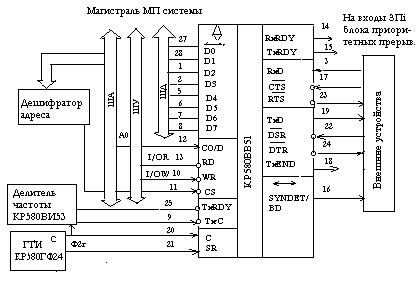

одключение

микросхемы КР580ВВ51 к магистрали МП

системы показано на рис. П5.4 [ 9 ].

Выход передатчика ( TxD

), вход приемника ( RxD

), выводы сигналов «Запрос передатчика

(приемника) терминалов» (RTS,

DTR), «Готовность

передатчика (приемника) терминалов»

(CTS, DSR)

подключаются к схеме сопряжения по

уровню преобразующей ТТЛ-уровни

входных и выходных сигналов в уровни,

необходимые для работы с ВУ (дисплеем,

накопителем на магнитной ленте и

т.д.).

одключение

микросхемы КР580ВВ51 к магистрали МП

системы показано на рис. П5.4 [ 9 ].

Выход передатчика ( TxD

), вход приемника ( RxD

), выводы сигналов «Запрос передатчика

(приемника) терминалов» (RTS,

DTR), «Готовность

передатчика (приемника) терминалов»

(CTS, DSR)

подключаются к схеме сопряжения по

уровню преобразующей ТТЛ-уровни

входных и выходных сигналов в уровни,

необходимые для работы с ВУ (дисплеем,

накопителем на магнитной ленте и

т.д.).

Рис.

П5.4

Рис.

П5.4

65

Приложение П6

Программируемый интегральный таймер (ПИТ) КР580ВИ53.

Микросхема КР580ВИ53 – трехканальное программируемое устройство (таймер), предназначено для организации работ МПС в режиме реального времени [9, 13]. Микросхема формирует сигналы с различными временными параметрами.

Программируемый таймер (ПТ) реализован в виде трех независимых 16-разрядных каналов с общей схемой управления. Каждый канал может работать в шести режимах.

Обмен информацией с микропроцессором осуществляется по 8-разрядному двунаправленному каналу данных.

Максимальное значение счета: в двоичном коде 2 16; в двоично-десятичном коде 10 4.

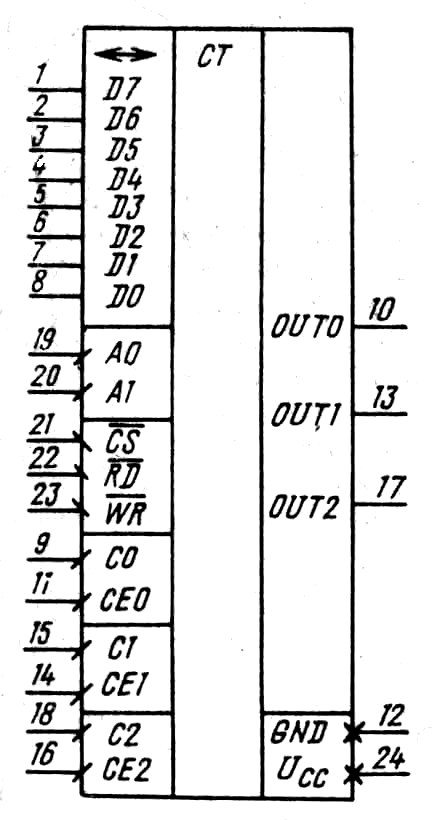

Условное графическое обозначение микросхемы приведено на рис. П6.1, назначение выводов - в табл. П6.1.

Режим работы каналов ПИТ программируется с помощью простых операций ввода / вывода (табл. П6.2).

Каждый из трех каналов ПИТ программируется индивидуально путем записи

Рис. П6.1

66

в регистр режима управляющего слова (УПС), а в счетчик - запрограммированного числа байтов.

Т ак

как микросхема не имеет аппаратного

вывода «Начальная установка», то в

ней предусмотрен внутренний программный

сброс отдельно по каналам. Сигнал

внутреннего сброса формируется при

записи управляющего слова в регистр

режима выбранного канала.

ак

как микросхема не имеет аппаратного

вывода «Начальная установка», то в

ней предусмотрен внутренний программный

сброс отдельно по каналам. Сигнал

внутреннего сброса формируется при

записи управляющего слова в регистр

режима выбранного канала.

После записи управляющего слова в регистр режима выбранного канала он переводится в один из шести режимов работы:

режим 0 - программируемая задержка;

режим 1 – ждущий мультивибратор;

режим 2 – делитель частоты;

режим 3 – генератор меандра;

Таблица П6.1

6 7

7

режим 5 – одиночный, аппаратно формируемый режим стробирующий сигнал;

4 - одиночный, программно формируемый стробирующий сигнал;

Таблица П6.2

68

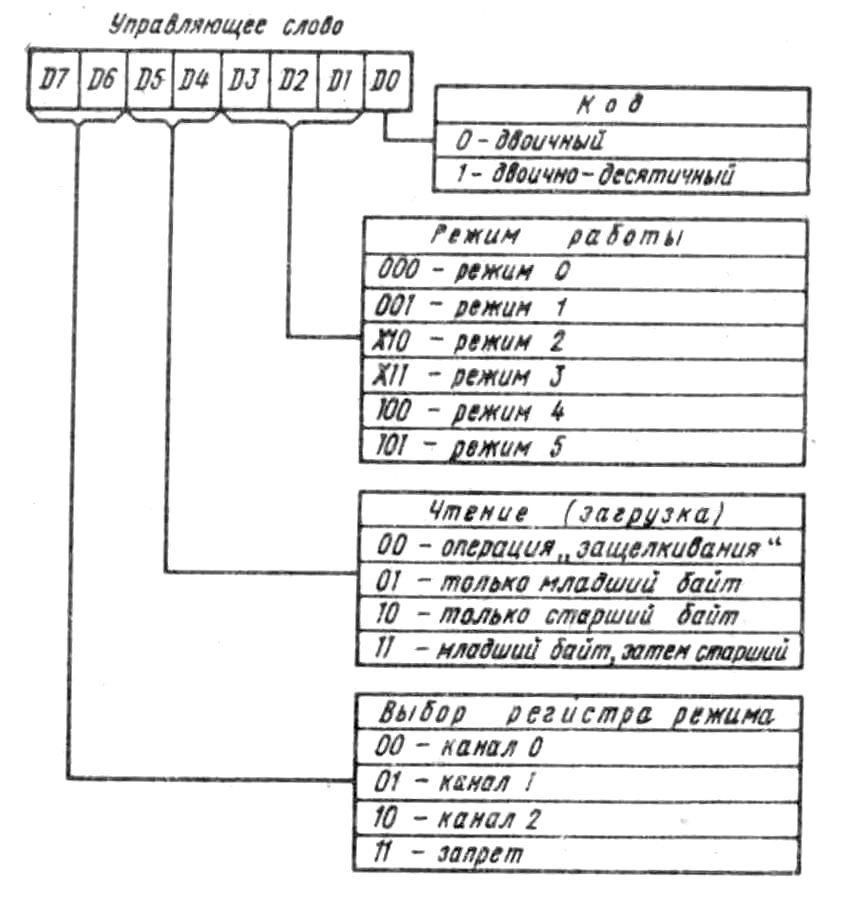

Формат управляющего слова (УПС) показан на рис. П6.2. Последовательность программирования отдельного канала следующая: УПС режима счетчика, младший байт загрузки счетчика, старший байт загрузки счетчика.

Пример программирования счетчика 0, адресуемого разрядом А4, в режиме 0 в двоичном коде:

MVI A, 0011 0000 ; формирование УПС

O UT

1110 1111 ; загрузка УПС в ПИТ

UT

1110 1111 ; загрузка УПС в ПИТ

MVI A, младший байт ; формирование и загрузка

OUT 1110 1100 ; младшего байта в счетчик 0

MVI A, старший байт ; формирование и загрузка

OUT 1110 1100; старшего байта в счетчик 0

Рис. П6.2

69

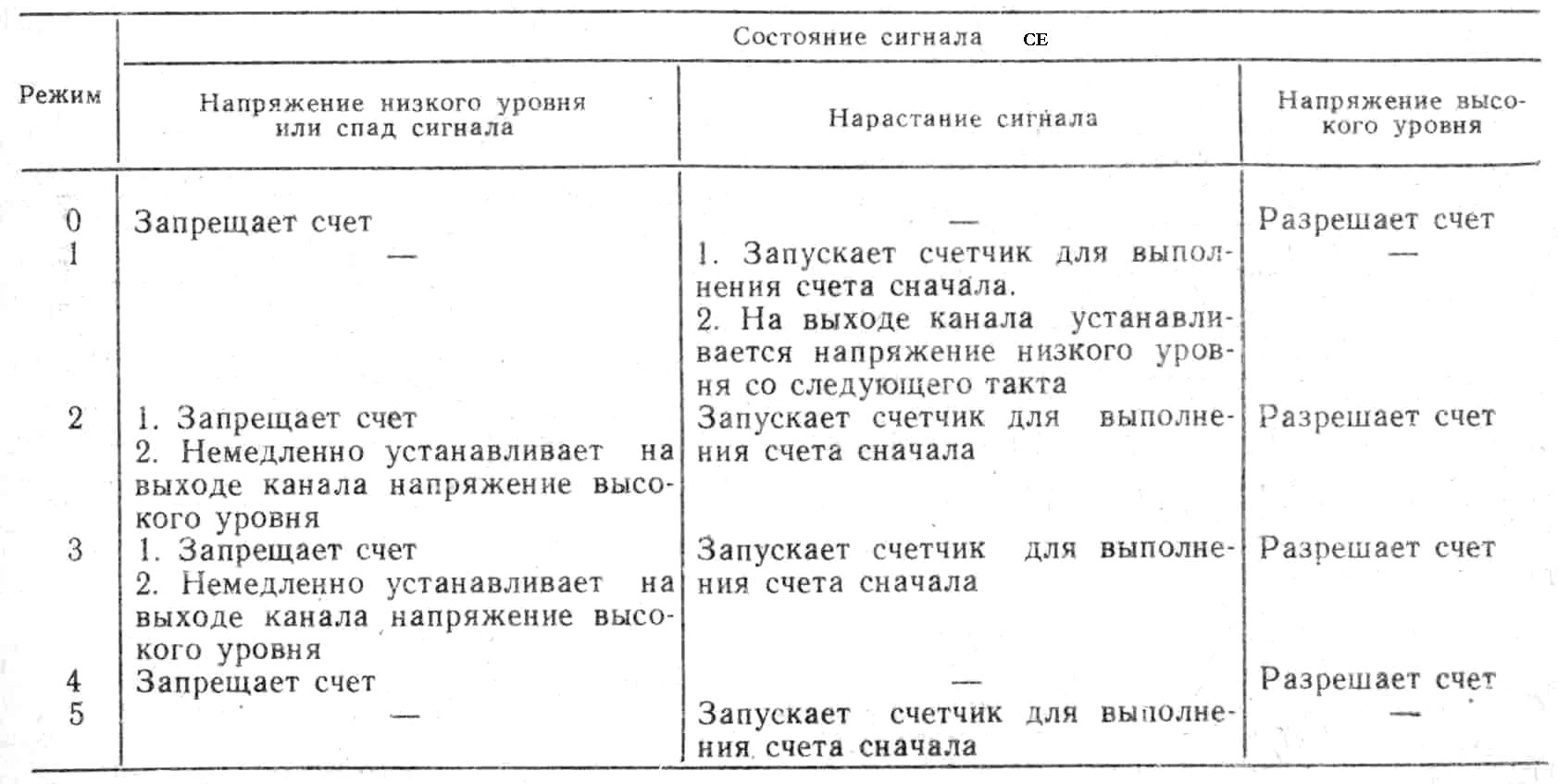

Анализ работы ПИТ в различных режимах необходимо проводить с учетом взаимодействия сигнала разрешения CE (табл. П6.3), который формируется на периферии МП системы.

В режиме 0 при подаче сигнала CE = 1 счетчик начинает работать. Перезагрузка счетчика во время счета

Таблица П6.3

приводит к следующему: загрузка младшего байта останавливает счет, а загрузка старшего байта запускает новый цикл счета. Появление сигнала СЕ = 0 в процессе счета приостанавливает работу счетчика и сохраняет текущее значение, с которого и продолжается процесс счета после восстановления разрешающего сигнала.

В режиме 1 длительность выходного импульса t вых = n 0, где 0 - период счета импульсов (СИ); n – число, загруженное в счетчик. Если во время работы в счетчик загружается новая величина n i , то это не повлияет на длительность текущей выдержки одновибратора до следующего запуска. Одновибратор является перезапускае-мым, т.е. каждый сигнал CE = 1 по переднему фронту за-

70

пускает счет или перезапускает его сначала, даже если счет не завершен до конца.

В режиме 2 счетчик делит входную частоту СИ f / n, где n - число, загруженное в счетчик. Сигнал Выход = 1 имеет длительность (n - 1) 0. Длительность выходного сигнала Выход = 0 равно периоду СИ. Перезагрузка счетчика не влияет на длительность текущего цик-

ла, но изменяет длительность следующего периода.

В режиме 3 формируются прямоугольные импульсы типа меандр (со скважностью 2). Период выходного сигнала Твых = n 0, при этом длительность положительного и отрицательного полупериодов 0 n / 2, если n четное. При нечетном n положительный полупериод 0 (n + 1) / 2, отрицательный 0 (n – 1) / 2, причем n 3.

В режиме 4 на выходе канала формируется строб логического «0» с длительностью, равной периоду 0 СИ, и программно-управляемой задержкой, длительность которой определяется числом n периодов СИ, отсчитываемых от момента появления разрешающего сигнала CE = 1.

Режим 5 аналогичен работе режима 4 с той разницей, что счетчик канала после загрузки начинает счет только по нарастанию разрешающего сигнала. Кроме того, если во время счета на входе разрешения CE появится передний фронт сигнала, то счет начинается сначала.

Один из возможных примеров записи режима

работы и загрузки счетчиков ПИТ при веден в табл. П6.4.

Режим чтения. Содержимое любого счетчика может быть считано под воздействием программы.

Это полезно в тех случаях, когда на основе считанного значения принимается решение о дальнейшем ходе вычислительного процесса. Считывать текущее значение счетчика ПИТ в МП можно двумя способами: операцией чтения или чтения «на лету». В первом способе ис-

71

Таблица П6.4

пользуется команда ввода IN. Однако, при этом на время выполнения операции считывания необходимо приостановить работу счетчика сигналом CE = 0. Кроме того, операцию чтения содержимого счетчика выбранного канала необходимо выполнить до конца, т.е. запрограммировано чтение двух байтов, то нельзя читать только один байт. Второй способ считывания содержимого счетчика без прерывания счета (чтение «на лету» ) требует предварительной загрузки в регистр режима УПС с кодом 1000 XXXX. Однако, особенностью этого способа чтения является невозможность предварительной записи УПС по каналам: УПС выдается МП непосредственно перед чтением.

Пример. Последовательность чтения содержимого счетчика 1, адресуемого разрядом А4, имеет вид:

72

MVI A, 1000 0000; формирование УПС чтения «на лету» OUT 1110 1111; запись УПС в ПИТ IN 1110 1100; чтение младшего байта счетчика

IN 1110 1100; чтение старшего байта счетчика

На рис. П6.3 изображена схема сопряжения ПИТ КР580ВИ53 с магистралью МП системы.

Рис. П6.3

73

Приложение П7

Микросхемы памяти

По функциональному назначению микросхемы памяти подразделяют на 2 вида: ОЗУ и ПЗУ. Микросхемы ОЗУ по типу элемента памяти разделяют на статические

и динамические. В микросхемах статических ОЗУ в качестве элементов памяти (ЭП) применены статические триггеры. В микросхемах динамических ОЗУ элементы памяти выполнены на основе электрических конденсаторов. Такие ЭП нуждаются в периодическом восстановлении (регенерации).

Микросхемы ПЗУ, масочные (ПЗУМ) и программируемые пользователем (ППЗУ), допускают однократное программирование. Один из вариантов реализации ПЗУ ориентирован на программирование заданных логических функций, Такие ПЗУ называют логическими матрицами (ПЛМ).

Существует разновидность микросхем ПЗУ, допус-

кающая неоднократное (сотни и тысячи циклов) перепрограммирование, называются репрограммируемые ПЗУ (РПЗУ). Для стирания информации перед новым циклом программирования необходимо удалить заряды в ЭП. В зависимости от способа выполнения этой операции микросхемы РПЗУ разделяют на два вида: со стиранием электрическим сигналом (РПЗУ-ЭС) и ультрафиолетовым светом (РПЗУ-УФ).

В таблице П7.1 приведены типы и основные характеристики специальных серий микросхем ЗУ, которые нашли применение в МПС различного назначения.

74

Таблица П7.1

Тип микросхем

|

Техно-логия |

Емкость. (организа-ция), бит

|

Время выборки адреса, нс |

Ток потреле-ния, мА |

Номер рисунка |