Министерство цифрового развития, связи и массовых коммуникаций Российской Федерации

Ордена Трудового Красного Знамени федеральное государственное бюджетное образовательное учреждение высшего образования

МОСКОВСКИЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ СВЯЗИ И ИНФОРМАТИКИ

(МТУСИ)

Факультет "Радио и телевидение"

Кафедра "Радиотехнические системы"

Лабораторная работа № 4

по дисциплине микропроцессорные устройства

Выполнил студент гр. БРМ1902: А.В. Ванин

Проверил Д.Н.Шубин

Москва 2022

Цель работы

Целью работы является ознакомление с внешним видом проекта, создан-ным полностью на языке описания аппаратуры VHDL.

Выполнение

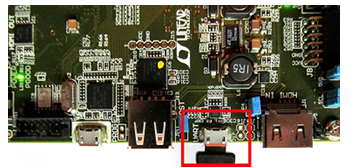

Отладочная плата Atlys Spartan-6 оснащена интерфейсом универсального асинхронного приемопередатчика (UART), порт которого обозначен как J17.

Рисунок 1 - Порт UARTна плате Atlys Spartan-6

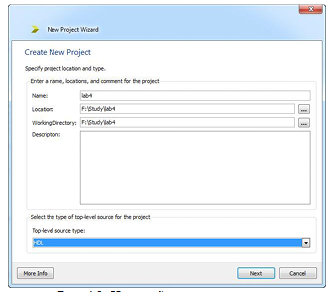

Создание проекта

Рисунок 2 - Настройки нового проекта

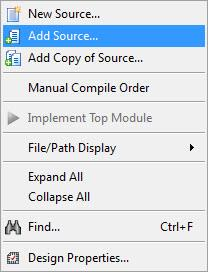

Добавление и изменение источников vhdl

Рисунок 3 - Добавление готовых файлов-источников

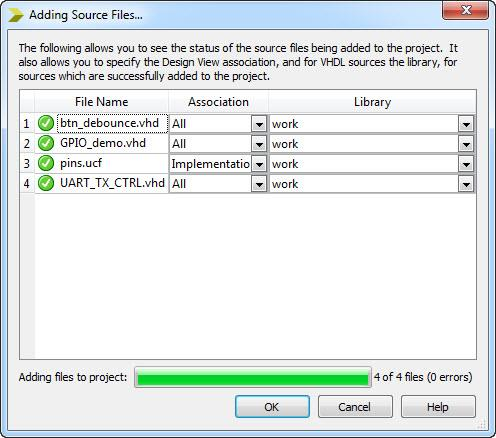

Рисунок 4 - Окно мастера импорта файлов в проект

Рисунок 5 - Иерархия проекта

Вывод информации на компьютер

После конфигурирования платы не отключая питаниянужно вытащить кабель«плата-компьютер» из разъема PROG и подключить к разъему UART.

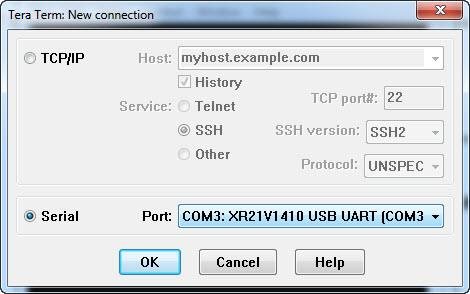

После подключения к разъему UART нужно запустить терминал Tera Term

В настройках подключения выбрать Serial и порт, отвечающий за под-ключенную плату.

Рисунок 6 - Настройки терминала Tera Term

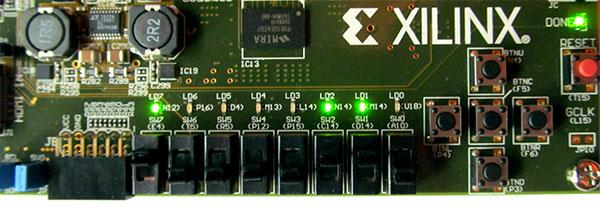

Все приготовления готовы, выбрав какую-либо комбинацию переключа-телей (зажгутся соответствующие светодиоды)

Рисунок 7 - Пример комбинации переключателей

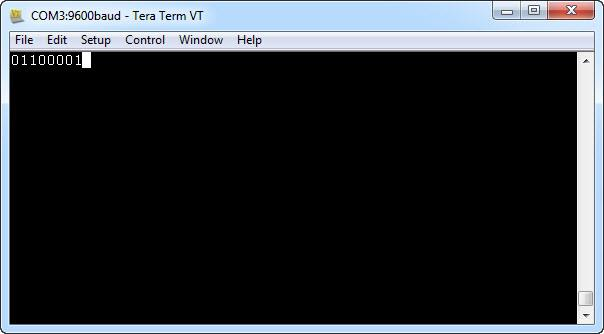

И после, нажав центральную кнопку в терминале должно высветиться следующее.

Рисунок 8 - Вывод информации в Tera Term

Это значит, что всё работает так, как и планировалось.

Контрольные вопросы

1. Какие функции выполняет порт последовательной передачи данных?

При последовательной передаче сокращается количество сигнальных линий, что упрощает разводку проводников на печатной плате, уменьшает габариты устройства и позволяет делать более помехозащищен-ные интерфейсы. При последовательной передаче каждый информационный бит должен сопровождаться импульсом синхронизации — стробом.

2. Опишите работу периферийного устройства UART. Пояснения сделайте с помощью временных диаграмм.

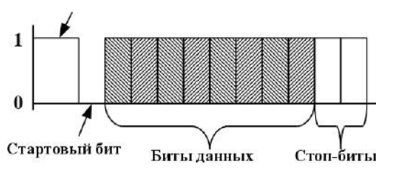

Когда передача данных не ведется - на линии выставлен уровень лог. 1. В начале передачи каждого байта всегда передается стартовый бит, всегда имеющий значение лог. 0. С учетом того, что линия до этого находилась в состоянии лог. 1, то признаком начала передачи является переход линии из состояния лог. 1 в состояние лог.О. Стартовый бит служит для обозначения начала передачи очередного байта данных. После приема стартового бита происходит прием битов данных (обычно используются 8-битные байты). После передачи всех битов данных передается один или несколько стоп-битов. Стоп-биты всегда имеют значение лог. 1 и служат для того, чтобы обеспечить наличие признака начала передачи при приеме следующего байта данных.

Временные диаграммы передачи данных по интерфейсу UART

3. Что такое пользовательский тип данных в VHDL? Как он объявляется?

VHDL – это строго типизированный язык. Это означает, что все про-граммные элементы данных (константа, переменная, сигнал) должны явно объявляться с обязательным указанием типа элемента. Кроме того, не допускаются операции над разнотипными элементами без предварительного преобразования типов.

В языке VHDL из ключевых, зарезервированных слов и других лексических элементов строятся образования, которые принято называть операторами. Оператор, в языке VHDL, начинается с ключевого слова и заканчивается символом точки с запятой (;).

В языке VHDL операторы с точки зрения их функционального программ-ного назначения принято делить на две основные группы:

· Операторы объявления программных элементов данных и их типов, компонентов проектируемого ЦУ, их интерфейсов и архитектур, пользовательских типов, а также функций и процедур.

· Выполняемые операторы.

В языке VHDL объявление делится на 2 части: интерфейс и архитектура.

entity...is

end entity...;

architecture...is

end architecture...;

В объявлении интерфейса (entity) содержится объявление портов проектируемого компонента с внешним миром. Объявление портов проектируемого компонента определяет внешние входные и выходные интерфейсные сигналы. Архитектура представляет собой набор таких взаимосвязанных программных элементов, как подчиненные компоненты, операторы, операторы параллельных вычислений, последовательные операторы, подпрограммы.

4. В какой код преобразуются данные, принятые UART?

UART означает универсальный асинхронный приемник-передатчик. Это периферийное оборудование, которое находится внутри микроконтроллера.

Функция UART заключается в преобразовании входящих и исходящих данных в последовательный двоичный поток.

5. Опишите назначение основных элементов отладочного набора для ПЛИС Xilinx Spartan.

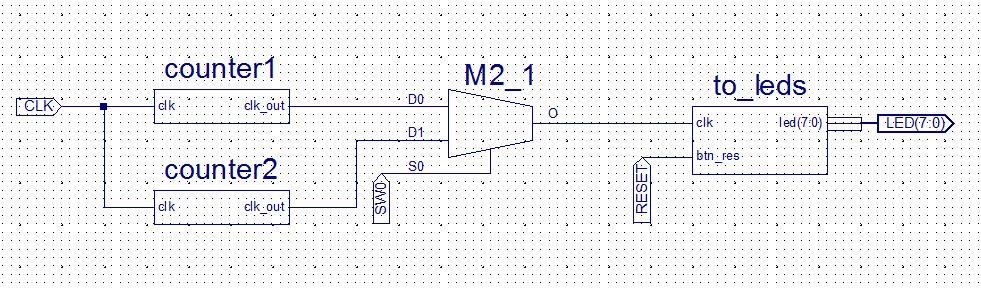

Модули counter1 и counter2 понижают скорость внутреннего счетчика с разной скоростью. ·

Мультиплексор M2_1 в зависимости от положения переключате-ля SW0 выбирает, какая скорость счетчика будет использоваться.

Модуль to_leds выполняет функцию бинарного счетчика, кото-рый выводит своё состояние на 8 светодиодов и при нажатии кнопки RESET на следующем такте обнуляет счетчик.

6. Для чего в языке VHDL используются библиотеки?

VHDL-библиотека (library) — место, где компилятор VHDL хранит информацию об отдельном варианте проекта, включая промежуточные файлы, используемые при анализе, моделировании и синтезе в рамках данной разработки.

7. В листинге файла GPIO_demo.vhd укажите декларацию компонентов проекта. Какие функции выполняют эти компоненты?

Все изменения должны касаться только файла верхнего уровня GPIO_demo.vhd, именно там содержится алгоритм работы. (Файл UART_TX_CTRL.vhd содержит описание работы интерфейса UART; файл btn_debounce.vhd отвечает за исправления явления дребезга контактов для кнопок и файл pins.ucf отвечает за связь с контактами отладочной платы)

8. Правильно ли, что компоненты, декларируемые в архитектурном теле, должны специфицироваться полностью (т.е. вместе с интерфейсом и выполняемыми функциями)? Поясните на примере программы, приведенной в Приложении 3.1.

Да. В entity и декларируемом компоненте должны совпадать спецификациии. Компонент является частью проекта. Его реализация осуществляется соответствующим entity и одним или несколькими архитектурными телами.

Тело архитектурного описания специфицируемого объекта, заключенное между begin и end, содержит совокупность параллельных операторов, иначе говоря операторов, выполняющихся параллельно друг с другом.

Локальные объекты

entity to_leds is

Port ( clk : in STD_LOGIC;

btn_res : in STD_LOGIC;

led : out STD_LOGIC_VECTOR (7 downto 0));

end to_leds;

Архетектурное тело

architecture Behavioral of to_leds is

begin

process(clk, btn_res)

variable cnt: STD_LOGIC_VECTOR (7 downto 0) := "00000000";

begin

if clk'event and clk = '1' then

if cnt = (cnt'range => '1') or btn_res = '0' then

cnt := "00000000";

else

cnt := cnt + 1;

end if;

led <= cnt;

end if;

end process;

end Behavioral;

В понятие спецификация можно отнести и тот факт, что VHDL – это строго типизированный язык. Это означает, что все про-граммные элементы данных (константа, переменная, сигнал) должны явно объявляться с обязательным указанием типа элемента. Кроме того, не допускаются операции над разнотипными элементами без предварительного преобразования типов.

9. Сколько архитектурных тел может быть связано с одним entity? Поясните на примере программы, приведенной в Приложении 3.1.

Тело объекта специфицирует его структуру или поведение. Его описание по терминологии VHDL содержится в описании его архитектуры architecture.

VHDL позволяет отождествлять с одним и тем же интерфейсом несколько архитектур. Это связано с тем, что в процессе проектирования происходит проработка архитектуры объекта: переход от структурной схемы к электрической принципиальной, от поведенческого к структурному описанию.

entity to_leds is

Port ( clk : in STD_LOGIC;

btn_res : in STD_LOGIC;

led : out STD_LOGIC_VECTOR (7 downto 0));

end to_leds;

architecture Behavioral of to_leds is

В данном примере с одним entity связано одно архитектурное тело.

10. Разрешается ли специфицировать начальное значение порта?

Да. В начальном значении порта и в архитектурном теле программы должны совпадать спецификации. Начальное значении порта является частью проекта. Реализация архитектурного тела осуществляется соответствующим начальным значением порта.

11. Поясните назначение каждого из блоков и особенности их реализаций.

Модули counter1 и counter2 понижают скорость внутреннего счетчика с разной скоростью. ·

Так как внутренний счетчик отладочной платы имеет частоту 100 МГц, то для вывода информации на светодиоды и для комфортного визуального вос-приятия нужно понизить частоту.

Мультиплексор M2_1 в зависимости от положения переключателя SW0 выбирает, какая скорость счетчика будет использоваться.

При реализации в ПЛИС мультиплексор можно синтезировать применительно к конкретной задаче, в соответствии с которой выбираются разрядность адреса, количество информационных входов и количество входов разрешения.

Модуль to_leds выполняет функцию бинарного счетчика, который выводит своё состояние на 8 светодиодов и при нажатии кнопки RESET на следующем такте обнуляет счетчик.

В настройках портов важна галочка элемента led и представленные значения. Таким образом, элемент led будет 8-битной шиной, каждый бит которой будет привя-зан к соответствующему светодиоду. Такой способ упрощает обращения со всеми светодиодами и делает код чище и приятнее для чтения и понимания.

12. В какой части VHDL-кода должны быть декларированы локальные сигналы архитектурного тела? Поясните на примере программы, при-веденной в Приложении 3.1.

В списке портов архитектурного тела

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity counter1 is

Port ( clk : in STD_LOGIC;

clk_out : out STD_LOGIC); end counter1;

architecture Behavioral of counter1 is – архитектурное тело

Сигнал, декларированный в пакете, является видимым во всех объектах проекта, которые употребляют ссылку (use) на данный пакет. Сигнал, декларированный в entity как порт, является видимым во всех архитектурных телах, связанных с данным entity. Сигнал, декларированный в разделе деклараций архитектурного тела, видим только внутри данного архитектурного тела.

13. С помощью фрагмента программы, приведенной в Приложении 3.1, поясните работу интерфейса UART.

Файл UART_TX_CTRL.vhd содержит описание работы интерфейса UART

Периферийное устройство UART – это полнодуплексный Универсальный Асинхронный Приемник/Передатчик (Universal Asynchronous Receiver/Transmitter – UART), совместимый с промышленным стандартом 16450. UART преобразует данные между последовательным и параллельным форматами. Последовательная передача (прием) выполняется по асинхрон-ному протоколу, который допускает изменение длины слова данных, различ-ное число стоп-бит, формирование сигнала четности. UART также может включать аппаратные средства модемного управления и обработки прерываний.

Строки STR0 и STR1заполнены символами «пробела» X"20" (Так как UART принимает данные в виде 8 бит и интерпретирует их в виде ASCII ко-да, то и значения, которыми мы оперируем, представляют соответственно ASCII код).

begin

if (rising_edge(CLK)) then

if (uartState = LD_INIT_STR) then

ind := 0;

while ind < 8 loop

if SW(ind) = '0' then

STR0(ind):=

std_logic_vector(to_unsigned(character'pos('0'), 8));

elsif SW(ind) = '1' then

STR0(ind):=

std_logic_vector(to_unsigned(character'pos('1'), 8));

end if;

ind := ind + 1;

end loop;

sendStr <= STR0;

strEnd <= 8;

led : out STD_LOGIC_VECTOR (7 downto 0));

14. С помощью фрагмента программы, приведенной в Приложении 3.1, поясните работу устройства, выполняющего функцию избавления от дребезга контактов.

Файл btn_debounce.vhd отвечает за исправления явления дребезга контактов для кнопок

btn_reg_process : process (CLK)

begin if (rising_edge(CLK)) then

btnReg <= btnDeBnc(3 downto 0);

end if;

end process;

Этот процесс btn_reg_process выполняет функцию избавления от дребезга контактов (иными словами выполняет файл btn_debounce.vhd).

Переключающая кнопка. Она выполняет функцию сброса.

btn_res : in STD_LOGIC;

Модули counter1 и counter2 понижают скорость внутреннего счетчика с разной скоростью.

Мультиплексор M2_1 в зависимости от положения переключателя SW0 выбирает, какая скорость счетчика будет использоваться.

Модуль to_leds выполняет функцию бинарного счетчика, который выводит своё состояние на 8 светодиодов и при нажатии кнопки RESET на следующем такте обнуляет счетчик.