Sbornik_PLIS

.pdfФЕДЕРАЛЬНОЕ АГЕНТСТВО СВЯЗИ

Федеральное государственное образовательное бюджетное учреждение

высшего профессионального образования

Московский технический университет связи и информатики

Кафедра радиотехнических систем

Сборник лабораторных работ по дисциплине

ЦИФРОВЫЕ УСТРОЙСТВА И МИКРОПРОЦЕССОРЫ

Москва 2015

План УМД на 2014/2015 уч.г.

Сборник лабораторных работ по дисциплине

ЦИФРОВЫЕ УСТРОЙСТВА

И МИКРОПРОЦЕССОРЫ

Составители:

Минаева О.Н., старший преподаватель, Мозжухин Г.Н., инженер, Косичкина Т.П., доцент

Утверждено советом факультета РиТ. Протокол № * от 16.10.2014 г.

Рецензент В.С. Сперанский, к.т.н., профессор

2

ЛАБОРАТОРНАЯ РАБОТА №1

1. Цель работы.

Целью работы является ознакомление с системой автоматизированного проектирования (САПР) Xilinx ISE Web Pack на примере менеджера проектов Project Navigator и реализация простейшей логической схемы на ПЛИС с использование функционала графического редактора.

2.Задания для выполнения лабораторной работы

2.1Предварительная подготовка к выполнению лабораторной работы

1.Изучить описание к данной лабораторной работе и рекомендованную литературу.

2.Ознакомиться с основами комбинаторной логики и правилами составления схем по логическим уравнениям.

3.Выполнить домашний расчет: по заданной таблице истинности составить логическое выражение и упростить его (см. Методические указания к данной лабораторной работе). На основе полученного логического выражения составить логическую схему в базисе, указанном преподавателем. Данные для выполнения расчета содержатся в Таблице 1.1. Номер варианта назначается преподавателем.

4.Подготовить ответы на контрольные вопросы, приведенные в данном описании лабораторной работы.

5.Подготовить письменный отчет принятой на кафедре формы. Отчет должен содержать:

-титульный лист принятой на кафедре формы;

-номера лабораторной работы, варианта работы и формулировку цели работы;

-исходные данные выполняемого варианта;

-домашний расчет;

-результат выполнения работы;

-краткие выводы по работе.

2.2Выполнение исследований в лаборатории

Разделы выполнения лабораторной работы:

2.2.1.Создание проекта

2.2.2.Проектирование цифрового устройства в графическом редакторе

2.2.3.Создание связи с выводами отладочной платы

2.2.4.Создание конфигурационного файла

2.2.5.Конфигурирование отладочной платы

2.2.1 Создание проекта

После запуска Project Navigator двойным кликом по иконке

3

или

появляется главное окно программы (Рис. 1.1)

Рис. 1.1. Главное окно программы Project Navigator

Для того чтобы создать новый проект, нужно нажать кнопку «New Project…» в приветственном окне программы, или через контекстное меню

File – New Project…

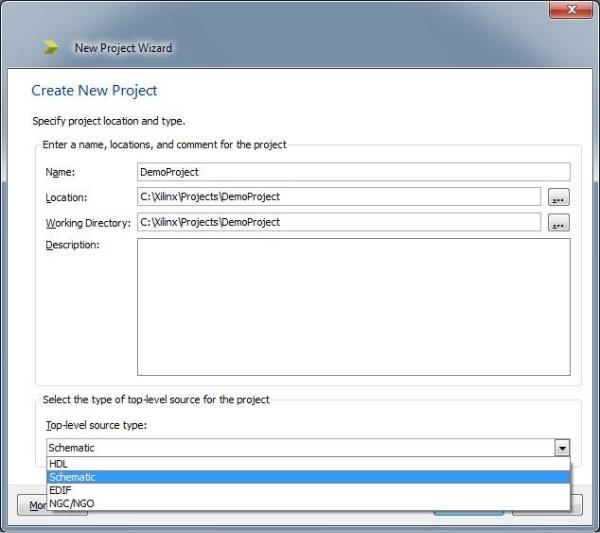

Откроется мастер создания нового проекта «New Project Wizard» (Рис. 1.2)

4

Рис. 1.2. Мастер создания нового проекта

В данном окне нужно задать следующие параметры:

Name: название проекта, которое автоматически задает расположение проекта в файловой системе и рабочую директорию.

Top-level source type: файл-источник высшего уровня. Именно этот тип будет считаться главным в проекте, и на его основе будет проходить создание проекта.

В данной, и всех последующих работах форма представления файла верхнего уровня проекта будет схематическая (Schematic).

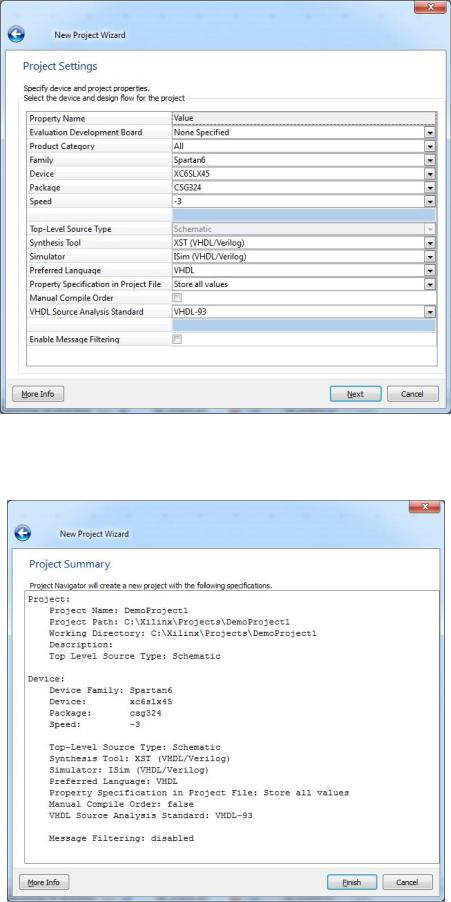

Следующее окно представляет собой выбор устройства и сопутствующих настроек для компиляции и симуляции проекта. В данном окне ничего менять не нужно, оно должно соответствовать рис. 1.3, в котором уже заданы все нужные параметры для корректной работы программы на отладочной плате Atlys Spartan-6.

5

Рис. 1.3. Настройки проекта

После нажатия кнопки «Далее» («Next») будет показана суммарная информация по проекту (Рис. 1.4).

Рис. 1.4. Суммарная информация проекта

6

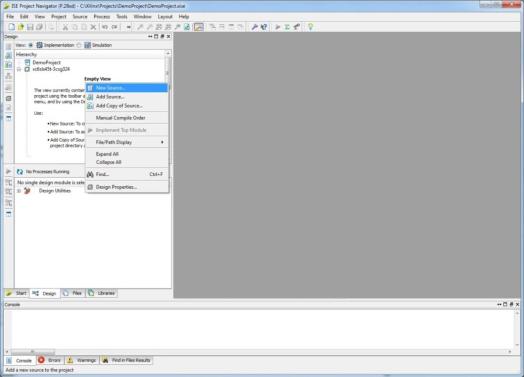

По завершению работы мастера создания нового проекта, в левой часте главного окна программы (Панель проекта) появится пустая заготовка текущего проета.

2.2.2. Проектирование цифрового устройства в графическом редакторе

Теперь нужно добавить в этот проект источники. Сначала создадим новый файл схематического представления (который и будет файлом верхнего уровня проекта).

Для этого нужно нажать правой кнопкой в свободной областе «Hierarchy» и выбрать «New Source» (Рис. 1.5).

Рис. 1.5. Добавление нового источника в проект

Откроется мастер создания нового источника («New Source Wizard») (Рис. 1.6.), в котором нужно будет выбрать тип источника (Shematic) и дать ему имя. Имя файла верхнего уровня также будет и у итогового скомпилированного файла.

После завершения работы мастера создания нового источника, автоматически откроется редактор нового источника в главной рабочей области. В данном случае откроется графический редактор схем (Рис. 1.7) (Если этого не случилось, открыть редактор файла можно с помощью двойного клика на названии файла вкладки Design) .

7

Рис. 1.6. Создание нового источника

Рис. 1.7. Редактирование файла-схемы

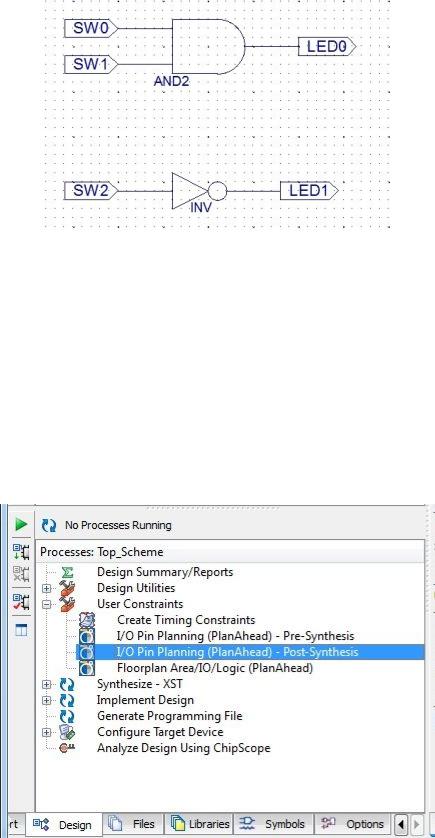

Следующим шагом в разработке проекта с использование схематического редактора нужно добавить элементы в рабочую область. Для простого ознакомления создадим схему, которая будет использовать 3 переключателя SW и 2 светодиода LED. Они будут выполнять следующую логику:

SW0 и SW1 при одновременном включении зажгут светодиод LED0

SW2 выводит на светодиод LED1 инверсию своего состояния

Нам потребуются логические элементы AND2 («И» на 2 входа) и INV (Инверсия) из стандартной библиотеки компонентов редактора.

8

Рис. 1.8. Вкладка элементной базы Symbols

Для добавления этих элементов в проект нужно выбрать соответствующее название из элементной базы вкладки Symbols (Рис. 1.8) и кликнуть в рабочей области открытой схемы. Элементы AND2 и INV находятся в категории

Logic.

После этих манипуляций схема должна иметь как на Рис. 1.9

Рис. 1.9. Схема с элементами AND2 и INV

Так как в данном проекте входы и выходы логических элементов являются основными выводами, которые и нужно связать с платой (входы SW, выходы LED), то нужно выставить маркеры, которые далее будут привязываться к отладочной плате.

Для этого на панели редактирования схемы нужно нажать на икон-

ку Add I/O Marker

И кликнуть на входы и выходы логических элементов. Автоматически создадутся маркеры, как представлено на Рис. 1.10.

Рис. 1.10. Добавление маркеров

9

Для удобства в последующем привязывании маркеров, их стоит переименовать. Для этого нужно нажать правой кнопкой на маркере и выбрать Rename Net, убедиться, что выбрано Rename the Branch’s Net и ввести имя маркера, как представлено на рисунке 1.11:

Рис. 1.11. Переименованные маркеры

Основная работа по созданию схемы выполнена.

2.2.3. Создание связи с выводами отладочной платы

Следующий важный шаг – связать созданную схему с выводами на отладочной плате.

Для связывания маркеров с выводами платы служит специальный тип файлов – Implementation Constraints File. Создать его можно двумя способами. Графический способ будет рассмотрен в этой лабораторной работе, а альтернативный способ в следующей работе.

Для создания Implementation Constraints File в графическом режиме нужно в окне процессов (левый нижний блок) выбрать процесс I/O Pin Planning (Plan Ahead) – Post-Synthesis и дважды кликнуть на него (Рис. 1.12).

Рис. 1.12. Процесс для создания Implementation Constraints File

10