- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

- •Вычислительные комбинационные устройства

Вычислительные комбинационные устройства

•Вычислительные комбинационные устройства (ВКУ) предназначены для выполнения арифметических действий с двоичными числами: сложения, вычитания, умножения и деления. Такие цифровые устройства называют также арифметическими.

•К ВКУ относятся также устройства, выполняющие специальные арифметические операции – выявление четности или нечетности заданных чисел и их сравнение.

•Особенность ВКУ состоит в том, что сигналам приписываются не логические, а арифметические значения 1 и 0 и действия над ними подчиняется законам двоичной арифметики. Хотя ВКУ оперируют с численными величинами, для описания их работы также удобно пользоваться таблицами истинности.

•ВКУ широко используются в ЭВМ и достаточно часто в аппаратуре информационно- измерительной техники. ВКУ выпускаются в виде готовых изделий в составе многих серий цифровых микросхем.

•Сумматоры – арифметические устройства, осуществляющие сложение n-разрядных двоичных чисел. Многоразрядные сумматоры строятся на основе одноразрядных сумматоров.

•Одноразрядные сумматоры производят сложение двух одноразрядных двоичных чисел. Разновидности одноразрядных сумматоров:

oсумматор по модулю 2;

oполусумматор;

oполный сумматор.

Вычислительные комбинационные устройства

•Сумматор по модулю 2 (исключающее ИЛИ, XOR, mod2, ) выполняет сложение по правилам: 0 + 0 = 0; 0 + 1 = 1; 1 + 0 = 1;

1 + 1 = 0, при этом возникает единица переноса в следующий разряд.

•Сумма описывается логической функцией неравнозначности.

a |

b |

S |

СДНФ: S = *b + a*= a b |

|

0 |

0 |

0 |

||

|

||||

0 |

1 |

1 |

|

|

1 |

0 |

1 |

|

|

1 |

1 |

0 |

|

Полусумматор также |

A |

B |

P |

S |

СДНФ: |

производит суммирование |

0 |

0 |

0 |

0 |

|

двух одноразрядных двоичных |

|

||||

0 |

1 |

0 |

1 |

|

|

чисел, но вырабатывает также |

|

||||

и единицу переноса в старший |

1 |

0 |

0 |

1 |

|

разряд. |

1 |

1 |

1 |

0 |

|

|

|

Вычислительные комбинационные устройства

•Полный сумматор – суммирует два одноразрядные двоичные числа с добавлением единицы переноса из младшего разряда, и вырабатывает единицу переноса в старший разряд.

Ai |

Bi |

Pi-1 |

Pi |

Si |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

0 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Первый полусумматор служит для сложения двух чисел, принадлежащих одному разряду, и обеспечивает выход промежуточной суммы Si и переноса Pi’ . Второй полусумматор складывает перенос предыдущего разряда Pi -1 с промежуточной суммой Si . Перенос Pi для данного разряда получается как логическая сумма переносов для первого и второго полусумматоров.

Вычислительные комбинационные устройства

•Многоразрядные сумматоры. Суммирование многоразрядных чисел может быть последовательное или параллельное.

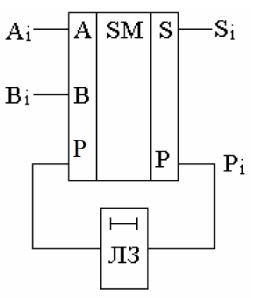

•В многоразрядных последовательных сумматорах используется один, общий для всех разрядов, полный сумматор с дополнительной цепью задержки.

Оба слагаемых кодируются последовательностями импульсов, которые синхронно вводятся в сумматор через входы А и В, начиная с младших разрядов. Цепь задержки ЛЗ обеспечивает хранение импульса переноса Pi на время одного такта, то есть до прихода пары слагаемых следующего разряда, с которыми он будет просуммирован. Задержку обеспечивает D-триггер (триггер задержки). Для хранения и ввода слагаемых А и В, а также для преобразования последовательного кода выходных импульсов в параллельный применяют регистры сдвига.

Достоинство последовательных сумматоров - малые аппаратурные затраты. Недостаток – невысокое быстродействие, поскольку одновременно суммируется лишь один разряд, а время выполнения операции пропорционально числу разрядов слагаемых и периоду поступления новых данных на входы сумматора: Tc = n*To.

В многоразрядных параллельных сумматорах используется n полных сумматоров, на которых производится одновременное суммирование всех двоичных разрядов чисел А и В. При этом по способу организации переноса Pi параллельные сумматоры подразделяются на:

•сумматоры с последовательным переносом;

•сумматоры с параллельным переносом;

•сумматоры с групповым переносом.

Вычислительные комбинационные устройства

•Параллельный сумматор с последовательным переносом.

•Число сумматоров в схеме равно числу разрядов.

•Выход переноса каждого сумматора соединен со входом переноса сумматора более старшего разряда. На входе переноса сумматора первого разряда установлен потенциал U0 (логического нуля), поскольку сигнал переноса сюда не поступает.

•Слагаемые Ai и Bi складываются во всех разрядах одновременно, а перенос поступает с окончанием операции сложения в предыдущем разряде.

Быстродействие многоразрядных сумматоров подобного вида ограничено задержкой переноса, так как появление сигнала переноса на выходе старшего разряда не может произойти до тех пор, пока сигнал переноса младшего разряда не распространяется последовательно по всей системе:

tпер = n * tсм1,

где tпер – время распространения переноса по n разрядам; tсм1 – время задержки суммирования в одном полном сумматоре.

В микросхеме К555 ИМ6 четыре полных одноразрядных сумматора объединены в схему четырехразрядного сумматора. Сумматор с последовательным переносом.

Вычислительные комбинационные устройства

•Параллельный сумматор с параллельным переносом.

•Чтобы уменьшить время выполнения операции сложения многоразрядных чисел, используют схемы параллельного переноса. При этом сигналы переноса во всех разрядах одновременно вычисляются по значениям входных переменных в данном разряде и во всех младших.

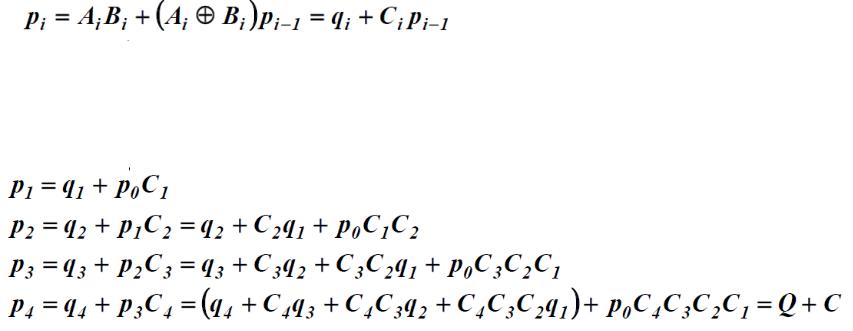

•Для сигнала переноса из любого i-го разряда справедливо соотношение

где qi -функция генерации переноса,

Сi -функция распространения переноса.

Пользуясь этм рекуррентным соотношением, можно вывести следующие формулы для вычисления сигналов переноса в четырехразрядном сумматоре:

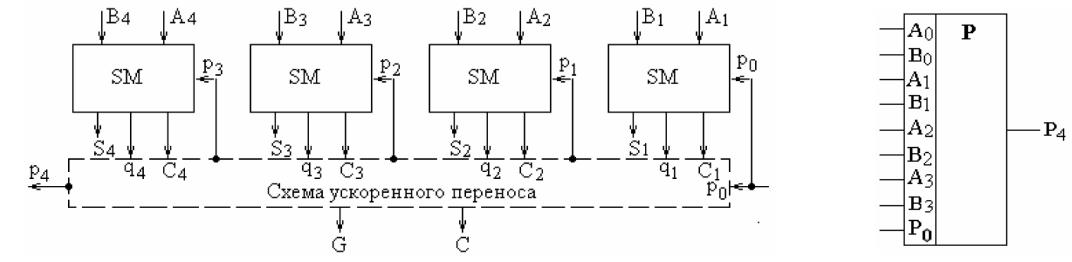

Реализацию этих функций выполняет схема ускоренного переноса

Вычислительные комбинационные устройства

•Хотя полученные логические выражения достаточно сложны, время формирования сигнала переноса в любой разряд с помощью вспомогательных функций определяется временем задержки распространения сигнала в двух элементах. 4-разрядная микросхема КМОП 564ИП4.

•Параллельный сумматор с групповым переносом.

•При большом числе разрядов сумматора применяется групповой перенос. Образование суммы в каждом разряде внутри группы происходит при последовательном переносе, а перенос в следующую группу снимается не с сумматора старшего разряда, а с выхода схемы параллельного переноса. Этот сигнал переноса P4 подается на один из входов такой же схемы следующей группы, а также на вход сумматора младшего разряда в этой группе.

•Для построения 16-разрядного сумматора используется эта же схема ускоренного переноса.

Вычислительные комбинационные устройства

Схема вычитателя A − B

•Group propagate (PG) — групповой сигнал распространения переноса.

•Group generate (GG) — групповой сигнал генерации переноса.

•Сумматор – основной компонент любого арифметико-логического устройства микропроцессора. С помощью сумматора реализуются все арифметические операции над двоичными числами – сложение, вычитание (в дополнительном коде), умножение (сложение со сдвигом) и деление (вычитание со сдвигом). Дополнительный код: обратный (инверторы) + 1 (+Uп на вход переноса PI).

Вычислительные комбинационные устройства

•Цифровые компараторы – ВКУ, предназначенные для сравнения двух чисел, заданных в двоичном коде. Цифровые компараторы также относятся к арифметическим устройствам, как и сумматоры.

•Цифровые компараторы, предназначенные для сравнения двух n-разрядных чисел А и В, имеют 2n входов и 3 выхода: FA>B , FA=B и FA<B . Условное графическое изображение компаратора и схема компаратора для сравнения одноразрядных чисел А и В представлены на рисунке.

Схема представляет собой развернутую логическую структуру элемента "Исключающее ИЛИ-НЕ" с тремя выходами. Из определения операции Исключающее ИЛИ (неравнозначность, сумма по модулю 2) вытекает, что функции FА=В , FА>B , FA<B равны:

, ,

Вычислительные комбинационные устройства

•Синтезируем компаратор для сравнения двух двухразрядных чисел

•А = а1а0 и В = b1b0 . Очевидно, A > B, если а1 > b1 , или

а0 > b0 при а1 = b1 . Аналогично, A < B , если а1 < b1 или

а0 < b0 при а1 = b1 .

•Если же а1 = b1 и а0 = b0 , то А = В.

•Можно составить таблицу истинности для функций FA>B , FA=B , FA<B и произвести их минимизацию с помощью карт Карно. Получим:

С повышением разрядности сравниваемых чисел сложность схемы резко возрастает. Цифровые компараторы выполняются в виде отдельных ИМС. Так, ИМС K56I ИП2 сравнивает два четырехразрядных двоичных числа и имеет три выхода FA>B , FA=B , FA<B .

Одноименные входы служат для наращивания разрядности сравниваемых двоичных чисел.